星载高速数字电路电源芯片选型及电源完整性设计

2020-08-12滕树鹏李森郭黎烨彭飞叶曦

滕树鹏 李森 郭黎烨 彭飞 叶曦

(上海航天电子技术研究所/八院智能计算技术重点实验室,上海,201109)

星载数字电路的高速化设计对电源完整性设计提出更高的需求,恰当的电源芯片选择有利于信号完整性设计优化。在星载高速数字电路中,随着信号传输速度的增加、芯片性能的增强,相应地对供电提出以下要求:更低的电压、更大的电流、需平滑更大的开关噪声、低功耗。常用的电源芯片包括开关式点电源芯片和LDO(低压差线型稳压器)型电源芯片。开关式点电源芯片具有高效率、输出电流大的优点,但同时也具有响应速度相对较低、开关噪声大等劣势。LDO型电源芯片本身特性导致其输入输出电压压差越大、输出电流越大,功耗越高,但其又具有响应速度快,纹波小等优点。因此在星载高速数字电路设计中对电源响应要求极高的位置,如:DDR(双倍数率动态随机存储器)的VTT(终端电压)供电,或工作电流极小 (一般压差小于3V电流小于1A)等位置一般优选采用LDO型电源芯片;其他供电需求中开关式点电源芯片更为适用。本文将对分别对开关式点电源芯片 (以LTM4644为例)及LDO型电源芯片在宇航产品中设计中的电源完整性设计进行分析。

1 开关式点电源芯片

1.1 功能与特性

在电源芯片选型过程中,考虑到宇航用电子类产品需要适应空间环境的高辐射、真空环境散热差、需长时间工作及无法维修的特点。宇航用开关式点电源应具备以下功能及特性。

a)具有输出过压保护、输出过流保护、短路保护等功能,并且在进入保护模式后重新上电后可恢复正常工作。过压保护及过流保护功能为常用电源芯片功能,均为保护后端电路设计,在供电后端器件异常情况下保护星上主电源不受影响。短路保护功能要求响应短路保护时间小于10μs。在空间环境中,后端电子类集成电路 (含MOS电路)可能受单粒子闩锁影响,导致集成电路中的MOS电路电源对地短路,电源芯片应能够及时响应短路保护功能,避免单粒子闩锁导致的短路引起的部分电路烧毁,重新上电后单粒子闩锁状态可解除。

b)电源芯片在工作输出电流范围内,效率高、热耗少。空间真空环境中散热条件较差,电源芯片本身为电子产品中的较大热源,而通常单机内的温度监控点设置在非热源位置,这样当电源芯片热量累计过大时,若相应电源不能紧急关断,可能对电源芯片造成不可恢复的硬件损伤。因此电源芯片在工作电流范围应具有高效率特性,以提高产品的热可靠性设计。

c)电源芯片额定电流与产品需求应具备1倍以上余量。额定电流应高于理论最大电流1倍以上是宇航产品的降额设计需求。考虑电子产品在上电瞬间浪涌一般高于额定工作电流1.5倍,因此电源芯片额定电流应具备1倍以上余量。

d)电源芯片可进行软启动配置。在后端芯片时序准许范围内,延长软启动时间可以有效降低上电瞬间的浪涌电流。一般情况下影响电子类产品寿命的关键因素为电路中的电容寿命,而电容寿命与电容的负载电压及充放电能量成反比,因此降低上电浪涌可以有效延长产品寿命。

1.2 开关式点电源电路设计

LTM4644为Linear Technology公司生产的4路输出DCDC电源芯片,单路输出电流4A,具备过压保护、过流保护、短路保护及高温保护特性。在电路的原理图设计中应注意:输入电容设计、输出电容设计、软启动设计、输出电压设计及时序设计。其中输入电容、时序设计及输出电压依托系统设计,参考系统内主要芯片及系统功能需求,此处不做详细介绍。

1.2.1 输出电容设计

在开关式点电源电路设计中,电源芯片输出电容的主要功能为,降低开关电源的开关噪声以及为后端负载储能。在电源开关噪声过大情况下,一般芯片若核电压超过±5%、接口电压超过±10%则会导致芯片工作异常,甚至完全不能启动;若后端负载电路电流较大,并且为突发负载,则电容储能不足可能导致输出电压瞬时降低或抖动,因此设计大容值储能电容应预留足够余量,但过多过大的储能电容又会占用较多PCB(印制电路板)布局资源。输出电容设计均需根据实际情况分析,不同负载、不同需求甚至不同的PCB layout(印制板布局布线)都可能导致同一电源芯片的电路设计不一致,一般均需通过测试对原设计进行优化。

但在输出电容的设计过程中通常有一些设计方法可以参考,以尽可能满足使用需求。

a)一次电与二次电的压降,若压差过大,输出电容需增大容值。

b)针对输出负载工作的频点,选择相应的滤波电容。通常大容值电容滤低频干扰,小容值电容滤高频干扰。通常采用的初始设计方式为大容值加小容值并联,具体容值可参考芯片数据手册,预留足够调试电容位置。

c)尽量选用低ESR(寄生电阻)电容,且电容不要串联。开关电源的滤波电容通过电容充放电及电容两端电压不可突变的特性实现输出电源的开关噪声过滤。若ESR过大则导致电容两端电压存在突变,会产生新的噪声源。

d)输出电容耐压值尽量不小于电源的输入电压且高于输出电压的2倍。

1.2.2 软启动设计

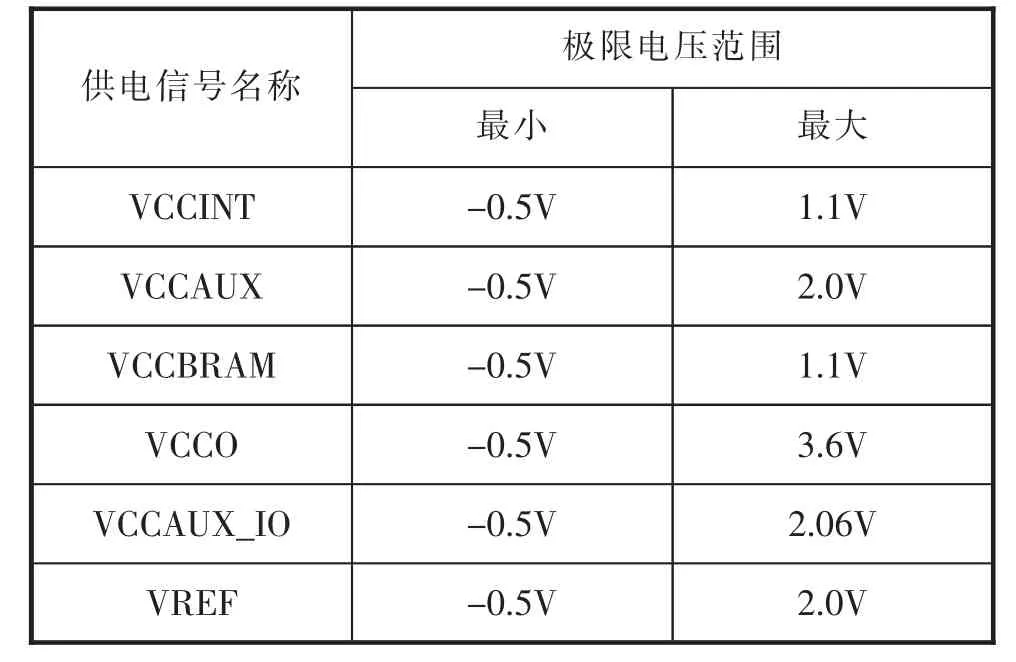

电源芯片的软启动一般根据芯片手册提供的公式计算,LTM4644的软启动时间计算公式如下:

公式 (1)中,tSS为软启动时长,单位为s;U=0.6V;CSS为软启动配置电容,单位为μF;I=2.5μA。一般tSS应在满足后端供电芯片时序需求的基础上尽量延长,降低负载端及一次电源端的启动浪涌。

1.3 测试和调试

在开关式点电源的设计中,对完成的电路进行测试、调试是必不可少的一步,可以在测试中针对电源完整性需求,采用上面提到的优化措施对电路进行验证及优化。

1.3.1 电源完整性测试

分别为空载、满载及动态负载情况下,针对输入电压在±10%波动情况下电源电路在常温、高温及低温条件下输出电压情况进行测试,测试结果若后端负载无特殊要求情况下一般输出电压波动范围不应该大于额定电压的±10%。

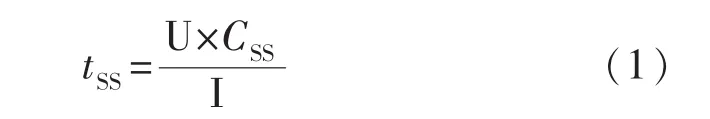

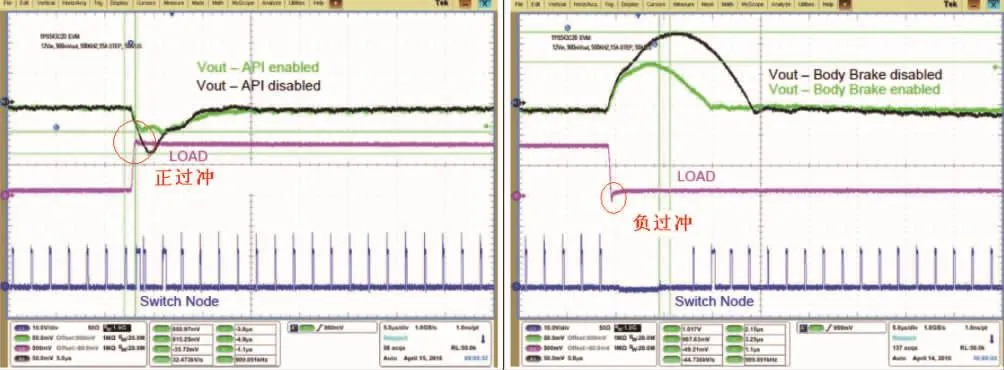

1.3.2 电源可靠性测试

电源可靠性测试主要为验证芯片的可靠性,一般在芯片选型确认后无法更改,但此项测试可以作为整个产品设计的可靠性的量化指标。一般测试项目主要为输出过流保护点、短路保护点、短路保护恢复性、正向过冲及负向过冲。其中正负过冲为电源在启动及关闭中发生的瞬时的输出电压超过设定电压及小于0,冲测试波形如图1所示。主要考虑部分芯片有供电电压极限值,若超过指定电压可能损伤芯片, Xilinx公司的Kintex-7系列芯片提出的供电电压极限值范围见表1。

图1 正负过冲测试波形

表1 Xilinx公司的Kintex-7系列芯片提出的供电电压极限值范围

测试中应遵循以下原则:①测试用示波器带宽不应过高,一般应小于1GHz;②接口电压的测试中示波器带宽选择应为100MHz,内核电压的测试中示波器带宽选择应为20MHz;③探头测测试点应该选择在输出电容的小容值电容两端。

1.4 PCB设计

PCB设计也是开关式点电源的电源完整性设计需要注意的重要部分。在PCB设计中应注意以下关键点。

a)输入电容的排列应该按照大容值电容远离电源芯片输入引脚,小容值电容靠近电源芯片引脚的顺序进行排列,即电流依次流经大电容及小电容再输入芯片。

b)输出电容的排列应该按照小容值电容远离电源芯片输出引脚,大容值电容靠近电源芯片引脚的顺序进行排列,即电流依次输出芯片流经大电容及小电容。

c)FB(电压反馈)信号走线应该尽量短,并且做加宽处理。同时在FB信号走线附近严禁走高速、高频信号。FB走线一般不换层、不走内层,必要时采用两次换层。

d)输入电容参考地、输出电容参考地及电源芯片参考地应该连在一起并且通过足够数量及孔径的过孔与本PCB地平面短接,各个地之间的走线禁止走细线。

e)电源输入端、输出端走线应预留足够线宽,以满足设计电流通过。

2 LDO型电源选用与设计

LDO型电源芯片在工作时理论自身热耗一般较高并且热耗会随着输入输出电压压差增加而增加,同时随工作电流的增加而增加。因此在选用LDO型电源芯片时要注意选用芯片应为金属封装,并且可大面积接地,以提供更好的散热路径;在选用LDO作为供电电源前需确认需求电压与输入电压压差及稳定工作电流,一般压差超过5V、工作电流超过3A时不建议选用LDO型电源芯片,防止热量过多累积。

针对宇航工作环境结合LDO工作原理,待选用的LDO电源型芯片还应具备以下特点:①应具备抗总剂量及单粒子指标,具体指标参照产品运行轨道,一般总剂量 (TID)≥50krad(Si),单粒子特性≥37MeV-cm2/mg;②应内置软启动及过流限制功能。

一般LDO型电源芯片内部主要功能电路为三极管或场效应管,此类元器件在空间环境中可能受单粒子效应影响,导致三极管或场效应管短路,使得输出电压等于输入电压或者输入电源对地短路,因此在宇航产品中选用的LDO型电源芯片一般应具备抗总剂量及单粒子指标,避免单粒子效应导致的供电异常。

LDO型电源芯片一般对外接口比较简单,但应当注意的是由于LDO型电源响应速度快,因此在高速电路设计中,尤其是被供电芯片具有高速开关特性时,LDO型电源的输出端一般需要匹配大容值电容作为储能电容。在输出电容的选用上ESR也是需要注意的重要指标,要严格按手册指定选用,具有过高和过低的ESR的输出电容会导致LDO电源输出的电压产生震荡。

3 星载高速数字电路电源完整性分析

以上对星载高速数字电路的供电部分进行了分析,在电源完整性设计中还有以下一些需要注意的地方。

a)芯片供电引脚的靠近引脚附件需摆放0.1μF~0.01μF电容,在高耗电芯片四周应布局10μF~22μF电容。靠近引脚电容为过滤供电中可能存在的高频干扰,四周大容值电容为储能电容,防止芯片瞬时电流变化导致影响供电电平面的电压稳定。

b)不同相邻电源平面间应该预留耦合电容,可优化整个PCB的EMI特性。

c)相同电压的供电平面应该尽量合并,避免存在多个相同电压的供电平面。

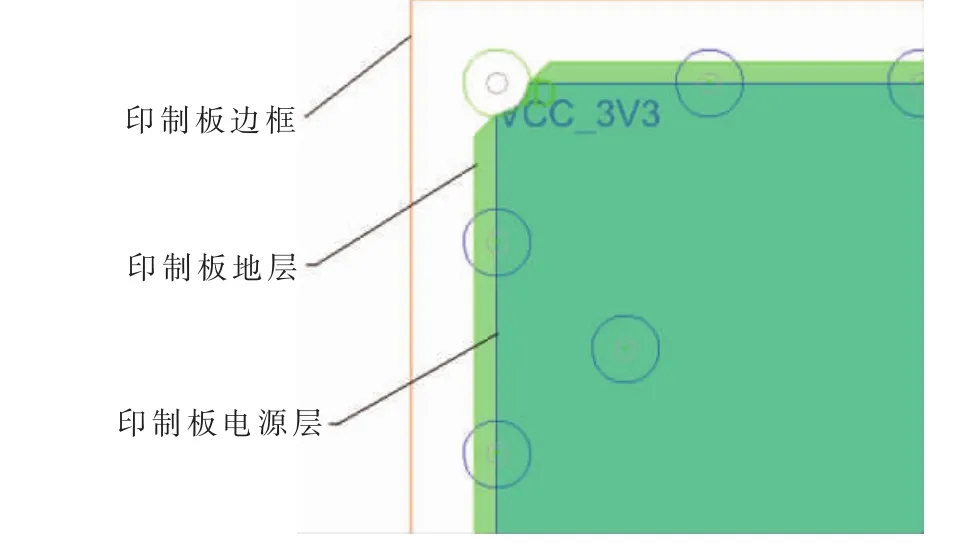

d)在PCB设计中,电源层应该做相应内缩,如图2所示。

图2 电源平面内缩

e)电源层走线宽度必须确保足够宽度。

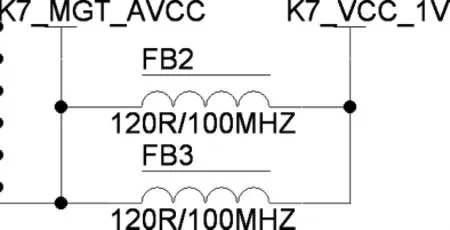

f)若电路设计中同时存在模拟供电及数字供电,若采用的是同一电源需使用磁珠对数字电及模拟电、数字地及模拟地进行隔离,如图3所示,其中K7_MGT_AVCC为模拟电,K7_VCC_1V为数字电。

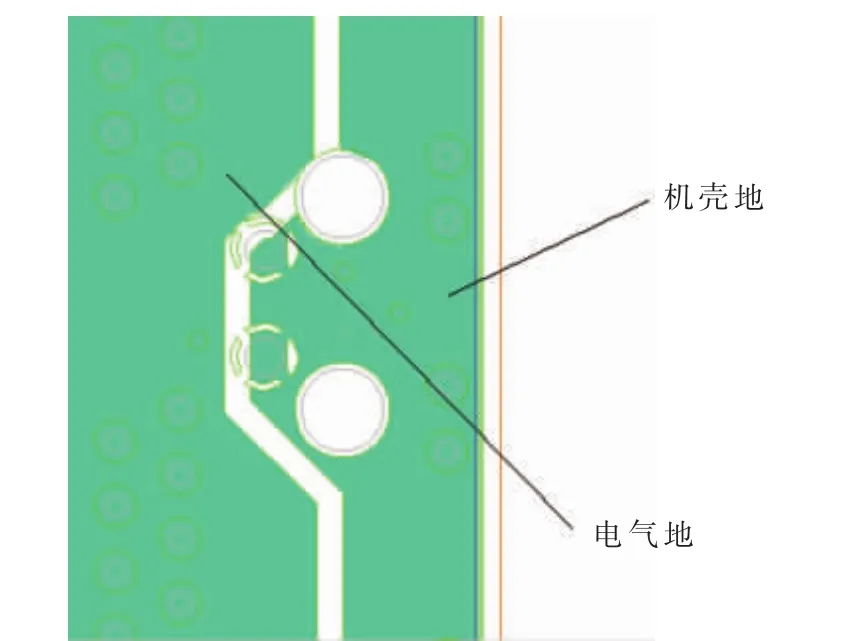

g)机壳地与电气地应该隔离,如图4所示。

图3 数字电源层与模拟电源层的分割

图4 机壳地与电气地隔离参考图