嵌入式网络数据库最优访问路径自动检测系统设计

2020-08-07黄海军韩红章赵小荣

黄海军 韩红章 赵小荣

摘 要: 传统的嵌入式网络数据库最优访问路径自动检测系统在检测过程中覆盖率低,准确性差。针对上述问题,设计了一种新的系统,硬件由采集器模块、处理器模块和检测器模块三部分组成,利用CAN总线连接硬件设备。采集器模块的运行系统为PC104系统,内部装有16 GB CF卡存储器,配合软件工作,选用智能采集通信节点C805 1 FO103作为通信节点;处理器模块内部拥有寄存器单元、算术逻辑单元、输入/输出单元,通过EAD?STROBE脉冲控制信息输入,利用WEAR?FAFAVD脉冲信号执行输出操作。软件分为系统上电复位、信息采集、信息处理三步。为检测系统工作效果,与传统系统进行实验对比,结果表明,给出的检测系统覆盖率更高,准确性更好。

关键词: 嵌入式; 网络数据库; 最优访问路径; 自动检测; 脉冲信号; 覆盖率

中图分类号: TN710?34; TP391 文献标识码: A 文章编号: 1004?373X(2020)13?0159?04

Design of automatic detection system for optimal access path

of embedded network database

HUANG Haijun, HAN Hongzhang, ZHAO Xiaorong

(School of Computer Engineering, Jiangsu University of Technology, Changzhou 213001, China)

Abstract: A new system is designed in view that the traditional automatic detection system for optimal access path of embedded network database has low coverage and poor accuracy in the detection process. The system hardware consists of three parts, named collector module, processor module and detector module. The CAN (controller area network) bus is used to connect the hardware equipment. The operation system of the collector module is PC104 system, equipped with 16 GB CF card memory to work with the software. The intelligent acquisition communication node C805 1 FO103 is used as the communication node. The processor module is internally provided with the register unit, arithmetic logic unit and input/output unit. The EAD?STROBE pulse is used to control the information input and WEAR?FAFAVD pulse signals are used to perform the output operation. The software is divided into system power?on reset, information acquisition and information processing. Contrastive experiments were performed to detect the working effect of the system. The results show that the proposed detection system has higher coverage and better accuracy.

Keywords: embedded type; network database; optimal access path; automatic detection; pulsing signal; coverage rate

0 引 言

嵌入式网络数据库具备独特的运行模式,将其应用到程序中,可以去掉与客户机服务器配置相关设备的开销。嵌入式网络数据库占用内存小,使用代码精简,运行速度快,工作效果理想。在不受到外界干扰的情况下,嵌入式系统可以长时间工作[1]。目前,嵌入式软件系统的开发技术已经成熟,系统内部的管理模式更加成熟、高效、稳定,嵌入式数据库是嵌入式系统的重要组成部分,在确保嵌入式系统稳定运行发挥着重要作用[2]。

嵌入式网络数据库最优访问路径自动检测系统具备检测数据库访问路径的功能,并且能够在多个访问路径中确定出最优访问路径[3]。用户最优路径预测、推荐是目前嵌入式网络数据库挖掘的一个重要方向,检测系统能够向用户推广有效的访问路径,提高搜索引擎的服务效果,为用户提供个性化访问服务[4]。

近年来,对于嵌入式网络数据库最优访问路径自动检测系统的研究较多,目前的检测系统多是根据神经网络算法、关联规则算法、聚类算法提出的。其中,关联规则算法和聚类算法得到了广泛的推广,关联算法能够对用户的浏览历史进行访问,分析用户的浏览记录,推广关联信息,检测适合用户的最优访问路径,但是这种方法过于受到支持度和置信度的影响,如果选择不当,就会加长计算时间,降低推荐性能。聚类算法是根据用户访问界面的布尔量进行推广的,采取的信息过于单一,难以准确检测到最优访问路径[5]。

本文在传统研究的基础上,设计了一种新的最优访问路径自动检测系统,该检测系统能够同时检测出多个访问路径,根据用户平时浏览的资料以及每个路径的性能选取最优路径进行推广。为验证系统性能,设计了实验研究。

1 自动检测系统硬件设计

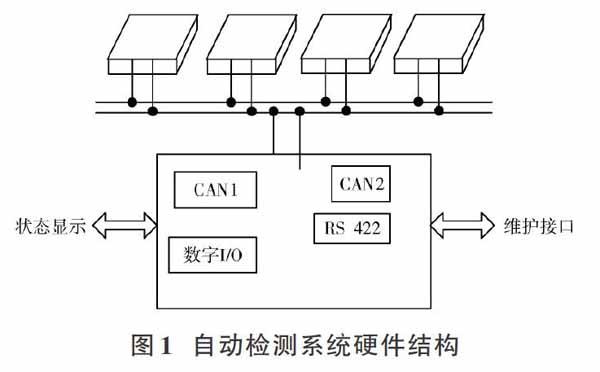

本文设计的嵌入式网络数据库最优访问路径自动检测系统硬件主要包括三部分:采集器模块、处理器模块和检测器模块,通过CAN总线上传给中心系统。采集器负责采集外部信息,将每个网络数据库的信息汇总到一起;处理器负责处理采集器采集到的信息,通过动态曲线图反映处理结果;检测器负责检测最优访问路径,并将检测结果加以比较,综合分析用户的浏览爱好,选出最后的结果,推荐给用户[6]。

嵌入式网络数据库最优访问路径自动检测系统硬件结构如图1所示。

观察图1可知,嵌入式信息处理模块是本文设计的自动检测系统的核心单元,不仅负责信息的处理工作,而且负责将后期得到的信息反馈给中心系统,同时接收外界用户信息。处理器会根据指令进行日常必要的维护工作,从而满足检测系统的本地维护要求和远程维护要求[7]。

系统内部使用的冗余总线为CAN总线,每个采集器和处理器中间都会有2路独立的CAN通道,系统在正常运行时,仅有1路CAN通道和1条CAN总线工作,另1路CAN通道和另1条CAN总线处于备份状态,如果其中一个设备出现故障,备份设备将会启用工作。但是任何时间,工作的CAN总线仅有1条,CAN通道仅有1路。

CAN总线控制器控制CAN总线工作,能够诊断系统故障,当诊断到系统故障时,控制器会自动启动“关闭模式”,检测系统进入离线状态,警报器发出警报声,提醒工作人员采取有效的方法解决。

1.1 采集器模块设计

本文选用的采集器串行总线为CAN总线,CAN总线是目前工业现场常用的串行总线,位速率高,抗电磁干扰能力强,当采集器内部出现故障时,CAN总线能够迅速监测到故障,并且对监测到的故障進行处理,可靠性高、灵活性强、实时性好,对于信息采集有着很好的促进作用[8]。传统的检测系统采集器内部选用的总线为单总线,一旦总线通信出现故障,整个采集器都难以工作,对于远程监测和控制工作起到很大的负面作用,甚至会造成危险,难以维修。单线总线出现故障之后,采集器采集到的所有信息都会丢失。加入了冗余CAN总线后,上述问题得到了很好的解决[9]。

为了满足检测系统的复杂性,本文设计的采集模块CAN总线接入方式为嵌入式接入,采集模块的硬件组成结构如图2所示。

观察图2可知,CAN总线接口设定为开发接口,数据采集器的运行系统为PC104系统,采集器能够对外界信息进行筛选,并且显示出采集到的信息状态。外围控制接口和维护接口都为辅助接口,与CAN总线接口配合工作,帮助系统更好的运行。采集器模块内部的嵌入式处理单元和中心操控系统通过双CAN总线连接到一起[10]。

本文设计的采集器模块能够对现场传感器的数据进行实时采集,同时接收本地命令和远程命令。采集模块的采集单元使用的架构为X86架构,配合PC104计算机系统和CAN总线完成高质量采集。采集器最高运行速度可以达到300 MHz,模块外部拥有丰富的接口,内部装有16 GB CF卡存储器,配合软件工作,方便调试和后期维修。为了更好地满足CAN总线通信接口要求,采集器模块中加入了SEM/CSD?4通信器,4路串行接口和8路并行接口同时工作,为系统日后的升级工作保留巨大空间[11]。

采集器的智能采集通信节点为C805 1 FO103,以高集成的方式组建所有元件,减小系统体积,降低系统功耗,提高系统可靠性。采集器模块内部设置的看门狗超时周期为1.25 s,通过CAN控制器实现冗余总线CAN接口。采集器模块电路图如图3所示。

观察图3可知,当模拟信号进入采集器之后,首先会通过二阶低通滤波器进行滤波处理,然后送入放大器放大电路信号,最后通过12位ADC对数据进行采样和增益转换。

1.2 处理器模块设计

处理器模块选用的CPU为DSP TSAHU3,内部拥有32位×32位的并行硬件乘法器,结构紧密。处理器模块内部资源丰富,拥有20个通用寄存器和18位指令系统,内部的地址线宽度最高可以达到12位,寻址空间[12]为1.5 Kb。处理器利用FPGA位流将文件传给存储器,处理器模块外围不需要设定多个存储器元件。处理器模块内部结构如图4所示。

1) 通用寄存器。处理器模块内部共有8个通用寄存器,工作位数都为8位,负责完成数据读/写工作,同时输入/输出信息,所有的信息都可以反馈给用户。模块内部没有特殊功能寄存器。

2) 算术逻辑单元[13]。提供8位运算,借助寄存器提供的操作数据完成操作,得到的计算结果也会反馈给寄存器。除了普通的运算工作,算术逻辑单元还可以进行布尔操作,使处理器具有灵活的移位操作功能。

3) 输入/输出单元。处理器内部拥有284个输入口和284个输出口,通过一个8位的地址译码器控制输入信号和输出信号,输入口和输出口中的地址既可以是绝对地址,也可以是间接地址。处理器模块在输入信息时,寄存器启动工作,通过READ?STROBE脉冲指示运行的信号,利用Ploc Blaze截取信号。处理器模块在输出信息时,寄存器会将得到的信号传送到输出口中,通过WEAR?FAFAVD脉冲信号执行输出操作,确保处理器传出的信号数据为有效数据。