基于FPGA 的贪吃蛇游戏设计与实现

2020-07-29吕兆承权循忠

李 营,吕兆承,陈 帅,权循忠

当前硬件游戏对功能的要求越来越复杂,传统硬件游戏系统易被盗版且功能不易拓展,已经难以适应市场对硬件设计的要求.可编程逻辑器件FPGA 具有高速并行计算、可编程、易拓展等优点,在智能家居等方面得到广泛地应用[1-3],若采用带有加密功能的FPGA 芯片实现游戏机平台设计,可避免软件游戏易受到黑客攻击的问题,且功能易拓展.鉴于此,本文根据PS2 键盘原理和VGA 时序显示原理,利用层次化建模思想设计硬件贪吃蛇游戏系统.

1 贪吃蛇游戏系统工作原理

1.1 游戏设计思路

本系统选用Altera 公司的锆石Cyclone IV系列EP4C6E10F17C8 开发板设计实现贪吃蛇游戏[4],系统由PS2 键盘接口、VGA 接口、FPGA芯片等构成.设计时将PS2 键盘与系统的PS2接口连接,将VGA 接口连接到一台显示器.显示器上有一自动移动的“蛇”,通过PS2 键盘的W、S、A、D 键实现“蛇”相应上、下、左、右方向改变.“蛇”在显示器一定范围内运动,若碰到VGA 显示器的边缘或者“蛇”的身体,则游戏结束.每当“蛇”吃到一只青蛙则VGA 屏幕有效区域会随机出现一只“青蛙”,且此时得分加1,分值在数码管显示.最终以FPGA 芯片为核心控制器,完成简单的硬件贪吃蛇游戏.

1.2 VGA 显示原理

设计中VGA 显示及时序信号控制应遵循VGA 工业标准,文中采用的640*480@60 Hz 通信时序,其原理在文献[5]中已详述,此处不再叙述,对应的行周期为31.75 ns,场周期为16.6 ms.

1.3 PS2 协议与通信原理

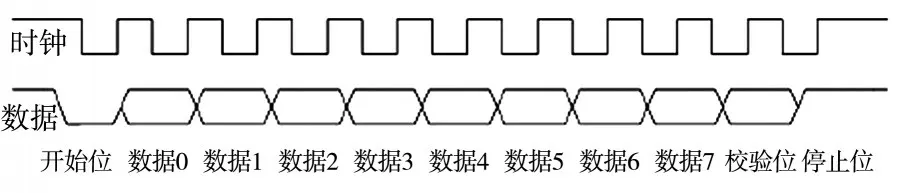

PS2 是一种应用于鼠标和键盘的遵循双向同步串行协议[6].文章使用PS2 接口键盘发送数据到FPGA,故主要分析PS2 键盘原理.PS2 键盘到主机传送的数据以11 位为一帧,具体含义如表1 所示.

表1 键盘到主机PS2 帧数据含义

PS2 键盘要发送数据时,首先检查时钟是否为1,若不是则主机抑制通信设备,键盘需要缓冲任何要发送的数据直至时钟线为高电平才可以发送数据[7-8],如图 1 所示.主机可在停止位之前将时钟电平拉低,键盘放弃发送当前字节.

图1 键盘到主机的通信过程

1.4 PS2 接口键盘控制器设计

按键被按下或释放时,键盘上的处理器会根据相应的按键发送唯一的“通码”或“断码”[9-10],文中用到的控制上、下、左、右键方向的四个键分别是W、S、A 和D,其相应的通码、断码和ASCII 码如表2 所示.

表2 文中用到的PS2 的第二套扫码集信息

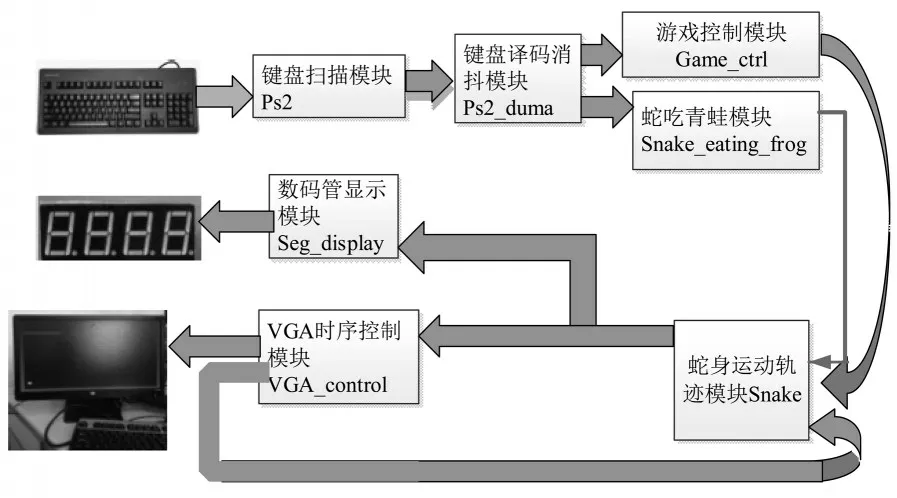

2 系统总体实现

依据层次化建模思想和Verilog HDL 设计实现各功能模块.系统的设计思路和功能框图如图2 所示.从图2 可知,该系统底层可划分为:用于控制方向的键盘扫描模块(Ps2.v),键盘译码消抖模块(Ps2_duma.v),游戏控制模块(Game_ctrl.v),蛇身运动轨迹处理模块(Snake.v),蛇吃青蛙处理模块(Snake_eating_frog.v),数码管显示模块(Seg_display.v),VGA 时序控制模块(VGA_control.v),顶层模块(top.v).

图2 系统设计思路和功能框图

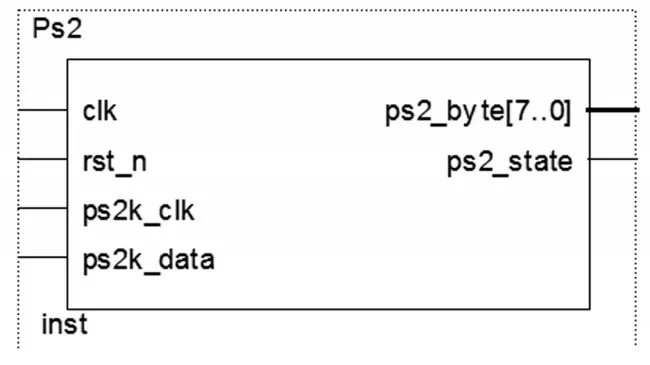

2.1 键盘扫描模块

该模块的输入信号包括50 M 时钟clk,复位信号rst_n,PS2 接口时钟信号ps2k_clk 和8bit数据信号ps2k_data.模块功能是在ps2k_clk 时钟下,不断扫描读取ps2k_data,从而输出按下键的8bitASCII 码值ps2_byte,并输出此时的键盘状态ps2_state.其中ps2_state 为1 表示有键被按下,ps2_state 为0 表示无键按下.该模块的接口框图如图3 所示.

图3 键盘扫描模块接口图

2.2 键盘译码及消抖模块

该模块的功能首先是接收PS2 键盘扫描模块输入键的ASCII 码值ps2_byte 和按键状态ps2_state,然后进行消抖和译码,最后控制下一时刻蛇身的运动方向.该模块的接口框图如图 4 所示 .图 4 中,输入端口 ps2_byte 为 PS2键盘的按键的ASCII 码值,ps2_state 代表按键状态.输出端口有 up、down、left、right 4 个,分別表示 PS2 键盘 W、S、A、D 四个按键的各自状态,利用其值控制蛇身的上、下、左、右运动方向.如up 值若为1,代表W 键被按下,蛇身朝上运动,其他按键功能类似,此处不再列出.

图4 键盘译码消抖模块接口图

2.3 游戏控制模块

本模块是从其他模块接收信号,决定游戏状态(ready、play、die),并且产生其他模块的控制信号.在ready 的状态下,只要有键按下(上、下、左、右),蛇就会自动向右运动,从而进入play 状态.在play 状态下,本模块等待hit_wall 或者hit_body 的信号,如果这两个信号发生,则进入die 状态,即游戏结束.在die 状态下,屏幕会闪烁一段时间,最后进入ready状态[8],该模块的接口框图如图5 所示.

图5 游戏控制模块接口框图

2.4 蛇吃青蛙处理模块

此模块的功能是在液晶显示器有效区域内随机产生一只青蛙,并且需要判断蛇是否已吃下青蛙,该模块的接口示意图如图6 所示,图中head_x、head_y 是蛇头出现的位置,frog_x、frog_y 是青蛙出现的位置,add_cube 的含义是蛇身新增方块.

图6 蛇吃青蛙处理模块接口框图

2.5 蛇身运动轨迹处理模块

该模块需要完成以下四个功能:①保持蛇的运动;②根据按下的键改变蛇的运动方向;③判断蛇是否碰撞墙或者自己的身体;④在液晶显示器上显示[4].该模块最终完成后的接口框图如图7 所示,图中cube_num 的含义是蛇身方块构成蛇身,head_x、head_y 是蛇头出现的位置,hit_body 指蛇运动时撞到蛇身,hit_wall 指蛇运动时撞到墙.

图7 蛇身运动轨迹模块接口框图

2.6 VGA 时序控制模块

该模块直接控制液晶屏的显示.产生五个信号:红、绿、蓝三色信号和行帧同步信号.设计中接收蛇头snake 的像素坐标,以及青蛙的坐标进行相应地显示,该模块的接口框图如图8 所示.

图8 VGA 时序控制模块接口框图

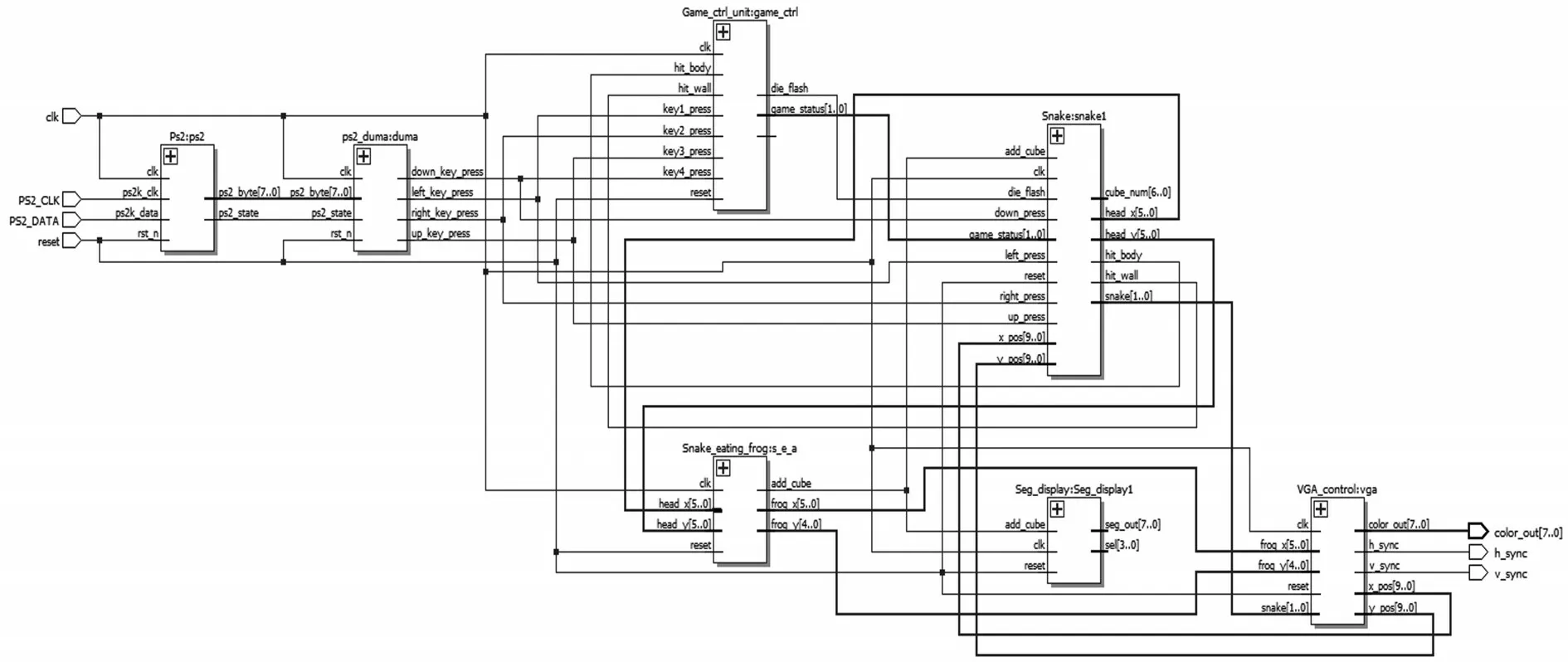

2.7 顶层模块

顶层模块的作用是进行各底层模块间数据信号和控制信号之间的连接,同时调用上述6 个模块,以及数码管显示模块,数码管模块较为简单,文章不再列出,最终实现系统要求.其核心代码为:

module Greedy_Snake(

input clk,

input reset,

input PS2_CLK,//PS2 的时钟端口

input PS2_DATA,//PS2 的数据端口

output h_sync,

output v_sync,

output[7:0]color_out

output[7:0]seg_out,

output[3:0]sel);

//中间连线声明

//调用上述六个模块(略)

//调用数码管显示模块(略)

endmodule

3 系统仿真结果

3.1 系统开发工具

①仿真软件:QuartusⅡ13.1;

②硬件描述语言:Verilog HDL;

③实验开发板:锆石A4系列EP4C6E10F17C8.

3.2 系统软件仿真

系统设计完成后生成的RTL 图,如图9 所示,由图9 可知各个功能模块与图2 系统设计思路和功能框图一致[4],说明系统设计思路正确.

3.3 系统时序信号仿真

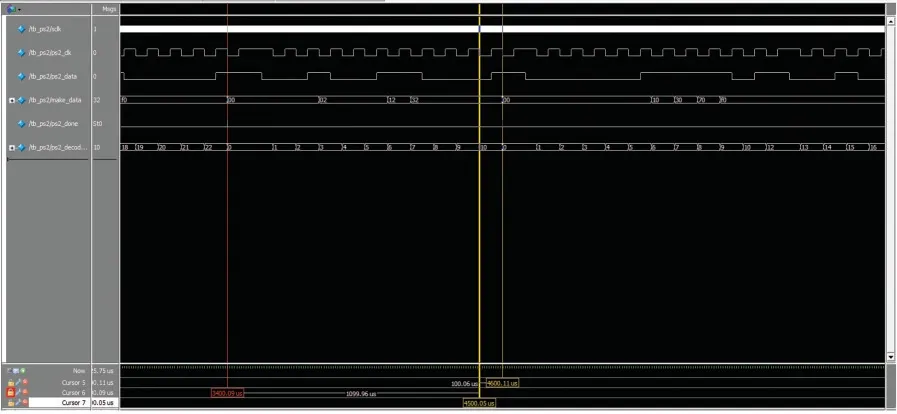

系统设计完成后编写测试文件进行时序仿真,结果如图 10 所示. 图 10 中 sclk 是 50 MHz 输入时钟信号,ps2_clk 为键盘输入时钟,ps2_data 是键盘依次按下 A、B、C 三个按键时对应的截图,图10 中分析线对应的是B 键发送时的情形,此时对应的接收后的ASCII 码是8‘h32,且此时 PS2 时钟为 100 us,PS2 键盘到主机传送的数据以11 位为一帧,且与文中1.3小节所要求的PS2 帧数据接口时序一致,说明PS2 键盘时序满足系统设计要求.

图9 系统RTL 图

图10 PS2 键盘发送按键B 时对应时序仿真图(截图)

3.4 系统硬件显示效果

FPGA 作为处理器读取PS2 键盘发送按键信息后,通过VGA 接口显示贪吃蛇游戏运行界面,通过W、S、A、D 四键分别控制蛇上、下、左、右移动,最终使其能够吃到青蛙,并在数码管端显示游戏成绩,结果达到了系统设计要求.

4 结语

文章在640*480@60 Hz 分辨率下,利用自顶向下层次化建模思想,设计出基于FPGA 的贪 吃蛇系统[11],并通过 Cyclone IV 系列的EP4C6E10F17C8 器件进行了硬件验证.文章提出的利用 FPGA 芯片、PS2 键盘、VGA 显示器等硬件设计贪吃蛇游戏系统是一种新的硬件游戏设计思路,该思路是利用FPGA 芯片开发游戏的有效尝试,相较传统的单片机游戏系统而言,本系统功能更易拓展,具有一定的参考价值.