基于FPGA的帧级异步FIFO设计

2020-07-23水颖

水颖

(第七一五研究所,杭州,310023)

目前,在传输业界中,网关、加扰机、编码机及调制解调设备等多采用千兆级以太网作为交互接口,要完成交互过程中大容量数据简单方便的缓存,通常采用板载FIFO、SRAM、SDRAM或DDR颗粒芯片的方案。在一些对存储资源要求不高但对存储速度要求高的应用中,大多使用FPGA内部的存储器资源。FIFO 是一种在电子系统得到广泛应用的模块,通常用于数据的缓存和容纳异步信号的频率或相位的差异。FIFO 的实现通常是利用双口RAM 和读写地址产生模块来实现的。

本文根据互联网帧的实际处理,提出了一种帧级 FIFO的设计,从而完成整帧数据处理的异步FIFO[1],设计的 FIFO处理模块是针对每一帧而不是每一个数据。根据FPGA提供BRAM块,搭建FIFO的读写以及数据使能,最关键的设计是控制读写地址、产生空满信号以及校验。此方式产生帧级的异步FIFO,既可以减少使用内部FIFO带来资源高的问题,又可以隔离异步时序减少亚稳态的产生。

1 功能描述及组成

传统的异步时序FIFO,当写入一个FIFO位宽的数据,FIFO的空信号(empty)置0,则可以进行读取数据。本文设计的基于帧级异步时序FIFO,当一个正常数据包正在写入时,FIFO的空信号并不会置0;只有当正常数据包全部写入异步FIFO中,空信号才能置 0,数据才能够被读取。此方式有利于互联网帧级数据的缓存和处理。

帧级FIFO是将一个数据包作为一个最小单元进行存储,包括以下几种情况:(1)数据包为坏包,则通过控制写RAM地址,刷新至上一包结束位置,将其从FIFO中删除;(2)数据包长度大于RAM剩余空间,则进行丢包处理;(3)正常数据包则写入RAM,更新写指针。当整个包写入后RAM后,输出不空标志,使得FIFO数据可以被读取。

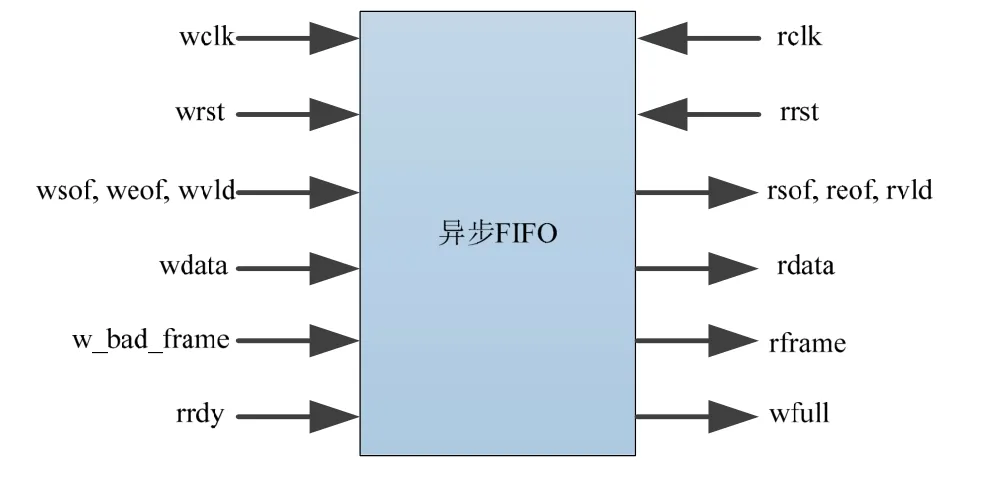

本文异步时序FIFO使用双端口RAM实现。FIFO 的接口信号包括异步的写时钟(wclk)和读时钟(rclk)、与写时钟同步的写有效(wvld)和写数据(wdata&wsof&weof)、与读时钟同步的读有效(rvld)和读数据(rdata&rsof&reof)。为了实现正确的读写,避免 FIFO 的上溢或下溢,通常还应该给出与读时钟和写时钟同步的 FIFO 的空标志(rframe)和满标志(wfull)以禁止读写操作。帧级FIFO的模块接口图见图1。

图1 异步FIFO的信号接口

2 设计方法

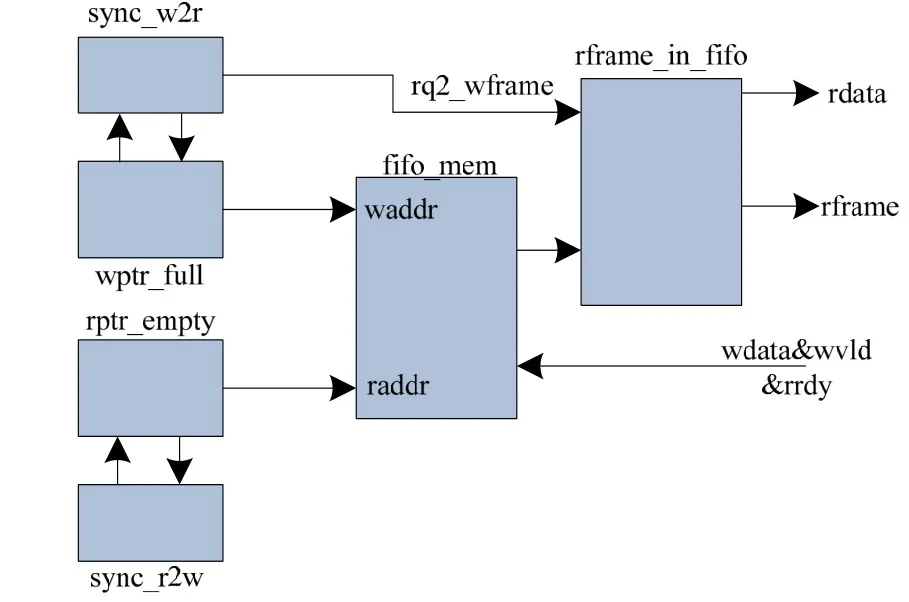

本文根据互联网帧级数据缓存原理,实现帧级FIFO的设计,由 6个模块来完成:fifomem、wptr_full、rptr_empty,sync_r2w、sync_w2r 和rframe_in_fifo模块。具体设计框图如图2所示。

fifomem 模块主要功能是存储数据。模块调用了xilinx的BRAM块作为存储单元块,根据产生读写地址进行数据存取。主要的存储处理流程如图3所示。

wptr_full 模块主要功能是产生写地址和写满的控制信号。每写入一拍数据地址加 1,如此递增产生写地址。当数据包为正常包,数据包length大于剩余空间,写满信号置 1;当数据包为坏包,虽然数据包length大于剩余空间,写满信号仍然为0。rptr_empty 模块主要功能是产生读地址和读空的控制信号。读地址与写地址产生方式相同,读出去一拍数据则自增。读写指针一致产生读空信号。sync_r2w和sync_w2r 模块主要是负责两个不同时钟域的单比特信号处理。空满信号的产生,需要跨时钟域信号处理。单比特跨时钟域信号处理使用寄存器打拍方式。rframe_in_fifo 模块主要是通过状态机的方式产生读取 BRAM 的控制信息。本模块主要根据 rq2_wframe信号即整帧数据写完成标志和fifo_mem模块读出的数据状态,产生FIFO控制信息。主要状态机处理见图4。

图2 帧级FIFO设计框图

图3 写RAM的处理流程图

图4 读RAM的状态机图

状态机空闲时刻为IDLE状态。当rframe信号为1,说明FIFO不空,则开始读取包头SOF和数据FRAME部分,读至EOF,即一个数据包结束,状态机再次回到空闲状态。循环读取异步FIFO中数据包,完成帧级FIFO读取功能。

3 帧级FIFO的Verilog实现

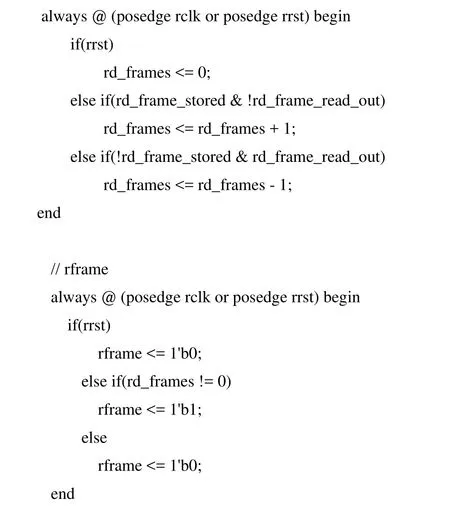

硬件描述语言是一种应用于电路设计的高层次描述语言,具有行为级、寄存器传输级和门级等多层次描述,并且具有简单、易读、易修改和与工艺无关等优点。目前,Verilog 语言已经得到多种EDA工具的支持,综合工具得到迅速发展。Verilog语言的行为级综合也已得到支持和实现,因此利用Verilog 语言进行电路设计可以节约开发成本和周期。实现调用了xilinx的BRAM原语,这样做的好处是可以适合所有不同xilinx器件进行调用。帧级FIFO rframe即为empty信号的产生代码如下[2]:

4 仿真和实测结果

帧级FIFO设计的关键在于控制读写地址和空满信号。写入地址根据正常包自加,而坏包进行刷新初值操作。当写入一个完整数据包时会产生不空信号,FIFO才允许读取。另一个关键点是异步的处理,正常异步多比特信号处理使用 BRAM 和握手两种方式,本文使用了 BRAM 的方式实现流水,减少异步时序带来的亚稳态。

异步 FIFO的整包仿真结果如图 5(a),产生rframe信号的仿真结果如图5(b)。wclk信号为写数据时钟,wvld信号为写数据使能,wdata信号为写数据,wsof信号为写帧级数据的起始标志,weof信号为写帧级数据的结束标志。通过判断 weof结束,如果不为 w_bad_frame(坏包),则 fifo不空,rframe信号置1。检测到rframe信号为1,则开始读取数据包,直至读取EOF标志,输出整帧数据包。仿真测试结果与设计相符,完成帧级FIFO的功能需求。本方案已通过设备的传输采集系统应用验证,帧级异步FIFO基于采集板进行收发包测试时,测试结果通过Xilinx公司Chipscope Logic Analyzer抓包软件。探测显示结果如图5(c)所示,实际抓包信号与仿真结果一致,符合预期。7×24 h拷机测试时性能也稳定可靠。

图5 异步FIFO的仿真结果与实测结果

5 结论

本文提出了一种帧级异步 FIFO 的设计,并以Xilinx公司V5系列的一款FPGA为设计平台,基于ISE 14.6 设计软件和Modelsim 10.4仿真软件,采用Verilog HDL高级可编程语言完成设计实现了信号采集传输系统。该电路实现了互联网整帧数据的存取,软件仿真和硬件实现已经通过验证,并已实际应用。实践证明它处理互联网整帧数据可靠性高、稳定性强。该设计可以直接应用于互联网数据的传输和处理,具有较强的工程实用价值。