面向极低功耗收发器的分数锁相环架构设计

2020-07-11何昊晨

何昊晨

面向极低功耗收发器的分数锁相环架构设计

何昊晨

(武汉理工大学 自动化学院,湖北 武汉 430070)

分数锁相环的毛刺是噪声耦合到带内的原因之一,导致收发器使用更高的功率实现等同的灵敏度。针对该问题,提出一种基于可变幅度电荷泵(Variable Amplitude Charge Pump,VACP)和固定脉冲、可变周期信号发生器(Fixed Pulse Variable Period Signal Generator,FPVPSG)的低毛刺分数锁相环架构。在FPVPSG的驱动下,VACP的输出电流脉冲不仅有固定位置、固定宽度、可变幅度,而且有可变周期,用于根除参考毛刺和分数毛刺。基于Spectre的仿真结果表明,当参考频率REF为20 MHz,小数分频为120.13,且瞬态和锁定时的周期分别为1/REF和27/REF时,20 MHz及其整数倍的参考毛刺被根除,10 MHz的分数毛刺较已有方案小19.67 dB,且其他分数毛刺均远小于已有方案。该结果表明推荐的分数锁相环架构可用于极低功耗收发器,在移动物联网和边缘计算领域有一定的应用前景。

极低功耗收发器;交调干扰;噪声;分数锁相环架构

1 引言

在移动物联网和边缘计算等领域,大部分收发器布局在户外或其他较难维护的场景,开发者应设计高性能的器件,用于尽可能降低收发器的功耗,使其具有较长的使用寿命。分数锁相环(Fractional Phase-Locked Loop,FPLL)为收发器提供本振信号,将基带信号上变频到射频或者将接收信号下变频到基带,它的毛刺将恶化收发器的信噪比,导致发射器使用更高的发射功率实现等同的灵敏度,不利于节省收发器的功耗。因此,研究更低毛刺的FPLL架构对实现极低功耗的收发器具有重要的意义,一直为学术界和工业界关注的研究热点。

现有大多数FPLL的架构通过零死区的鉴频鉴相器[1-2]、高匹配的电荷泵[3]、采样环路滤波器[4]、低噪声的分频器[5]和低噪声的压控振荡器[6]等减小毛刺。但是,以上技术均存在脉冲宽度调制和脉冲位置调制等效应,毛刺不能从源头被根除[7]。KATUMBA提出了一种基于固定宽度可变幅度电荷泵的FPLL架构,用于移除脉冲宽度调制效应和脉冲位置调制效应,然而该方法仅能根除参考毛刺。基于已有技术的积累和不足,提出了一种能移除脉冲宽度和脉冲位置调制的低毛刺FPLL架构,不仅能根除参考毛刺还能降低分数毛刺。该架构与已有架构的主要区别在于可变幅度的电荷泵(Variable Amplitude Charge Pump,VACP)和固定脉冲、可变周期的信号发生器(Fixed Pulse Variable Period Signal Generator,FPVPSG)。在FPVPSG的驱动下,VACP的输出电流脉冲不仅具有固定的位置、固定的宽度、可变的幅度而且具有可变的周期,因此能根除参考毛刺和降低分数毛刺。首先根据问题分析引入研究低毛刺FPLL架构的意义,然后给出了推荐的FPLL架构并介绍了工作原理,最后通过Spectre仿真验证了该架构移除整数毛刺和分数毛刺的可行性,并给出了相关的结论。

2 问题分析

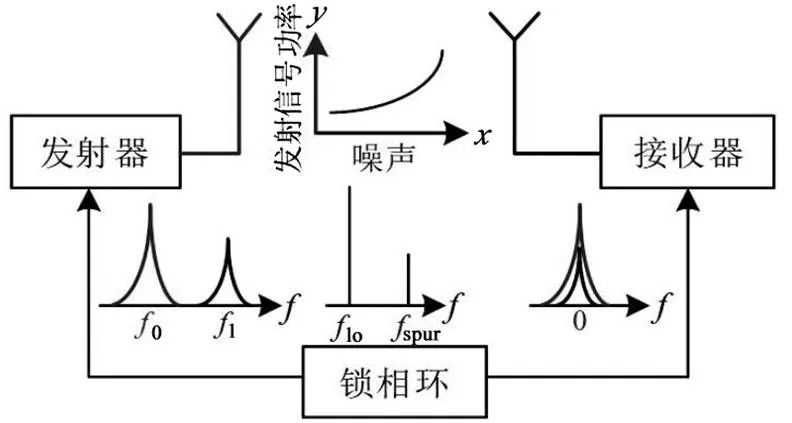

收发器的架构主要包括发射器、接收器和锁相环。收发器的灵敏度固定不变时噪声、发射信号的功率和FPLL输出信号的频谱纯度之间的关系如图1所示。

图1 收发器灵敏度不变时噪声、发射信号功率和FPLL输出信号的关系

信号和干扰的所在的频率分别为0和1,锁相环输出信号的频率和毛刺所在的频率分别为lo和spur,在零中频收发器中lo等于0。锁相环为收发器提供本振,用于将位于0的信号下变频到基带(或者将基带信号上变频到0)[8]。此时,如果锁相环的输出信号在spur处存在毛刺且spur等于1,则在下变频的过程中频率1处的噪声被耦合到0频处的信号内,因此增加了接收信号的噪声,需要通过增加发射信号的功率维持恒定的灵敏度。在移动物联网、边缘计算和5G无线移动通信系统中,由于各种无线通信协议并存,邻道干扰更严重。开发者通常选择低功耗的通信协议、低功耗的发射器和低功耗的接收器,并且相关的低功耗技术已经处于瓶颈期[9-11]。基于该原因,本论文提出了一种低毛刺的分数锁相环架构,避免锁相环的毛刺恶化收发器信噪比,从减小毛刺降低收发器功耗的角度为开发者提供一种低功耗技术。

3 架构设计

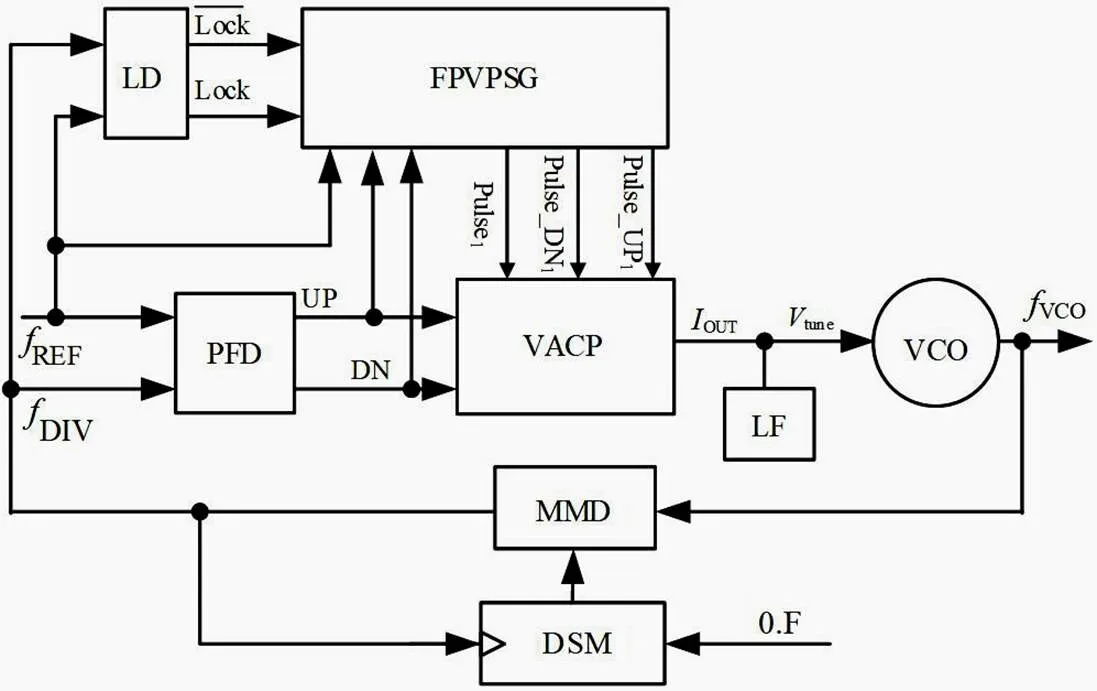

推荐的低毛刺分数锁相环架构如图2所示,包括鉴频鉴相器(Phase Frequency Detector,PFD)、锁定检测器(Locking Detector,LD)、VACP、FPVPSG、环路滤波器(Loop Filter,LF)、电压控制振荡器(Voltage-Controlled Oscillator,VCO)、多模分频器(Multi-Mode Divider,MMD)和Delta-Sigma调制器(Delta-Sigma Modulator,DSM)共8个模块。该架构与传统的架构的区别在于VACP和FPVPSG这2个模块,其中FPVPSG产生Pulse_UP1脉冲、Pulse_UP0脉冲和Pulse1脉冲,用于驱动VACP产生固定位置、固定宽度、可变幅度和可变周期的输出电流脉冲OUT。

图2 推荐的低毛刺分数锁相环架构

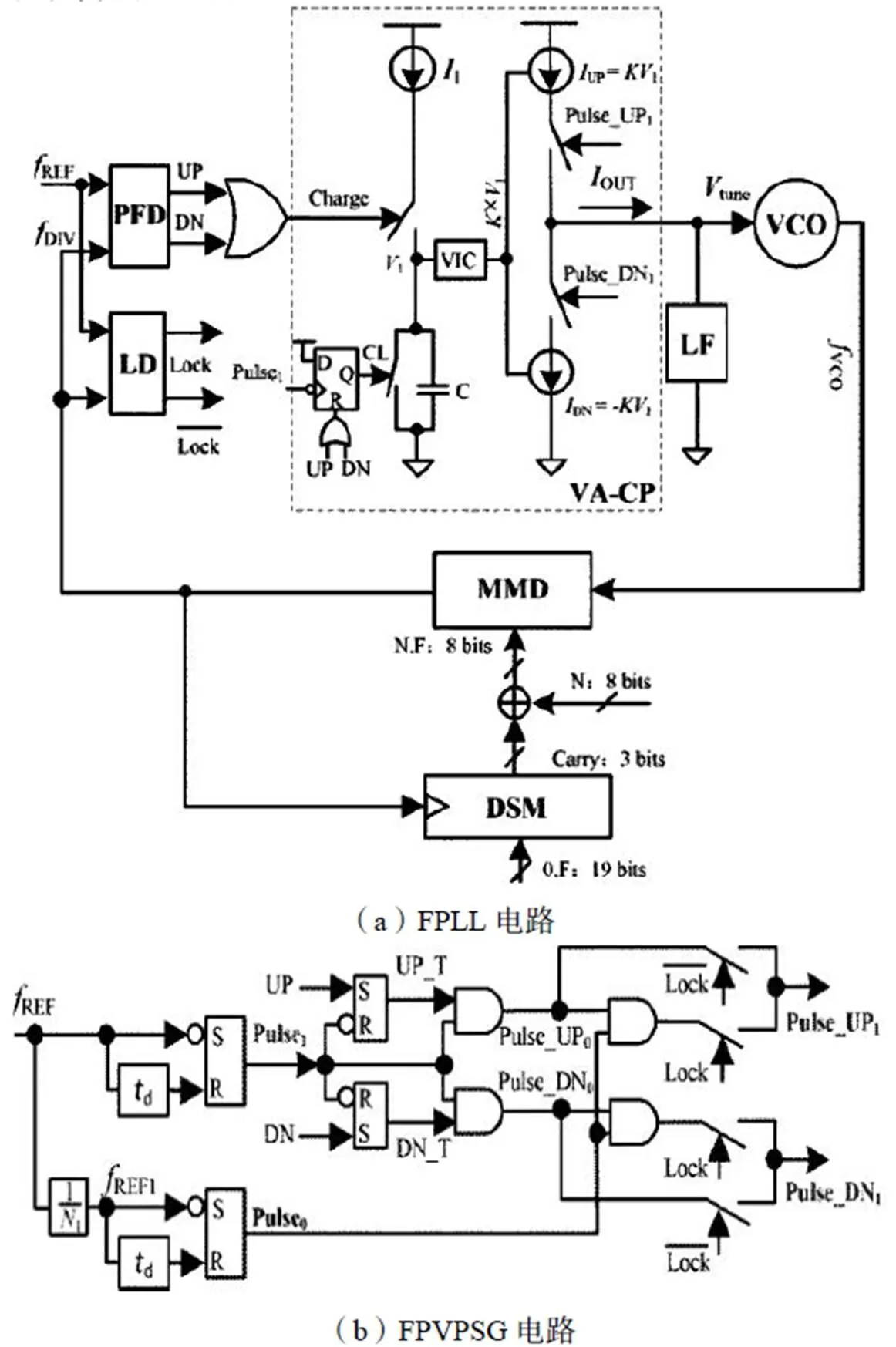

基于VACP和FPVPSG的低毛刺分数锁相环架构如图3所示。MMD的分频控制字N.F为整数部分。和进位:Carry的和,其中采用8位的二进制,Carry采用3位的二进制,DSM的输入0.F采用19位的二进制,Carry为0.F通过DSM不断积累产生的进位溢出。结合该电路,推荐的PFLL架构的两个创新点说明如下:①UP或DN为REF和DIV之间的误差,当REF领先DIV时UP输出高电平,当REF滞后DIV时DN输出高电平,它们通过或门生成Charge信号,用于驱动电流1对电容C充电。充电前电容C上的电压1通过D触发器清零,由Pulse1脉冲控制实现,因此1与REF和DIV之间的误差error成正比。1通过电压-电流转换器(Voltage- Current Convertor,VIC)转换为电流1,为无量纲比例因子,充电电流UP=1,且放电电流DN=﹣1。②Pulse_ UP1脉冲和Pulse_DN1脉冲驱动VACP产生输出电流OUT,它们的位置、宽度和周期分别为REF的下降沿、d、瞬态时为1/REF且锁定时为1/REF。因此,VACP的输出电流脉冲OUT具有固定的位置、固定的宽度、可变的幅度和可变的周期,其中固定的位置、固定的宽度和可变的幅度等特性可用于根除参考毛刺;同时,因为FPLL锁定时的周期增加1倍,使得毛刺的功率被均衡到0到无穷大频率之间,所以可以降低分数毛刺。

假设1为3、相位误差阈值为0且REF领先DIV,则FPLL的时序如图4所示。

图3 基于VACP和FPVPSG的低毛刺分数锁相环架构

图4 推荐FPLL的时序

结合该时序图,FPLL具体的工作过程描述如下:首先FPLL处于瞬态(Transient),Lock输出低电平,Pulse_UP1、Pulse_UP0和Pulse1具有相同的波形,此时UP驱动OR门产生充电信号Charge对电容C充电,并且从Charge的上升沿到CL的上升沿期间充电电流UP等于1。同时,UP_T用于驱动UP,Pulse_UP1、Pusle_UP0和 Pulse1的位置、宽度和周期分别为REF的下降沿、d和1/REF,因此Pulse_UP1驱动VACP输出电流脉冲OUT,它的大小、宽度、周期和位置分别为1、d、1/REF和REF的下降沿。另一方面,当error小于0时,FPLL进入锁定状态(Locking),Lock输出高电平,Pulse_UP1为Pulse_UP0和Pulse0的与运算结果。因为1=3,REF1和Pulse0的周期为3/REF,用于驱动Pulse_UP1每3个参考周期对UP采样,因此FPLL锁定时VACP输出电流脉冲的周期为3/REF。

在实际电路中,1的取值应同时保证FPLL具有较快的锁定时间和较小的毛刺。虽然FPLL的毛刺与1的值成反比,但是过大的1值将延迟FPLL的锁定时间。例如,当图3处于锁定状态时,在3个参考周期内只有第1个周期用于纠正REF和DIV之间的相位误差error,而在第2个周期到第3个周期内,因为相位误差没有被纠正,导致相位误差不断被积累。如果1的取值足够大,将使得第2个周期到第1个周期内积累的相位误差大于0,则FPLL再次进入瞬态,并且有可能使FPLL在一段时间内处于锁定状态和瞬态交替的状态,因此较大程度延迟了FPLL的锁定时间。

4 仿真验证

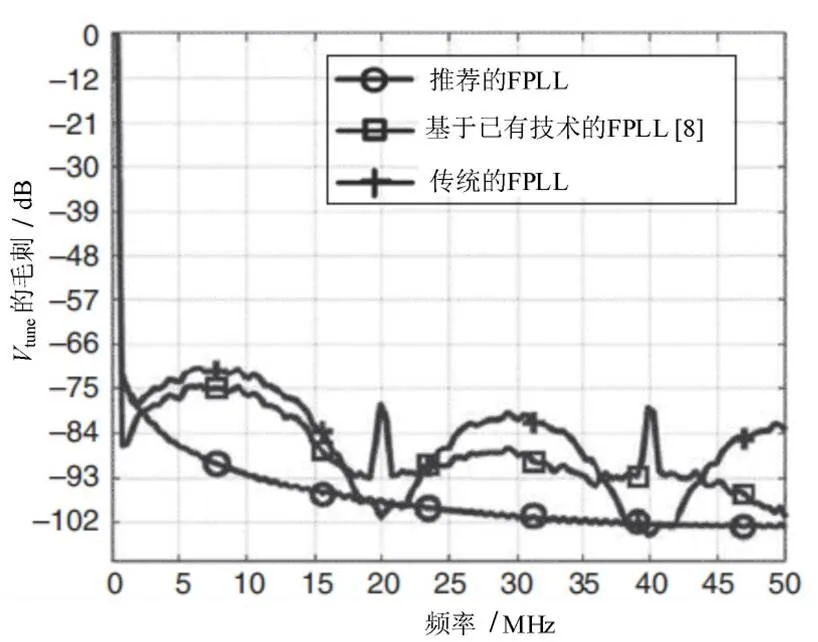

传统的FPLL、基于已有技术的FPLL和推荐的FPLL的环路参数如表1所示,其中VCO、VCO和分别为VCO的增益、输出频率和FPLL的环路带宽,并且1、和的取值为了使FPLLs中电荷泵的的增益相同。因为VCO为tune控制的频率输出器件,它的频谱特性与tune具有一致性,所以可以通过仿真tune的频谱分析不同FPLLs架构的毛刺性能。因为N.F=120.13,参考频率REF为20 MHz,VCO的频率为2 402.6 MHz,因此FPLLs锁定时tune的值为513 mV。此外,1的设定方法如下:将1设为变量,同时将锁定时间和在10 MHz或其他频点处的分数毛刺设为因变量,通过计算机仿真得到锁定时间急剧上升且毛刺没有较明显改善的临界点。本设计中的临界点为27,因此1的值设为27。

表1 推荐的FPLL、已有的FPLL和传统FPLL的环路参数

参数推荐的FPLL已有的FPLL [8]传统的FPLL fREF/MHz202020 KVCO/(MHz·V-1)200200200 fVCO/GHz2.3~2.52.3~2.52.3~2.5 BW/MHz111 N.F120.13120.13120.13 IUP(IDN)KV1KV1100 μA I1/mA11— C/pF200200— td/ns55— θ0/ns1—— K0.0040.004—

利用Spectre仿真得到tune锁定到513 mV的波形,并截取140~140.96 μs时间段内的数据作为分析对象,用一种平滑系数为1、窗大小为256、采样点为4 096的汉宁窗分析tune的频谱。仿真结果如图5所示。基于已有技术的FPLL和推荐的FPLL在20 MHz和其他参考频率处均没有参考毛刺;在分数频率为10 MHz处的分数毛刺较已有的FPLL和传统的FPLL分别小19.67 dB和 16.22 dB,并且在其他分数频率处的分数毛刺均小于已有的FPLLs。

图5 推荐的FPLL、已有的FPLL和传统FPLL的毛刺性能

5 结论

提出了一种用于极低功耗收发器的低毛刺FPLL架构,用于根除FPLL的参考毛刺和分数毛刺。首先从系统层面分析了锁相环的毛刺影响收发器功耗的问题,然后提出了一种低毛刺的FPLL架构,并阐述了它的基本工作原理,最后利用Spectre仿真验证了该架构根除参考毛刺和分数毛刺的可行性。仿真结果表明,提出的FPLL架构具有可行性。

[1]HWAN S C,BYUN S.On frequency detection capability of full-rate linear and binary phase detector[J].IEEE Transactions on Circuits & Systems ii Express Briefs,2017,64(7):757-761.

[2]ABDUL M K K,KAILATH B J.Low power PLL with reduced reference spur realized with glitch-free linear PFD and current splitting CP[J].Analog Integrated Circuits and Signal Processing,2017,93(1):29-39.

[3]WANG D Z,ZHANG K F,ZOU X C.High current matching over full-swing and low-glitch charge pump circuit for PLLs[J].Radio Engineering,2013,22(1):153-158.

[4]WANG K J,GALTON I.A discrete-time model for the design of type-II PLLs with passive sampled loop filters[J]. IEEE Trans. Circuits Syst I,2011,58(2):264-275.

[5]SANYAL A,YU X Y,ZHANG Y L,et al.Fractional-N PLL with multi-element fractional divider for noise reduction[J].Electron Lett,2016,52(10):809-810.

[6]WANG D Z,ZHANG K F,ZOU X C.Wideband Q-VCO using tail-current shaping based automatic amplitude control[J]. Miroelectronics Journal,2013,44(5):367-372.

[7]THAMBIDURAI C,KRISHNAPURA N.On pulse position modulation and its application to PLLs for spur reduction[J].IEEE Trans Circuits Syst I,2011,58(7):1483-1496.

[8]SAKIAN P,MAHMOUDI R,ROERMUND H M.System level reciever design for minimum sensitivity to process variations[J].IEEE Trans Circuits Syst I,2011,58(10):2296-2307.

[9]KUO F W,FERREIRA B F,CHEN H N R,et al.A bluetooth low-energy transceiver with 3.7-mW all digital transmitter,2.75-mW high-IF discrete-time receiver and TX/RX switchable on-chip matching network[J].IEEE J Solid-State Circuits,2017,52(4):1144-1162.

[10]MARTORELL A,RAOULT J,MARIJON R,et al.RF front-ends nonlinearity characterization using reflected power[J].IEEE Trans on Electromagnetic Compatibility,2017,59(6):1925-1931.

[11]KIAYANI A,ANTTILA L,KOSUNEN M,et al.Modeling and joint mitigation of TX and RX nonlinearity-induced receiver desensitization[J].IEEE Trans on Mircowave Theory and Techniques,2017,65(7):2427-2442.

TN74

A

10.15913/j.cnki.kjycx.2020.13.016

2095-6835(2020)13-0043-03

何昊晨(1999—),男,本科在读,研究方向为控制科学与工程。

〔编辑:严丽琴〕