基于90 nm GaAs PHEMT工艺的二次倍频器芯片的设计

2020-07-09任璇

摘 要:基于90 nm GaAs PHEMT工艺设计了一款二次倍频器芯片,通过探针台对芯片性能进行了评估。倍频器芯片输入频率为9~15 GHz,输出频率为18~30 GHz。芯片电路中包含了输入、输出两级驱动放大器、一个二次倍频器和一个带通滤波器,可以实现将典型输入功率为3 dBm的9~15 GHz的输入信号倍频输出为功率大于15 dBm的18~30 GHz的二倍频输出信号,并且输出的二倍频信号对基波信号的抑制度可以达到30 dBc以上。倍频器芯片的尺寸为1.9 mm×1.2 mm。

关键词:GaAs;PHEMT;倍频器;芯片;谐波抑制

中图分类号:TN771 文献标识码:A 文章编号:2096-4706(2020)23-0025-04

Design of Second Frequency Multiplier Chip Based on 90 nm GaAs PHEMT Process

REN Xuan

(The 14th Research Institute of China Electronics Technology Group Corporation,Nanjing 210013,China)

Abstract:Based on 90 nm GaAs PHEMT process,a second frequency multiplier chip is designed,and the performance of the chip is evaluated by the probe station. The input frequency of the frequency multiplier chip is 9~15 GHz and the output frequency is 18~30 GHz. The chip circuit contains of an input and output two-stage driver amplifier,a second frequency multiplier and a band-pass filter,which can double the input signal of 9~15 GHz with a typical input power of 3 dBm to the output signal of 18~30 GHz with a power greater than 15 dBm,and the suppression of the output second frequency multiplier signal to the fundamental signal can reach more than 30 dBc. The size of the frequency multiplier chip is 1.9 mm×1.2 mm.

Keywords:GaAs;PHEMT;frequency multiplier;chip;harmonic suppression

0 引 言

经过了多年的发展和完善,目前无线通信技术已经成为人们生产生活中不可或缺的关键技术之一,对促进经济社会发展具有无可替代的重要作用。随着信息容量的不断扩大,传统的频段范围越来越难以满足日益增长的通信要求,而毫米波频段具有更宽的频谱范围和更大的信息容量,可以很好地解决目前存在的诸多难题。毫米波领域现在已经成为研究的热点领域,受到各国科研单位的重视。伴随着微波频段的不断提高,通信系统对振荡器的要求也随之提高。倍频器可以将频率较低的本振信号进行倍频处理从而得到高频的信号,这就大大降低了对振荡器的设计要求,研究倍频器对于提升通信系统的整体性能具有重要意义。倍频器在雷达系统、电子战以及其他通信系统中都有着大规模的应用,基于此笔者设计了一款高性能倍频器。一般而言,在电路中利用半导体器件的非线性特性就可以实现倍频效果[1,2],本文中使用的二极管倍频器就是基于这个原理工作的。

1 倍频原理

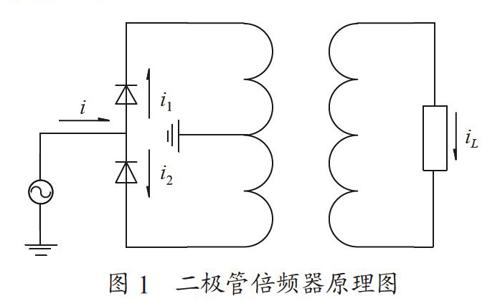

一般的,只要是具有非线性特性的半导体器件都可以实现频率变化的功能从而出现倍频效果。在实际工程应用中一般都要求倍频电路有一个较宽的频带和相对较高的效率,因此为了保证倍频电路的性能,经常将非线性电导器件作为实现倍频功能[3]的主要元器件。二极管结构简单,价格也相对较低,是一种使用范围非常广泛的半导体器件,二极管也经常被用于倍频电路之中。理论上讲只要将二极管接入电路中便可以通过它的非线性特性产生倍频效果,在实际工程应用中出于倍频效率的考虑,二极管倍频电路经常采用二极管对的布局形式。如图1所示,这种由二极管对构成的倍频电路在提高了倍频效率的同时也加强了对基波以及其他奇次谐波部分的抑制[4,5]。

图1中的倍频电路由一个反向的二极管对和巴伦结构构成。如图1所示,输入信号首先通过一对极性方向相反的二极管对,随后通过一个巴伦结构,最后在输出端就可以得到一个倍频信号。由于二极管对中的二极管极性相反,所以这两个二极管并不是同时导通的,它们是在信号的正负两个周期时分别处于导通状态。在此将通过两个二极管的电流分别设为i1和i2,二极管的反向饱和电流设为Is,根据二极管的特性i1和i2用公式可以分別表示为:

i1=Is[e-αν-1] (1)

i2=Is[eαν-1] (2)

式中ν=Vcos(ωt),α= 。

其中,V为电压,ω为角频率,t为时间,n为理想因子,K为玻尔兹曼常数,T为绝对温度。

根据i1和i2,输出的电流iL可以表示为:

iL==is[cos(αV)-1] (3)

可以将cos(αV)进行级数展开,可以得到:

iL=i0-Is+2[incos(nωt)] (4)

根据式(4)可以看出输出的电流中只有偶次分量,而不存在奇次分量。这种结构是实现偶次倍频的一种理想结构,本文中的二倍频器就是基于这种结构设计的。

2 芯片结构及设计

2.1 芯片结构

本文基于90 nm GaAs PHEMT工艺制作了一个二次倍频器芯片,它可以处理9~15 GHz范围内的输入信号,使其频段倍频至二倍,并且输出信号对基波有着较高的抑制度。

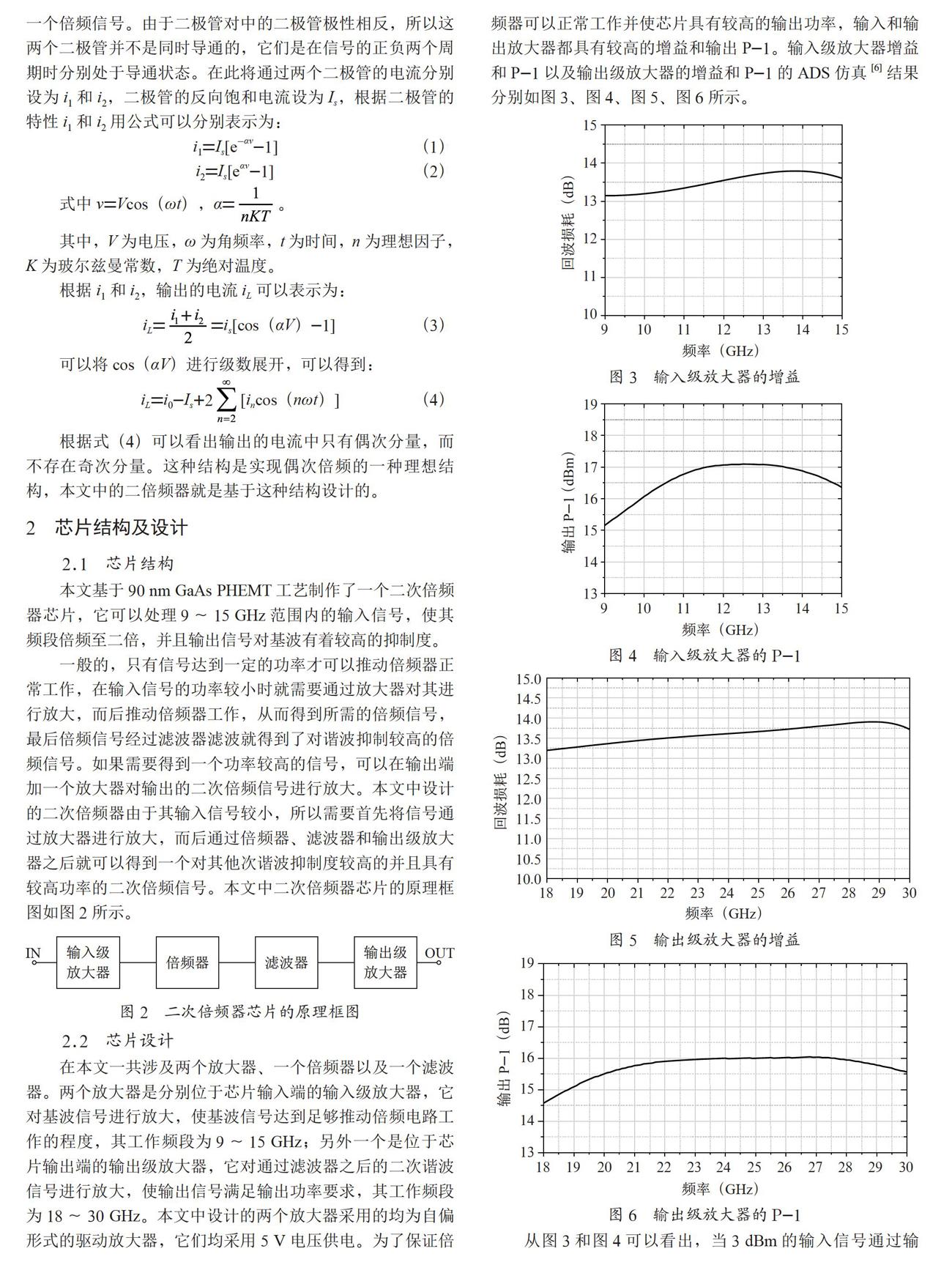

一般的,只有信号达到一定的功率才可以推动倍频器正常工作,在输入信号的功率较小时就需要通过放大器对其进行放大,而后推动倍频器工作,从而得到所需的倍频信号,最后倍频信号经过滤波器滤波就得到了对谐波抑制较高的倍频信号。如果需要得到一个功率较高的信号,可以在输出端加一个放大器对输出的二次倍频信号进行放大。本文中设计的二次倍频器由于其输入信号较小,所以需要首先将信号通过放大器进行放大,而后通过倍频器、滤波器和输出级放大器之后就可以得到一个对其他次谐波抑制度较高的并且具有较高功率的二次倍频信号。本文中二次倍频器芯片的原理框图如图2所示。

2.2 芯片设计

在本文一共涉及两个放大器、一个倍频器以及一个滤波器。两个放大器是分别位于芯片输入端的输入级放大器,它对基波信号进行放大,使基波信号达到足够推动倍频电路工作的程度,其工作频段为9~15 GHz;另外一个是位于芯片输出端的输出级放大器,它对通过滤波器之后的二次谐波信号进行放大,使输出信号满足输出功率要求,其工作频段为18~30 GHz。本文中设计的两个放大器采用的均为自偏形式的驱动放大器,它们均采用5 V电压供电。为了保证倍频器可以正常工作并使芯片具有较高的输出功率,输入和输出放大器都具有较高的增益和输出P-1。输入级放大器增益和P-1以及输出级放大器的增益和P-1的ADS仿真[6]结果分别如图3、图4、图5、图6所示。

从图3和图4可以看出,当3 dBm的输入信号通过输入级放大器以后可以将其功率提升至15 dBm以上,这足以保证其可以推动倍频电路部分正常工作。从图5和图6可以看出,当通过倍频器和滤波器之后的信号通过此放大器以后可以保证输出的二倍频信号有较高的输出功率。

本文中设计的倍频芯片电路采用的是无源巴伦和二极管对的形式,该形式可以将输入的基波信号进行倍频处理,倍频至所需的二次倍频信号。根据倍频原理部分对倍频电路的分析和相关的公式推导可知输入信号经过倍频器以后在输出信号中将只存在信号的偶次谐波分量,这是在理想的情况才可以下成立的。由于在实际工程中电路并不能达到完全的理想平衡状态,输出信号中依然会存在奇次谐波分量,在实际工程操作中可以通过加入一个带通滤波器进行滤波,从而得到一个对其他次谐波抑制度都较高的二次倍频信号。

3 测试结果

本文中设计的芯片可以使用探针对裸芯片按照设计要求进行整体评估测试,根据指标要求在此给出不同输入功率下的输出功率曲线、输入功率为3 dBm时的基波和二次谐波功率、输入功率为3 dBm时不同温度下的二次倍频输出功率、输入回波损耗和输出回波损耗的实际测试结果。

从图7中可以看出,当输入信号的功率在1~10 dBm的范围内变化时输出的二倍频信号的值均保持在14.5 dBm以上,并且当输入信号的功率达到5 dBm以上时输出的二倍频信号功率可以保持在一个较为稳定的范围内。通过上述分析,该倍频器芯片具有一个比较宽的输入功率范围和相对较高的输出功率值。

从图8可以看出当输入功率为3 dBm输入时输出的基波功率和二次谐波功率相差很大,输出的二次谐波的功率可以到达15 dBm以上,而基波的功率基本上都在-15 dBm以下,二次谐波对基波的抑制度在9~15 GHz整个频段内都可以到30 dBc以上,表明该芯片具有较高的谐波抑制度。

从图9可以看出当输入功率为3 dBm时输出的二次谐波功率在高温125 ℃时会有一些下降,不过在整个频段范围内还可以保持14 dBm以上的较高输出功率值,在常温25 ℃和低温-55 ℃时输出的二次倍频功率值均在15 dBm以上。该倍频器在高温125 ℃、常温25 ℃和低温-55 ℃状态下均可以保持较高的二次倍频输出功率。

图10和图11给出了不同温度下(高温125 ℃、常温25 ℃和低温-55 ℃)该芯片的输入回波损耗和输出回波损耗。从图10可以看出对输入信号而言,在常温25 ℃下该芯片的输入回波损耗在大部分频带内保持在-20.0 dB以下,最差的也在-17.5 dB左右;在高温125 ℃和低温-55 ℃的情况下回波也均保持在-15.0 dB以下;从图11可以看出对于输出信号而言,不管在高温125 ℃、常温25 ℃还是低温-55 ℃下该芯片的输出回波损耗在大部分带宽内都保持在-20.0 dB以下,在频带高端处回波损耗的指标略差,但是也基本上可以保持在-10 dB以下的水平。

4 结 论

本文中基于90 nm GaAs PHEMT工艺中研制了一款二次倍频器芯片,该芯片布局结构紧凑,尺寸为1.9 mm×1.2 mm。该倍频器芯片內包含了输入级放大器电路、倍频器电路、滤波器电路和输出级放大器电路,它可以将输入的9~15 GHz的基波信号倍频至18~30 GHz的二次倍频信号,并且当输入信号的功率值为典型输入功率3 dBm时,该倍频器芯片可以将输入信号的功率从3 dBm提升至15 dBm以上。该倍频器芯片在保证可以得到一个较大的二次倍频信号的同时其基波抑制度也同时达到了30 dBc以上,并且在高温、常温和低温状态下均有良好的输入和输出回波损耗。

参考文献:

[1] YU L T,CHEN P Y,WANG H. A broadband PHEMT MMIC distributed doubler using high-pass drain line topology [J].IEEE Microwave Wireless Components Letter,2004,14(5):201-203.

[2] JUNG D Y,PARK C S. A Low-Power,High-suppression V-band Frequency Doubler in 0.13um CMOS [J].IEEE Microwave and Wireless Components Letters,2008,18(8):551-553.

[3] KALLFASS I,TESSMANN A,MASSLER H,et al. Balanced active frequency multipliers for W-band signal sources [C].IEEE European Microwave Integrated Circuits Conference Symp,2011:101-104.

[4] 王凯.X波段倍频器研究与设计 [D].成都:电子科技大学,2010.

[5] 陈茄.超宽带有源倍频器MMIC的设计 [D].成都:电子科技大学,2009.

[6] 徐兴福.ADS2008射频电路设计与仿真实例 [M].北京:电子工业出版社,2009.

作者简介:任璇(1980—),女,汉族,安徽巢湖人,工程师,本科,毕业于武汉理工大学,研究方向:微波芯片发展。