基于虚拟仪器的数字电路实验系统设计

2020-07-08张商州刘爱军刘菘

张商州,刘爱军,刘菘

(商洛学院 电子信息与电气工程学院,陕西商洛 726000)

数字电路作为电类专业的专业基础课程,对学生的理论学习和实验操作都有较高的要求,也是很多专业课程的先行课程。通常数字电路的授课过程是先理论再实验,部分学生较难将理论与实验相结合,再加上实验课程大多为验证性实验,所以实验效果往往不是很好[1-3]。如果在上课过程中能够结合虚拟仿真技术,讲授过程中及时对各种逻辑关系、组合逻辑电路、时序逻辑电路等进行演示,使得课堂教学更加直观、简单,为传统教学方式开辟新的路径[4-5]。鉴于此,本文基于LabVIEW仿真软件设计了数字电路实验系统,摆脱了传统实验仪器的束缚,通过软件前面板更为直观地展示各类数字电路输入与输出之间的逻辑关系,使学生更好地理解各个门电路和集成芯片的功能。目前,该实验系统已应用在《数字电路与逻辑设计》教学过程中,大大地提高了学生的学习兴趣,帮助学生更好地理解和记忆数字电路的逻辑功能,在学生中反响较好。

1 实验系统总体设计

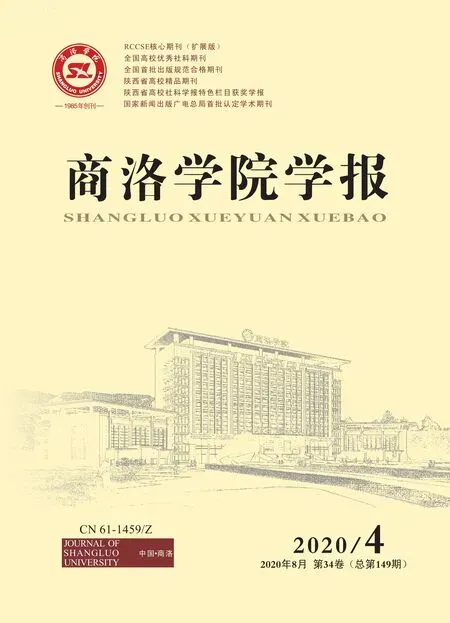

实验系统主要由组合逻辑电路、时序逻辑电路和综合设计电路实验组成,其主界面如图1所示。

图1 数字电路实验系统设计界面

其中组合逻辑电路实验中包括基本逻辑门电路(与门、或门、非门、与非门、或非门、同或门和异或门)、全加法器、译码器、编码器等,时序逻辑电路主要包括触发器、寄存器和计数器,这两部分主要借助LabVIEW中布尔模块对电路的原理、组成、功能进行直观演示;综合设计电路实验包括表决器、逻辑函数实现和码制转换器,这部分主要将多种电路芯片进行结合使用,培养学生设计与创新能力,教师也可根据学生授课实际对仿真演示内容进行相应的替换。

2 实验系统子模块设计

以基本逻辑电路、数据选择器、同步JK触发器和表决器为例,从程序框图的设计、前面板的设计以及扩展应用为例对实验系统的子模块进行举例说明。

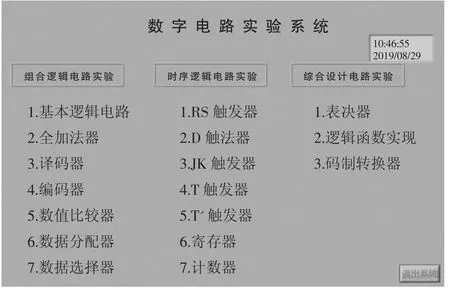

2.1 基本逻辑电路的仿真实现

基本逻辑电路主要对三种基本的门电路和四种组合逻辑门电路进行了演示操作,输入用开关按钮表示,输出用指示灯表示,“亮”表示高电平,“灭”表示低电平,学生可直观地看出输入与输出之间的关系,为后续学习奠定良好基础。系统设计的演示面板见图2(a),程序框图见图2(b)所示。

图2 基本逻辑电路的前面板和程序设计

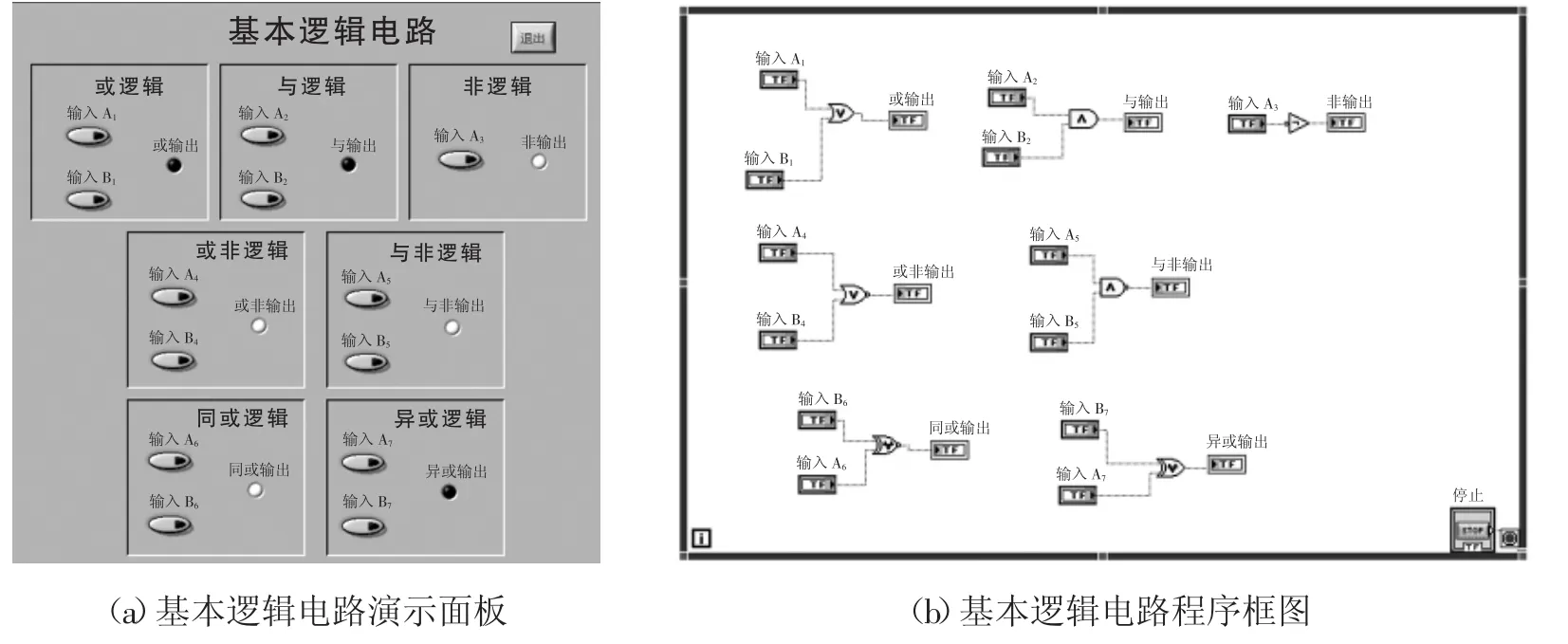

2.2 数据选择器的仿真实现

以4选1数据选择器为例,其输出逻辑函数表达式为[6]:

输入信号为4路数据,用D0、D1、D2、D3表示,在软件中用开关按钮实现;两个选择控制端,用A0、A1表示,用开关按钮实现;输出信号用Y表示,用圆形指示灯表示,它可以是4路输入数据中的任意一路,主要由选择控制端进行选择。设计完成后前面板如图3(a)所示,根据逻辑表达式在程序框图中利用逻辑门电路实现各部分之间的连接,如图3(b)所示。

如图3所示,选择控制端A1A0置10,输出Y与输入数据D2保持一致,此时D2=1,输出Y也为1。

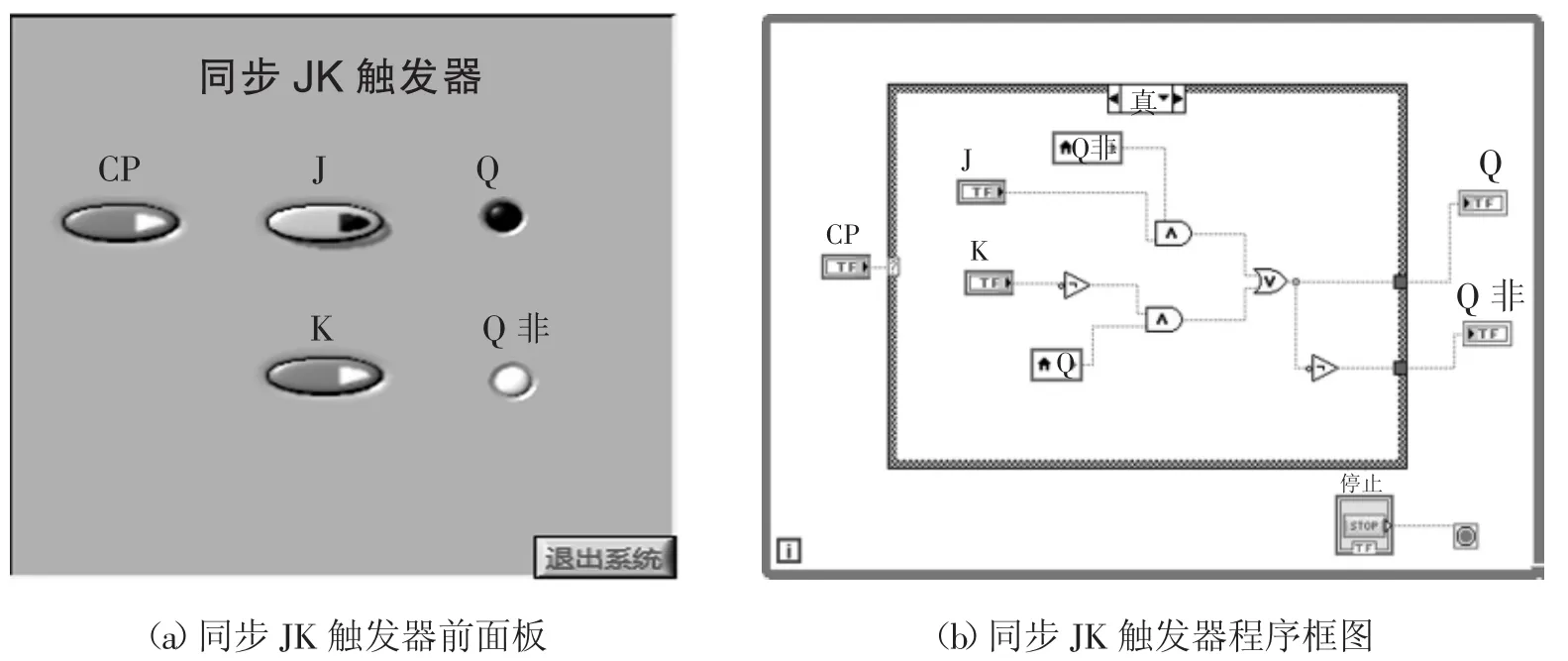

2.3 同步JK触发器

触发器是构成时序逻辑电路的基本电路,其具有两个自行保持的稳定状态,能够根据不同输入信号置成1或者0状态。常见的触发器按逻辑功能的不同分有RS触发器、D触发器、JK触发器、T触发器和T'触发器,按照电路结构形式的不同分为基本触发器、同步触发器、主从触发器和边沿触发器等[7-9],本文以同步JK触发器为例进行设计说明。

对于同步JK触发器,当JK=00时处于保持状态,Qn+1=Qn;当JK=01时处于置0状态,Qn+1=0;当JK=10时处于置1状态,Qn+1=1;当JK=11时处于翻转状态,;同时对于同步触发器,当CP=0时,触发器状态保持不变,只有当CP=1时,次态由JK的取值和现态决定。鉴于此,同步JK触发器采用条件分支结构来实现,若CP为真,则,在条件分支中利用逻辑门实现;若CP为假,则保持原状态输出。

设计完成后前面板如图4(a)所示,程序框图如图4(b)所示。如图4所示,CP=1,JK=01,此时输出Q为0,为1。

图3 数据选择器的前面板和程序设计

图4 同步JK触发器的前面板和程序设计

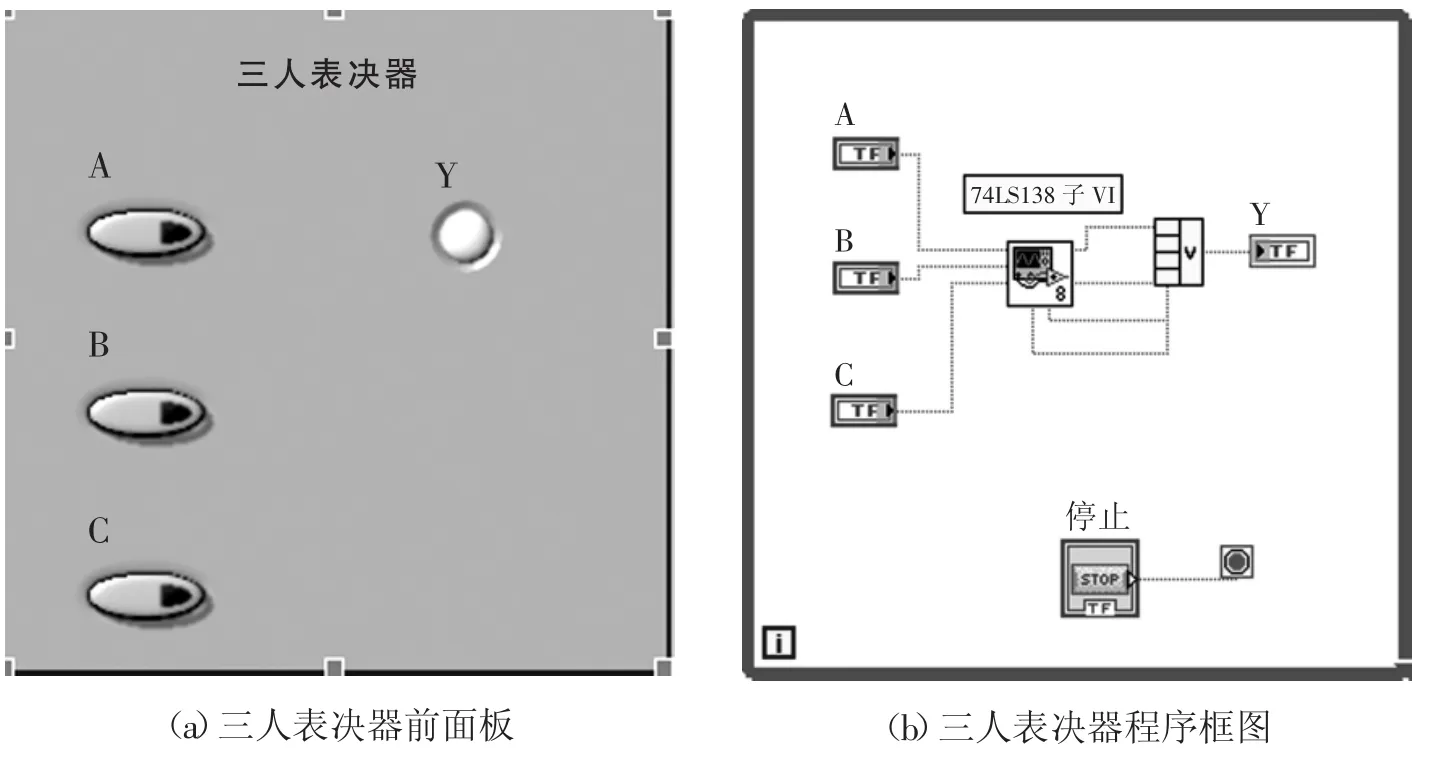

2.4 表决器的设计

表决器在数字电路设计中属于最常见的设计,可以用基本逻辑函数实现、74LS138实现、74LS151实现等[10-11],主要考察学生对理论知识的应用能力,本文以74LS138为例进行三人表决器的设计与LabVIEW实现说明。首先进行逻辑抽象,三个评委分别用A、B、C表示,同意为“1”,不同意为“0”,表决结果用Y表示,当三人中有两个或三个同意时表决通过输出Y为“1”,否则Y为“0”,则可得到表决器的输出为:

A=A2,B=A1,C=A0,则Y=Y3+Y5+Y6+Y7。

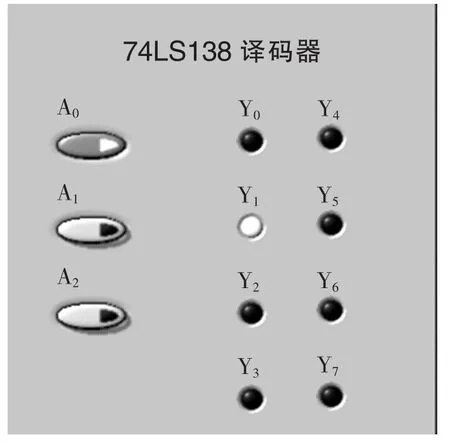

由于LabVIEW中没有现成的74LS138芯片模块,所以首先要根据该芯片输入与输出的关系在软件中建立模型并生成子VI[12],为了分析方便所设计74LS138输出为高电平有效,如图5所示。

图5 74LS138译码器

在表决器电路中调用74LS138译码器子VI,三个表决端分别接A2、A1、A0,译码器输出中 Y3、Y5、Y6、Y7接入一个四输入或门,或门输出即为表决结果,具体电路图见图6所示。

图6 三人表决器的前面板和程序设计

通过本系统的设计,一方面可以使学生掌握74LS138实现逻辑函数的基本原理,另一方面也巩固学生对逻辑电路设计方面的知识,通过最终生成的EXE文件使学生更加直观地看到显示的结果。

3 结论

在进行数字电路理论教学过程中,通过引入图形化编程软件LabVIEW,替代常规的纯理论讲授,更加直观地展现了数字电路的实现过程与结果,激发了学生学习兴趣。其次,学生也可利用课后自行在LabVIEW中进行数字电路地搭建,实现理论教学与实验教学的平滑过渡,使实验不在局限于实验室,也可以使学生对各个电路的内部原理有更深刻地认识,提高了授课效率,降低了实验成本,为理论教学提供更简洁、易懂的仿真。