基于FELIX的微结构气体探测器读出电子学系统设计

2020-06-16元光远沈仲弢水雁斌刘树彬

元光远,沈仲弢,*,王 宇,水雁斌,刘树彬

(1.核探测与核电子学国家重点实验室,中国科学技术大学,安徽 合肥 230026;2.中国科学技术大学 近代物理系,安徽 合肥 230026)

微结构气体探测器(micro-pattern gas detector, MPGD),如GEM(gas electron multiplier)[1]、THGEM(thick GEM)[2]、Micromegas[3]等,因其面积大、时间空间位置分辨率高等优点,在粒子物理、天文观测、核医学等领域有广阔的应用前景[4-5]。在未来MPGD的应用中,通常要求读出电子学系统具备可裁剪性好、通道规模大(数十路至上万路)、数据总带宽高(1 Gb/s以上)、工作灵活性好、适应不同ASIC(application specific integrated circuit)等特点。如在升级后的ATLAS中,MPGD通道数将达到2×106,数据率将达到1 Tb/s量级[6]。在预研中的中国环形正负电子对撞机(Circular Electron Positron Collider, CEPC)中,通道数将达到百万路,数据率也将达到100 Gb/s量级[7]。

FELIX(frontend link exchange)系统具有工作方式灵活、可扩展性高、数据带宽大、兼容性好等优点,能满足MPGD对于读出电子学系统的需求[8]。针对MPGD对读出电子学的需求,本文提出一种基于FELIX的MPGD通用电子学系统的整体架构方案,设计实现可完成4 096路AGET模拟通道读出或10 240路MICROROC半数字通道读出的电子学系统,并与探测器一起进行宇宙线径迹探测,以验证该设计方案的可行性。

1 读出电子学系统设计

1.1 系统架构

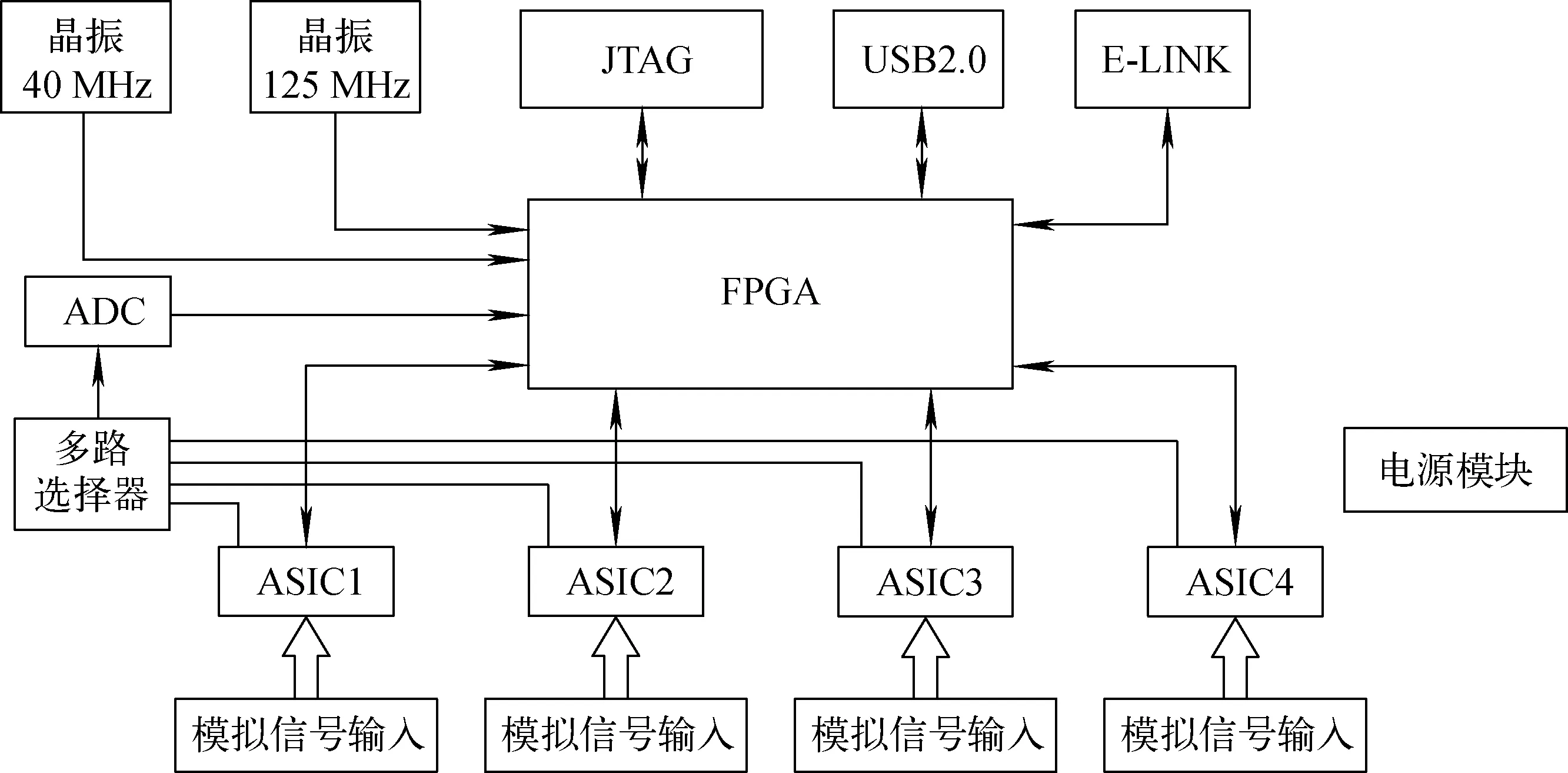

面向MPGD的通用读出电子学系统框图如图1所示,由完成探测器模拟信号数字化的前端模块,完成多个前端模块与FELIX卡之间数据汇总的GBT模块,完成数据读出的FELIX系统,以及完成系统控制、数据存储和离线数据处理的数据处理终端(DAQ)系统组成。

前端模块主要用于完成探测器输出信号调理以及数字化。为减少长距离传输带来的噪声等问题,前端模块安装在探测器上,在探测器前端完成数字化。根据具体应用需求,前端模块可搭载不同的ASIC芯片,并在设计上适应探测器信号、机械接口等具体需求。本文采用基于AGET的模拟读出前端模块以及基于MICROROC的半数字读出前端模块完成系统联调。

GBT模块功能为利用分时复用构建虚拟通道完成多个前端模块与FELIX卡之间的数据传输[9]。本文设计的GBT板可通过RJ45电接口或SFP光纤接口与前端电子学完成数据传输,分别可完成20块基于MICROROC的前端模块或8块基于AGET的前端模块读出。

图1 面向MPGD的通用读出电子学系统框架Fig.1 Architecture of scalable readout electronics system for MPGD

FELIX系统是读出电子学系统数据采集与数据处理终端的数据节点[8,10]。FELIX系统采用PCIE接口、光纤传输等高速数据传输技术,最大带宽可达百Gb/s。同时提供分时复用建立虚拟通道的解决方案,可满足多通道的需求。目前,FELIX可完成2块GBT板的数据读出,未来FELIX卡升级后可完成24块GBT板的数据读出。

数据处理终端通过商用网络技术与FELIX系统通信,完成系统控制、数据存储、数据处理等。

该架构的核心设计思想是由硬件搭建从前端电子学模块到软件的高带宽透明硬件通道,由软件根据实际的应用需求完成相应的功能,因此通用性好,对不同的前端ASIC芯片、应用场景、工作模式具有很好的兼容性。同时该架构采用分时复用方案搭建虚拟通道,可扩展性好,可满足MPGD对多通道数的需求。

1.2 前端电子学模块设计

1) 基于MICROROC的前端电子学模块

MICROROC(MICRO mesh gaseous structure readout chip)芯片由法国Omega小组于2010年设计[11]。每块MICROROC芯片可完成64路半数字通道读出,动态范围为1~500 fC。基于MICROROC的前端模块设计如图2所示[12]。其前端与探测器相连的接口采用80针、50 mil(1 mil=0.025 4 mm)间距的ERNI-154744连接器,以实现高密度读出。每个模块集成4片MICROROC芯片共256通道用于探测器信号读出,最大数据率为20 Mb/s。其与GBT板之间采用RJ45电传输,由3对传输速率为160 Mb/s的差分线组成,包括由GBT板传输的1路时钟、1路数据,以及发送到GBT板的1路数据。前端模块主控芯片为Xilinx A7 FPGA,完成整个模块的系统控制。

图2 基于MICROROC的前端模块设计框图Fig.2 Diagram of MICROROC chip carrier

噪声水平是衡量电子学性能的重要指标。本文采用S型曲线测试得到的MICROROC通道噪声如图3所示,其中横坐标是噪声水平,纵坐标是落在该噪声范围内的通道数。结果表明,大部分通道噪声不超过0.2 fC,满足MPGD读出需求。

2) 基于AGET的前端电子学模块

AGET(ASIC for general electronics for time projection chambers,面向时间投影室的通用ASIC芯片)由法国Scalay实验室在AFTER芯片的基础上研制而成[13]。每块AGET可完成64通道模拟信号采集,每路电子学通道前端集成了电荷灵敏放大器(CSA)、滤波成形电路、由512个开关电容构成的环形存储阵列以及甄别触发电路。

图3 基于MICROROC的前端模块噪声Fig.3 Noise of MICROROC chip carrier

图4为基于AGET的前端模块设计框图,每个前端模块集成4片AGET芯片,可完成256路电子学通道的读出[14]。探测器信号经AGET芯片完成波形采样后,由ADC芯片AD9522完成波形数字化。前端模块与GBT板之间采用光纤传输,链路速率为400 Mb/s,其中有效数据率为200 Mb/s。基于AGET的前端模块将光纤链路恢复出的时钟作为系统时钟,从而实现与GBT板时钟同步。该模块主控芯片为Xilinx A7 FPGA。

图4 基于AGET的前端模块设计框图[14]Fig.4 Diagram of AGET chip carrier[14]

在没有输入时,采用随机触发对各电子学通道的信号进行采集可完成噪声测试。图5所示为AGET通道噪声,噪声均不超过0.4 fC,满足MPGD读出需求。

图5 基于AGET的前端模块噪声Fig.5 Noise of AGET chip carrier

1.3 GBT模块设计

图6 GBT模块设计框图Fig.6 Diagram of GBT module

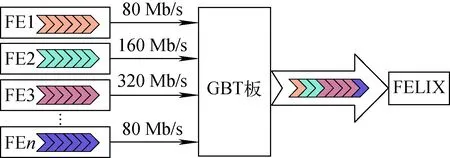

GBT模块是前端模块与FELIX卡之间的数据通道,GBT模块设计框图如图6所示。GBT模块与FELIX卡之间通过光纤链路完成数据传输,链路传输速率为4.8 Gb/s,用户数据率为3.2 Gb/s。该链路称为GBT link。GBT板与前端模块之间的链路称为Elink[15],分别设计基于RJ45电传输和基于SFP光纤传输的Elink,用于完成MICROROC前端模块和AGET前端模块的数据读出。1个GBT模块最多可完成20个基于MICROROC的前端模块数据读出,或8个基于AGET的前端模块数据读出。GBT模块的核心功能由Xilinx K7-410T FPGA完成,其主要功能利用分时复用将高速的GBT link数据通道分成多路相对低速的前端电子学模块数据通道,如分成40路80 Mb/s Elink、20路160 Mb/s Elink或10路320 Mb/s Elink。

作为GBT模块的主控模块,FPGA逻辑主要功能为利用分时复用建立虚拟通道[16],完成多个前端电子学模块与FELIX系统之间的数据通信,其设计框图如图7所示。该逻辑GBT作为透明的数据通道,前端模块可近似看成直接与FELIX卡完成数据传输。GBT板与FELIX卡之间的数据传输采用GBT frame编码,该编码方式可完成1位误码修正、2位误码检测功能。在面向MICROROC前端模块的逻辑设计中,Elink物理层采用RJ45接口电传输、160 Mb/s Elink数据通道,可实现20个MICROROC前端模块的数据读出。面向AGET前端模块的逻辑设计中,Elink物理层采用SFP接口光纤传输、320 Mb/s Elink数据通道,每个GBT板可实现8个AGET前端模块的数据读出。

图7 GBT逻辑设计框图Fig.7 Diagram of GBT logic

此外,逻辑中还集成了1个慢控制模块,可完成软件复位、工作模式切换、状态监测等功能。GBT板从FELIX接收时钟作为系统时钟,同时通过Elink下发时钟到前端模块中,实现整个系统的时钟同步。

对基于RJ45电传输和基于SFP光纤传输的Elink通道开展12 h的双向误码率测试,传输速率分别为320 Mb/s和400 Mb/s,未发现误码,在置信度90%的前提下可认为误码率分别小于2.9×10-13和2.3×10-13。对GBT link开展24 h的双向误码率测试,传输速率为4.8 Gb/s,未发现误码,在置信度90%的前提下可认为误码率小于1×10-14。

1.4 FELIX系统

FELIX系统是为ATLAS升级而设计的数据获取系统。其设计目标在于成为前端读出电子学与大型商业网络之间的通用数据路由系统。1个FELIX系统由1个带PCIE接口的服务器(FELIX Server)及1块被称为FELIX卡(FELIX card)的PCIE扩展卡组成。目前常用的FELIX卡有FLX709和FLX712。FLX709是基于Xilinx开发板VC709实现的FELIX卡,以Virtex7 FPGA为主控芯片,集成了4路SFP+光纤接口作为与前端电子学之间的数据链路,以及PCIE GEN3 Lane×8接口作为与FELIX服务器之间的数据通道[10]。FLX712由布鲁克海文国家实验室设计,采用Virtex Ultrascale+FPGA作为主控芯片,采用PCIE Gen3 Lane×16作为与FELIX服务器之间的数据通道,共48路miniPOD光纤接口可完成与前端电子学之间的数据传输[17]。

设计使用Xilinx的开发板VC709作为FELIX卡。经测试,FELIX卡与FELIX服务器之间的平均传输带宽可达44 Gb/s。

2 探测器联调结果

宇宙线径迹探测平台由上、下各1层作为符合探测器的塑料闪烁体探测器、6层完成宇宙线信号探测的Micromegas探测器以及相应的读出电子学构成。当粒子穿过探测器装置时,上、下的塑料闪烁体探测器给出触发信号,Micromegas探测器完成宇宙线粒子探测,由电子学系统读出Micromegas探测器信号,即可实现宇宙线粒子探测。Micromegas探测器由中国科学技术大学设计制造,灵敏区面积为150 mm×150 mm,工作气体为93%Ar与7%CO2混合气体,二维条读出,条间距为400 μm,每维有384路探测器信号,6层12个维度共4 096路探测器通道。

2.1 应用MICROROC前端模块的测试结果

基于MICROROC的前端模块为半数字读出型前端板,适应超大规模读出通道数。因此在该系统中,采用直接读出。每个MICROROC chip carrier可完成256路通道读出,6层探测器共需18块MICROROC板4 096路电子学通道。图8为记录的1次宇宙线事例。每条黑色线为每维的击中位置,两条黑线的交叉处即为宇宙线击中的探测器位置。将6层探测器击中位置拟合直线,就可得到宇宙线穿过探测器的径迹。

图8 应用MICROROC重建的宇宙线径迹Fig.8 Rebuilt cosmic track applying MICROROC

2.2 应用AGET前端模块的测试结果

基于AGET的前端模块采用位置编码读出方式[18-19],1个维度384路探测器通道需1个AGET芯片64路电子学通道完成读出,6层探测器共使用4个基于AGET的前端模块,12块AGET芯片共768路电子学通道完成数据读出。

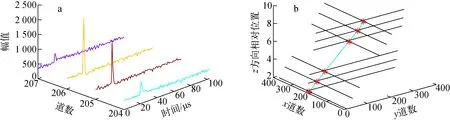

基于AGET的前端模块为波形采样读出,可得到宇宙线事例的波形、峰值、上升沿等信息。图9a为1次宇宙线事例中1个维度的探测器通道采集到的探测器信号,图9b为重建的宇宙线径迹。利用基于AGET前端模块采集到的信号峰值信息可得到宇宙线能谱,其中1个维度的宇宙线能谱如图10所示,符合朗道分布。

图9 基于AGET采集到的波形以及重建的宇宙线径迹Fig.9 Waveform of cosmic ray event and rebuilt cosmic ray track applying AGET

图10 宇宙线能谱Fig.10 Cosmic ray spectrum

3 总结与讨论

设计了1套面向MPGD的通用可扩展读出电子学系统架构,该架构支持通道数多、对不同的前端ASIC芯片支持好。采用适用于MPGD的AGET和MICROROC两款芯片,完成了数字读出和模拟读出的原型系统设计,并利用电子学原型系统与Micromegas探测器完成了宇宙线径迹探测。该系统工作方式灵活、通用性好、兼容性好、可扩展性好,可很好适应MPGD的读出需求。对于未来规模更大的读出需求,也可采用FLX712进行系统升级来满足。

向为本文电子学系统设计提供帮助的布鲁克海文国家实验室的陈虎成、陈凯、邬维浩以及提供Micromegas探测器的中国科学技术大学的张志永致谢。