PandaX-nT暗物质探测实验读出电子学预研系统的研制

2020-06-16王淑文沈仲弢封常青刘树彬

王淑文,沈仲弢,*,王 硕,封常青,刘树彬

(1.核探测与核电子学国家重点实验室,中国科学技术大学,安徽 合肥 230026;2.中国科学技术大学 近代物理系,安徽 合肥 230026)

暗物质模型[1]是解释宇宙结构的关键理论之一,已在天文学相关实验与理论[2-4]中预言了其存在性。国际上,多个实验组均在开展相关的暗物质直接探测实验,如意大利的XENON实验[5]、美国的LUX实验[6]等。在中国,PandaX系列实验[7]是利用氙作为探测介质的暗物质直接探测实验。PandaX实验位于中国锦屏地下实验室,利用气液二相型氙时间投影室(time projection chamber,TPC)技术直接探测暗物质重要的候选粒子——弱相互作用重粒子(weak interactive massive particle,WIMP)[8-9]。当入射粒子与TPC中氙原子发生作用,将电离氙原子并激发氙原子产生闪烁信号(S1信号);而电离氙原子产生的电子在TPC中电场作用下,产生电致发光信号(S2信号)。S1信号与S2信号的宽度取决于电子扩散尺度和TPC中氙气的厚度,S1信号的宽度一般在几十ns,而S2信号则一般弥散在1 μs左右的时间窗口内[10-11]。同时,在1 keVee能量下,S1信号为几个PE,而S2信号则为S1信号的50~100倍,最小的S2信号在百PE左右[11]。

PandaX实验经过了一系列升级,其中PandaX-Ⅰ和PandaX-Ⅱ均取得了重要的科学成果[12-16]。为进一步提高暗物质探测的灵敏度,PandaX实验将进一步升级为PandaX-nT实验。PandaX-nT实验TPC中液氙质量将达到4 t,光电倍增管(PMT)数量也增加到512路;未来将升级到30 t,PMT数量也将达到上千路。在PandaX-Ⅰ和PandaX-Ⅱ实验中,主要通过计算S2信号与S1信号的比值实现对主要本底和信号的甄别;此外还可通过粒子和电子的S1信号的PSD(pulse shape discrimination)进行本底甄别。但受限于PandaX-Ⅱ商业FADC采样率(100 MS/s)问题,几十ns级别的波形无法完成[11]。因此,PandaX-nT的升级还要求读出电子学能对S1信号进行高速、高精度的采样(>500 MS/s),从而进一步研究PSD算法来提高探测灵敏度[17-20]。由于PandaX-nT探寻的是稀有事例,运行时事例率约为3 Hz[10],但考虑到需对整个系统进行刻度,而电子源刻度时事例率为30 Hz[10],因此需读出电子学触发率至少为30 Hz,以保证整个系统的正常运行。同时为兼容基于网络的数据控制系统[21],电子学系统应采用以太网传输数据。最后还要具有较高可扩展性,能适应以后更大规模的读出需求与触发需求。这对整个读出电子学系统提出了挑战,需读出电子学能进行高速高精度波形采样(>500 MS/s),同时能实现不同的触发算法需求,满足触发率和相应的带宽需求,并有较高的可扩展性,而以往的基于商业插件的读出系统不能满足现有需求,需研制新的读出电子学系统。本工作拟设计与研制PandaX-nT读出电子学预研系统。

1 读出电子学结构

基于PandaX-nT的升级对电子学提出的挑战,整个读出电子学采用模块化思想设计,便于设计与扩展。读出电子学系统如图1所示,其主要由前置放大电路模块、波形数字化模块(FDM)、数据获取模块(DAQ)和时钟分发模块等模块组成。前置放大电路模块主要用于将PMT输出的信号放大,以提高信噪比。FDM模块采用1 GS/s 14 bit的高速高精度的ADC对放大后的PMT信号进行波形数字化,以满足PandaX-nT对于PSD算法研究的需求;同时单个FDM集成8路ADC,具有较高的集成度。DAQ则采用基于纯数字化的触发判选,能灵活实现多种触发算法;通过光纤汇总来自FDM的数据,方便扩展;并通过以太网与服务器进行通信,同时以太网部分兼容千兆和万兆两种以太网协议,便于根据不同触发算法选择合适数据带宽。时钟分发模块则主要用于分发同步时钟,保证整个系统的同步性。

图1 读出电子学预研系统基本结构示意图Fig.1 Block diagram of readout electronics pre-reasearch system

a——第1级差分放大;b——第2级运算放大图2 前置放大电路图Fig.2 Pre-amplification circuit diagram

1.1 前置放大电路模块

根据PandaX-nT PMT信号特征,前置放大电路模块需10倍增益,-3 dB带宽为250 MHz,如图2所示。前置放大电路主要由两级级联放大器构成,第1级差分放大电路为2倍增益,由于-3 dB带宽为250 MHz,因此要求差分放大器增益带宽积至少为500 MHz;同时为保证信号不失真,差分放大器压摆率要好于200 V/μs。综合以上考虑,差分放大器选用了Texas Instruments(TI)公司的THS4520,此芯片在2倍增益下带宽为450 MHz,压摆率为570 V/μs,满足实验的需求。第2级运算放大器设计增益为5倍,在满足增益的要求下,选用TI公司的LMH6629芯片,此芯片具有噪声低、压摆率高等优点。最后,通过两级级联10倍放大后的信号再经过输出驱动电路,通过同轴线缆传输至FDM模块,从而减小了通过线缆传输过程中噪声的干扰,提高了输入信号的质量。

1.2 FDM

为满足PSD算法研究的需求,综合功耗和通道集成度的考虑,FDM采用Analog Devices(ADI)公司的1 GS/s 14 bit的ADC——AD9680。AD9680是基于JESD204B的双通道ADC,具有较高的集成度。1 GS/s的采样率不仅满足现有PSD算法研究的需求,同时保证了ADC单通道功耗较低,有利于系统设计。且AD9680峰峰值量程为1.94 V,与PandaX使用的商业插件量程相当,能满足PMT信号的动态范围需求。由于FPGA需支持JESD204B高速串行协议和光纤传输,因此选用Xilinx Kintex 7 系列FPGA XC7K420T。XC7K420T具有至少24条高速串行链路,能保证单个FDM模块集成4片AD9680,同时还有多余的高速串行链路用于光纤传输。且XC7K420T具有42万门逻辑资源和丰富的片内RAM资源,能满足FDM逻辑设计需求。FDM模块还集成了兼容JESD204B协议的Jitter Cleaner PLL——LMK04610,用于产生ADC所需的高精度时钟和JESD204B所需的SYSREF信号。

FDM采用PXI 6U标准板卡设计,结构框图如图3所示。FDM主时钟源是时钟扇出模块提供的25 MHz同步时钟,然后通过模块内PLL Q产生ADC的采样时钟、FPGA的工作时钟和用于JESD204B协议的SYSREF同步信号,从而保证了整个前端采集系统的时钟的同步性。由SMA输入的前放信号,经过FDM内部运算放大器转换成差分信号,并经过低通滤波器滤除运放带来的高频噪声后,输送到AD9680。每片AD9680采样后的数据通过4条10 Gb/s的JESD204B链路汇总到FPGA中。在FPGA中,通过来自DAQ的触发信号,将触发窗口内的有效数据全部存储在FPGA内部RAM中,其余数据丢弃;存储后的有效数据,经添加时间戳、触发号等信息后,重新组装成完整的数据帧,并通过光纤将此数据帧上传到DAQ中。

图3 FDM结构框图Fig.3 Block diagram of FDM

1.3 DAQ

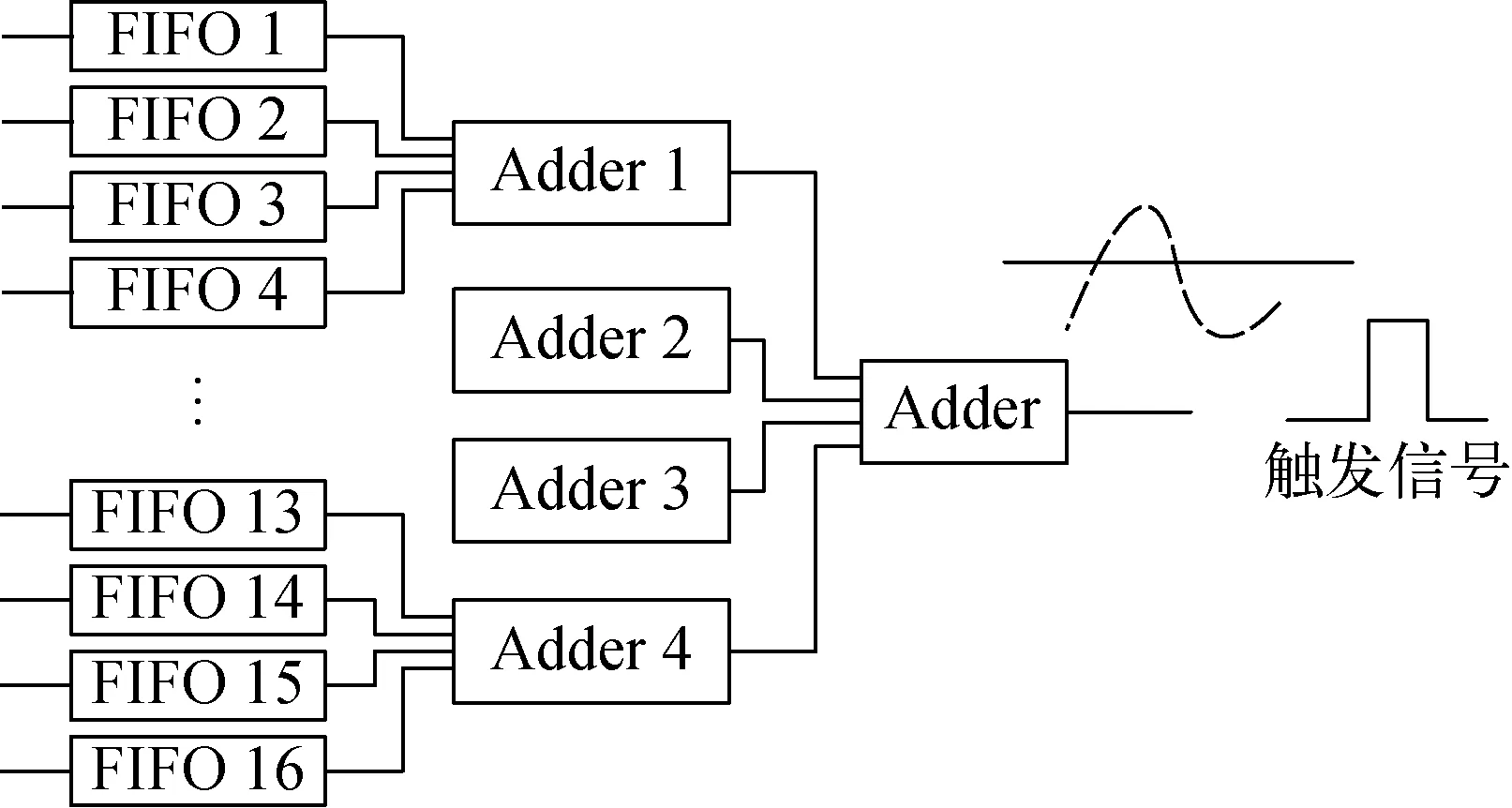

DAQ用于汇总来自FDM的数据和分发触发信号,其结构框图如图4所示,每个DAQ主要由光纤收发器、Xilinx XC7K420T FPGA、DDR和以太网收发器等组成。每个DAQ有16路光纤收发器,能汇集并控制来自16个FDM的数据,汇总的数据先缓存在模块内的DDR存储中,然后通过以太网和交换机传输到服务器集群。每路光纤收发器通过FPGA高速串行接口,恢复FDM模块传输的数据。恢复的FDM数据包含每个通道的击中信息,通过触发判选算法,产生触发信息,并通过光纤将触发信息再发送给FDM。

图4 DAQ结构框图Fig.4 Block diagram of DAQ

DAQ数据汇总框图如图5所示。由于光纤链路延迟的不确定性,会造成不同FDM通道击中信息到达时刻不一致。因此,在FPGA中,通过弹性缓冲区消除光纤链路的延迟不确定,保证击中信息的同时性。接收到的FDM数据,先通过FPGA内部弹性缓冲区消除通道之间的延迟后,进入到数据FIFO中;然后DAQ将多个通道的数据,添加帧头、帧尾、时间戳等信息后,重新组装成数据帧,并将组装好的数据帧存储到DDR中,然后通过以太网传输。

图5 DAQ数据汇总框图Fig.5 Block diagram of data collection of DAQ

1.4 基于数字化的触发判选方案

为实现有效事例的筛选,剔除噪声的干扰,需对探测到的信号进行触发判选。在预研系统中,触发系统采用基于数字化的触发判选方案。纯数字化的触发判选方案,可充分利用FPGA内部强大的逻辑资源,实现各种可重构的触发算法。

在预研系统的验证阶段,触发算法主要基于全局过阈触发,其框图如图6所示。FDM通过采集PMT信号,将8路波形信息进行积分,积分后的结果通过抽取,传输到DAQ;DAQ通过FPGA内部FIFO汇总来自16个FDM的波形信息,然后通过流水线结构将所有的波形信息进行积分求和,得到最终的波形信息;最后,通过调整合适阈值,使S1和S2信号积分后的波形均能分别过阈,从而得到最终的触发信号,并将此触发信号和当前的时间戳信息通过光纤下发到各FDM。FDM在接收到DAQ的触发信息和时间戳后,将窗口内2 μs的数据打上时间戳后,重新组帧,上传到DAQ,最终汇总到服务器。由于在TPC中,S1信号和S2信号之间的时间差代表着逃逸电子的漂移时间,并且S1信号总是先于S2信号触发,因此对离线数据利用时间戳信息能区分S1信号和S2信号。

图6 触发算法框图Fig.6 Block diagram of trigger system

单个DAQ能容纳128路通道信号,因此对于PandaX-nT升级实验,512路通道信号需4个DAQ。同时,预研系统还利用额外的1块DAQ,汇总其余4个DAQ触发信息,最后根据512路通道信号产生最终的触发信号,并通过其余4个DAQ分发到FDM。

1.5 基于以太网的高速数据传输

在PandaX-nT实验中,由于通道数较多,同时采用高速高精度波形数字化技术,因此要求DAQ具有较高的数据传输速率。而以太网正满足这种高带宽需求。同时为保证数据传输的可靠性,需采用可靠的传输层通信协议TCP。

以太网实现框图如图7所示,在FPGA中实现以太网和TCP协议的具体过程。以太网物理层(PHY)实现是通过实例化FPGA内部高速串行收发器,将千兆以太网1 Gb/s串行数据流串并转换成125 MHz、8 bit并行数据。以太网PHY层并行数据通过GMII接口,与TCP协议处理IP核SiTCP相连。SiTCP[22]是日本KEK电子学组专门为物理实验开发设计的处理TCP协议的IP核。SiTCP IP核中,包含了以太网MAC协议层和TCP协议处理层。SiTCP中TCP协议的实现如图8所示。当计算机(客户端)需通过以太网与SiTCP(服务端)通信时,先通过3次握手建立1条可靠的连接通道,即:计算机首先向SiTCP发送1个SYN请求建立连接;然后当SiTCP接收到SYN后,向计算机发送1个确认信息SYN/ACK,表示允许建立连接;最后当计算机接收到SiTCP发送的SYN/ACK后,再次向SiTCP发送1次确认信息ACK,表示已正确接收到SYN/ACK信号。此后,计算机与SiTCP直接建立1条数据连接通道,用于后续的数据传输。在数据传输阶段,SiTCP将DDR中存储的有效数据通过前面建立的数据通道,上传到计算机中,当计算机正确接收到数据帧后,向SiTCP发送1条正确接收的确认信号ACK;只有当SiTCP接收到来自计算机的确认信号ACK后,才开始下一次传输,否则就认为上一次传输失败,从而重新发送上次的数据帧,直到计算机正确接收到为止。通过这种传输、确认、出错重传的机制保证数据传输的可靠性。

图7 以太网实现框图Fig.7 Block diagram of implementation of Gigabit Ethernet

由于有确认信息ACK的传输,基于TCP的千兆以太网有效传输速率并不能达到1 Gb/s,经测试,实际平均速率约600 Mb/s。对于PandaX电子源刻度信号,触发率为30 Hz。在采用S1、S2单独过阈触发算法下,每个过阈信号的时间窗为2 μs,因此对于1路通道信号,1次触发产生2 μs×14 bit/Sample×1 GS/s,即28 kbit数据。对于S1信号和S2信号,则1次有效事例数据为56 kbit。因此,对于1个DAQ,128路通道信号在触发率为30 Hz条件下,数据率为56 kbit×128×30 Hz,即210 Mb/s。因此基于TCP的以太网协议能满足数据传输的带宽要求。

图8 SiTCP数据传输框图Fig.8 Block diagram of data transmission of SiTCP

图9 前置放大电路增益和带宽测试结果界面Fig.9 Interface of gain and bandwidth test results of pre-amplifier

2 系统测试

整个系统的测试由整个读出电子学的性能测试和与探测器系统的初步联合测试构成。

2.1 读出电子学的性能测试

1) 前置放大电路模块性能测试

前置放大电路性能测试主要测试前置放大电路的增益和带宽,同时还要验证其噪声性能的好坏。增益和带宽的测试是利用信号源输入一定频率的正弦信号,测试其输出结果,通过输入输出的对比,得到其实际增益和带宽结果。噪声测试是在无输入的情况下,测试输出的噪声幅值计算放大电路的信噪比。

图9为前置放大电路模块增益和带宽的测试结果界面。从图9可看到,当输入信号幅度峰峰值为120 mV时,放大电路输出结果为1.2 V,增益为10倍,而-3 dB带宽为256 MHz,满足设计需求。图10为噪声测试的结果界面。在没有输入情况下,放大电路模块输出噪声RMS为0.422 mV,扣除示波器自身的噪声RMS 0.153 mV,计算得到放大电路模块噪声RMS为0.269 mV。

2) ADC性能测试

ADC性能测试主要分为静态性能测试和动态性能测试。静态性能测试包括微分非线性(differential nonlinearity, DNL)、积分非线性(integral nonlinearity, INL)等指标。动态性能测试主要测试ADC有效位(effective number of bits, ENOB)。

静态性能测试是通过信号源向每个ADC通道输入低频的满幅度正弦信号,然后将ADC采集到的波形数据根据ADC码值进行直方图统计分析,最后根据直方图统计结果计算分析得到ADC静态性能INL和DNL。图11所示为FDM 1个通道的静态性能测试结果,测试中正弦信号输入频率为7.9 MHz。从图11可看到,DNL结果在-0.15LSB~0.15LSB(LSB为最低有效位)之间,INL结果在-4LSB~4LSB之间。此测试结果与AD9680数据手册提供的测试结果相当,ADC静态性能正常。

动态性能测试是通过Agilent公司的高速信号发生器E4438C产生单一频率的正弦信号,经带通滤波器后输入到FDM的ADC通道,最后通过分析ADC采集到的正弦波信号的频谱图计算ENOB。表1列出FDM上8个通道的测试结果。从表1可看到,除通道8由于距离PCB板上数字部分较近,性能低于其余通道外,其余通道在250 MHz频率输入范围内,有效位均好于9.40 bit。AD9680手册指标为10.7 bit@170 MHz,这是由于FDM前端是采用有源器件直流耦合,导致信噪比低于数据手册。

图10 前置放大电路噪声测试结果界面Fig.10 Interface of noise test results of pre-amplifier

图11 ADC静态性能测试结果Fig.11 Static performance test result of ADC

表1 ADC ENOB测试结果Table 1 Test result of ADC ENOB

3) 以太网传输测试

基于SiTCP的以太网测试是通过DAQ FPGA产生PRBS序列,然后通过SiTCP发送到计算机;计算机通过以太网接收来自DAQ的PRBS序列,并校验,来测试整个以太网的稳定性与传输速率。通过长时间测试,基于SiTCP以太网正常传输,并未出现错误,测试中,基于SiTCP的以太网平均速率约为600 Mb/s,满足整个读出电子学系统的需求。

2.2 与探测器的初步联合测试

为检验整个读出电子学对探测器实际S1、S2信号的获取能力以及整个读出系统的稳定可靠性,在中国锦屏地下实验室利用PandaX-Ⅱ TPC探测器验证整个读出电子学性能。

1) 单光子标定测试

由于PMT的不一致性,相同信号PMT在同一工作高压下,其增益也会有一定差异,因此需对其增益进行标定。单光子标定测试中,利用发光二极管(LED)的弱光模式标定。整个测试流程如下:通过控制提供给LED的电流信号,使LED工作在弱光模式下,间断产生光子。PMT的光阴极吸收1个光子并发射1个电子,通过后续打拿极的倍增后,最终倍增电子被阳极获取;PMT产生的信号最终被读出电子学采集。

采集到的单光子信号减去基线后,在一定窗口对波形信号进行积分,从而得到单光子标定结果。图12所示为探测器中1个通道的标定结果。图中左侧较高的峰是台基,对应着读出电子学接收到LED外触发,但PMT未接收到光子;右侧的峰代表单光电子峰。两个峰值之间的差值即为PMT增益。从图12可看到,测得的通道增益为391.5道,与PandaX-Ⅱ以往标定结果相当。

图12 单光子标定结果Fig.12 Test result of single photon calibration

2) 探测器信号测试

为检验读出电子学对S1、S2信号的获取能力,关闭PandaX-Ⅱ TPC探测器LED后,对探测器信号进行采集。图13所示为1次探测的结果。从图13可清晰看到信号的S1峰与S2峰,表明整个读出电子学工作正常。

3 总结

本文针对PandaX-nT升级实验设计完成了读出电子学预研系统。该读出电子学预研系统包括前置放大电路模块、集成8通道的高速高精度FDM、集成16路光纤通道和基于以太网传输的DAQ和时钟分发模块等模块。目前,已完成了整个电子学读出系统的性能测试,并与探测器进行了初步联合测试,验证了读出电子学系统的性能指标,为后续进一步完善和扩展做好了准备。

图13 探测器信号测试结果Fig.13 Test result of detector signal