基于FPGA 控制的高速Nandflash 阵列存储模块设计

2020-06-04葛进

葛进

(上海都森电子信息科技有限公司,上海201102)

1 项目概况

该型高速Nandflash 阵列存储模块是为雷达遥感设备配套的科研项目,项目总体设计要求该存储模块设计达到:a. 满足高速存储和大容量存储要求。在目前新型的雷达遥感系统中,由于多通道的高频采样,将实时生成大量的数据,为防止宝贵的数据因吞吐率不足而丢失,存储器必须以较高速率传输数据和进行存储,供后续算法分析或回放显示使用;b. 满足存储设备体积限制和抗冲击震动要求。雷达一次观测采集数据可能持续较长时间,这就需要尽可能应用体积小密度高且抗冲击震动的存储介质,以保证在有限的设备空间内能存放较多的数据和具备一定的抗冲击震动性能;c. 适应试验过程中便于修改和连接其它测试设备多的要求,控制试制成本。

Nandflash 作为一种非易失性存储器,它以半导体为记忆载体,具有读写速度快、存储容量大、能承受一定的温度变化、抗机械震动和冲击的可靠性较高、易于实现低功耗和小型化等特点,同时考虑到数据存储文件在使用中需经常擦写或搬运,要求存储介质具备较高的稳定性和可靠性,因此选用可擦写次数较多,bit 误码率较少且稳定耐用的MLCNandflash 芯片作为存储介质。由于单片的Nandflash 容量有限,需通过构建Nandflash 阵列系统来满足存储容量大的使用要求[1]。

在Nandflash 的控制器的选择上,通过比较FPGA 与cpu,认为FPGA 具备较强的并行数据处理能力和丰富自定义的接口资源,因此为快速开发Nandflash 控制器,首选是使用FPGA,并辅以cpu 模式下的文件系统,达到完成对整个存储系统的控制的目的。FPGA 可反复编程和擦除,适宜设计不同的片内逻辑来实现不同的使用功能。由于FPGA 开发过程投资小,设计灵活,发现错误可直接更改设计,减少了投片的风险,节省费用[2]。

为了适应试验中便于调整和修改的需要,在过渡设计中采用分置主控、接口FPGA 不同功能的双FPGA 结构,其中的主控FPGA 集成了微处理器,作为维护系统文件之用;而接口FPGA灵活配置为多种高速接口与多种数据源相连接。这种双FPGA结构大大方便了研发过程中的调整和修改。

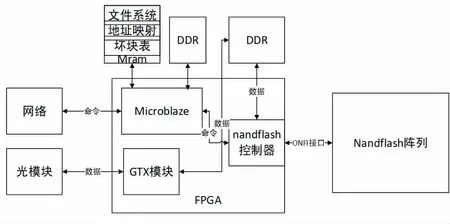

图1 存储模块系统结构图

2 Nandflash 阵列存储模块的硬件设计

存储模块包括数据采集和存储两大部分,系统的速度由这两部分的速度共同决定。硬件结构按照数据采集- 数据缓存-数据存储- 数据下传的流程进行设计,整个过程由FPGA 硬件逻辑实现。

2.1 单片FPGA 的结构形式

该型存储模块的硬件组成为单片FPGA+Nandflash 芯片阵列。FPGA 选用xilinx 公司的XC7V585T-2,Nandflash 芯片使用的是镁光公司的MT29F256G08C。

FPGA 通过专用高速模块和外部多路光纤相连,这是整个存储模块对外的数据接口;FPGA 通过硬件编程,实现原生态的ONFI 的接口与Nandflash 阵列相连,本设计中一共实现了16 路8bit 的接口。FPGA 内有一个microblaze 的cpu 核作为最高层文件系统和坏块管理控制使用,通过以太网接收上位机的用户命令[3]。存储模块的硬件结构如图1 所示。

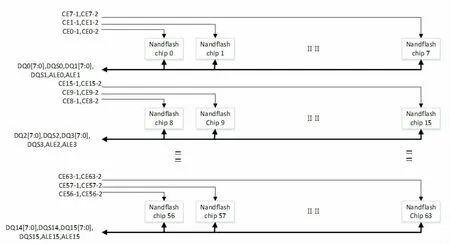

Nandflash 阵列,每行为8 个芯片,共有8 列,总共使用了64个芯片,每个芯片的接口位宽是16bit,为2 个通道,总容量2TByte。每个芯片上使用两个CE 片选使能,分别控制2 个DQ[7:0] 的数据通道接口。除了片选使能CE 以外,其他的控制信号ALE,WR,以及数据采样信号DQS,DQ[7:0]都是每行8 个芯片共享的,这样既可以精确的控制每个通道8bit 的DQ 读写,又能大幅减少管脚数量,减少布线难度,提高通讯信号质量[4]。Flash 阵列控制示意如图2 所示。

图2 Nandflash 阵列控制示意图

图3 双FPGA 结构示意图

2.2 过渡设计采用的主控FPGA+接口FPGA 的结构形式

为方便试验而采取的过渡设计中,曾采用主控FPGA+接口FPGA 的结构形式,具体是将单片FPGA 功能分解为两片FPGA的不同功能,即一个为主控FPGA、另一个为接口FPGA。结构示意见图3。

主控FPGA、接口FPGA 集成在一块PCB 板上,数据源通过高速接口与接口FPGA 连接,接口FPGA 通过原生的简易高速接口与主控FPGA 相连,主控FPGA 通过DDR 模式的闪存接口与Nandflash 阵列连接。主控FPGA 集成了微处理器、闪存阵列控制器等,可以专注完成核心记录数据的功能,对复杂的控制命令操作以及对数据处理的步骤可以适当简化;接口FPGA 发挥并行优势,做成多种接口的交换中心模式,灵活的与外部数据源相连接,从而不会因为接口的变化导致重新布局设计制版。

3 FPGA 阵列控制器传输流水节拍控制的设计

为了实现高速的数据读写,必须要求尽可能的并发数据处理[5],Nandflash 阵列共有16 个通道共128bitDQ 要同时读写。先读写第一列8 个芯片的第N 个page,然后读写第二列8 个芯片的第N 个page…以此类推,直到读写到第8 列的8 个芯片的第N 个page,然后再从第一列读写8 个芯片的第N+1 个page。

读写的接口I/O 时序方式是采用DQS 同步双沿采集DQ[6]。DQS 时钟频率高达50MHz,双沿数据采样率高达100MT/sec。这样阵列总的理论接口速率是128bitnet*100MHz=12800Mbit/sec=1.6GByte/sec。

文件系统的设计是以适应高速数据吞吐的大文件节点系统来考虑的,对整个阵列的所有通道进行一次block 操作,作为一个文件节点的操作。由于本设计采用多个Nandflash 芯片共同工作的方式,而每个芯片的最小擦除单位是block,所以因此每个文件节点容量计算方式如下:64 个芯片,每个芯片中2 个通道,每个通道最小擦除单位1 个block, 每个block 分为512 个page,每个 page 可以存储16384byte 数据 , 故64*2*1*512*16384byte=1Gbyte。

查看Nandflash 芯片手册,可以知道对于每个page 的读时间为75us, 对于每个page 的编程时间为1300us, 而使用同步100MT/s 的DQS 采样,传输一个page16384byte 需要的I/O 时间是16K/100M=160us。Nandflash 芯片在使用160us 时间收集数据到cacheregister 后,需要花大量的时间去编程Nandflashcell,由于在编程的过程中,对外显示busy,此时接口不能使用DQS 收集新的数据,所以编程所需时间就成为影响写数据速率的瓶颈。为了解决这个问题,每行设计使用8 个Nandflash 芯片,使用I/O 接口先传输第一个芯片数据耗时160us, 然后第一个芯片编程开始编程,把数据从内部cacheregister 转移到Nandflashcell,随后I/O 接口依次传输后面7 个芯片的数据,这样一行8 个芯片传输总耗时约为160us*8=1280us。这时再回到第一个芯片,而这时距离第一个芯片的编程开始时间已经过去了160*7=1120us,只要经短暂等待就会结束上一次编程时间,使第一个芯片又可以传输下一个page 的数据。这样I/O 接口的DQS,DQ 信号除了短暂的等待外,一直处于跳变工作状态,使每个芯片都处于编程的流水控制过程中,从而达到较高的传输效率。NandflashI/O接口写时间与编程写时间的流水节拍控制调度示意如图4 所示。

图4 nandflashI/O 接口写时间与编程写时间的调度示意

4 Nandflash 数据正确性处理

FPGA 内部可以产生100MHz 的时钟,并且进行2 分频成为50MHzDQS,数据可以很准确的发往Nandflash 并被存储下来,但是在读取Nandflash 数据的时候,由于线路延迟或者其他原因,Nandflash 芯片发出DQS 和DQ 在到达FPGA 时有时候不满足建立时间和保持时间条件,容易采样到误码。因此借鉴DDR 采样的方式,设计一种自动循环的延迟、采样、比对机制,来确保数据进入FPGA 被正确读取。先发送读ID 命令给Nandflash 芯片,Nandflash 芯片就会通过DQS 和DQ 将ID 返回给FPGA。使用FPGA 中的元语idelay,iddr 以某个延迟把DQS 和DQ 在时间轴上错开,用DQS 将DQ 采样下来。由于正确的NandflashID 是手册可以查到的,所以进行比对,看看读回来的ID 是否正确,如果不正确,就步进延迟,然后再采样比对,直到比对正确为止。

除了采样错误需要纠正以外,Nandflash 芯片由于工艺的限制,会有一定的bit 翻转误码,所以还要采用bch 或RS 纠错码进行ECC(错误校验码)校验。

5 坏块管理

使用的Nandflash 芯片中,包含4 个LUN(逻辑单元),而每个LUN 还包含1024 个block(块),由于工艺限制,并不是每个块都是好的,而且有些好的块经过了反复的擦写以后,也可能变为badblock(坏块)[7]。因此使用了5 个步骤来甄别坏块,减少坏块。首先,读取特定位置的出厂数据信息,标定出厂时就已经有的坏块;第二,进行初始化擦除,清空Nandflash,如果有坏块存在会返回异常,就在物理坏块表里做标记;第三,写某个page 时,如果出现写失败,也在物理坏块表里做标记;第四,如果在做ECC 时候,返回无法纠错,也在物理坏块表里做标记;第五,在文件系统节点分配的时候,做空闲节点的队列循环使用。如果最近某个文件被擦除,节点被回收成为空闲节点,会放在队列最后,队列的最前面总是指向最早空闲的节点。这样保证了不同的block 被擦写的次数相对平均,防止过量编程导致好块变为坏块。

6 Nandflash 的断电保护

为了使Nandflash 在断电再上电后仍能继续之前的操作,地址缓存在每次Nandflash 读写操作后都会更新当前地址,并将更新的地址存入Nandflash 的地址存储空间,在Nandflash 下一次读写操作开始前,把存入地址存储空间的地址读出并作为本次工作的操作地址。这样,就能使Nandflash 在断电再上电后,仍可以从地址存储空间读出操作地址,从而继续之前的操作[8]。

结束语

本文介绍了基于FPGA 控制高速Nandflash 阵列存储模块的硬件和FPGA 设计,该型存储模块针对雷达遥感系统采样频率高、采样通道多而产生数据量大的特点,给出了一种定制化程度高、实时快速数据存储模块的设计,其核心是通过FPGA 对Nandflash 芯片阵列进行读写调度和控制,不仅能使数据传输量增大,而且也能很好的保证数据的安全性。

该型存储模块成功实现了在FPGA 控制下的各种功能接口,顺畅完成了从数据采集、缓存,到实时传输存储Nandflash 阵列的整个工作流程,产品数据存储容量、数据读写速率、体积控制和抗冲击震动等性能均满足了用户的要求。今后,随着FPGA技术和元器件制造水平的不断提高,高速大存储量的控制技术将会得到更快发展,各种新型存储器也将不断涌现并将获得更广阔的应用前景。