铁路信号安全协议中消息认证码算法的研究

2020-05-18伍忠东刘菲菲

张 凯,伍忠东,刘菲菲

(兰州交通大学电子与信息工程学院,兰州 730070)

1 概述

2001年,欧盟通过立法形式确定ETCS[1]成为强制性技术规范,不仅使列车能够在欧洲各国实现互通运行,并且能够提高列车运行的安全性和实时性。作为我国CTCS-3级列控通信系统[2]的核心安全协议,RSSP-II协议[3]的安全性[4]和实时性[5]对高速铁路的运行起到了至关重要的作用,协议中消息鉴定安全层的消息认证码算法又被视为整个协议功能的核心。

提高铁路信号安全协议消息鉴定安全层核心算法的安全性和实时性是铁路信号安全协议中的研究热点,目前该协议消息鉴定安全层核心算法大多数是基于TDES或者通过传统软件方式去实现的。张启鹤提出了一种基于传统的TDES算法的消息鉴别码算法,通过在FPGA上面实现了协议核心算法的功能,提高了协议的实时性[6],A B Nasution等研究使用TDES算法保护数据的机密性和完整性[7],郭伟等从网络攻击的角度分析了协议的安全性能,并指出了目前协议的核心算法存在的安全隐患[8],Mohit Mittal等通过MATLAB软件对DES算法和AES算法的安全性能和时间性能进行了分析比较[9],张元玲等提出了一种基于AES的消息鉴别码算法,通过软件的实现方式提高了协议的安全性能[10],CHEN Lijie等利用彩色Petri网(CPN)模型对安全通信协议进行了性能分析与验证[11],和晟姣介绍了CSP方法建模工具,分析了RSSP-Ⅱ通信协议,从密钥服务流程、对等实体认证两个方面对协议进行CSP方法分析建模[12]。

目前RSSP-Ⅱ中消息鉴定安全层消息认证码算法主要是通过数据加密标准DES算法来实现,但是随着DES算法的广泛应用,其安全性和实时性方面的隐患不断出现:在安全性方面,首先DES算法存在弱秘钥、半弱秘钥问题,弱秘钥、半弱秘钥问题会导致将不同的明文加密成相同的密文,导致密码攻击者很容易破解密码进而对协议产生安全威胁,其次DES算法存在秘钥长度过短的问题,密钥长度仅为56 bit,但是随着计算机数据处理能力的快速提高,使用传统DES算法将不能有效抵抗穷举攻击,从而使得协议的安全性受到极大的威胁;在实时性方面,首先传统基于DES的消息认证码算法对最后一个分组进行3重DES(TDES)计算,会大大增加算法的执行时间,其次铁路信号安全协议中消息鉴定安全层消息认证码算法的传统实现都是基于软件进行的,相比硬件执行,软件实现在速度方面具有很大的劣势,难以保证列车在高速铁路环境下的实时性要求。

针对传统算法在安全性和实时性方面存在的上述问题,对铁路信号安全协议的安全性和时间性进行了深入研究,提出了基于高级加密标准AES算法的MASL-AES-MAC算法。该算法结合了AES加密算法的高安全性和FPGA硬件的快速实现性的优势,并对算法的硬件实现进行优化处理。通过Altera公司的Cyclone V系列5CSXFC6D6F31C6N FPGA硬件开发板的有效评估,实验结果表明:MASL-AES-MAC算法较传统的算法相比不仅具有更高的安全性,同时还缩短了算法的执行时间。

2 RSSP-Ⅱ协议MASL层概述

2.1 消息鉴定安全层概述

RSSP-Ⅱ通信协议是按照欧洲无线电功能接口标准制定的,目的是能够为数据提供安全的传输服务[13]。其中的消息鉴定安全层的功能就是通过发送方和接收方运行消息源安全验证程序,为数据传输中消息的真实性和完整性提供安全保障,并且同时保障消息发送方的不可伪造性。

发送方验证:

输入:消息M,发送方A和接收方B的共享密钥Ks,源地址SA、目的地址DA。

处理流程:

(1)发送方A的方向标志设为0,接收方设为1。

(2)在消息M前附加消息M的目的地址(DA):DA|M。

(3)计算步骤2所生成字符串的长度L(八字节),并将该长度(2个八位字节)附加到该字符串之前,格式为:L|DA|M。

(4)判断消息(L|DA|M)的长度,若字符串长度不是64的整数倍,则在字符串后面按照通信双方的规定进行填充数据P,从而构成新字符串:L|DA|M|P。

(5)用共享密钥Ks对字符串进行CBC-MAC[14]算法:MAC(M)=CBC-MAC(Ks,L|DA|M|P)。

输出:将MAC(M)值附加在消息M上并发送给接收方B。

接收方验证:

输入:方向标志,包含MAC(M)的消息M,发送方A和接收方B双方共享密钥Ks,源地址SA、目的地址DA。

处理流程:

(1)在消息M前附加消息M的目的地址(DA):DA|M。

(2)计算步骤2所生成字符串的长度L(八字节),并将该长度(2个八位字节)附加到该字符串之前,格式为:L|DA|M。

(3)判断消息(L|DA|M)的长度,若字符串长度不是64的整数倍,则在字符串后面按照通信双方的规定进行填充数据P,从而构成新字符串:L|DA|M|P。

(4)用共享密钥Ks对字符串进行CBC-MAC算法:MAC’(M)=CBC-MAC(Ks,L|DA|M|P)。

(5)比较MAC(M)和MAC’(M)是否相等。

输出:若MAC(M)=MAC’(M),则证明消息没有被进行篡改且确信消息M由发送者A发送,反之则消息M已被篡改或伪造。

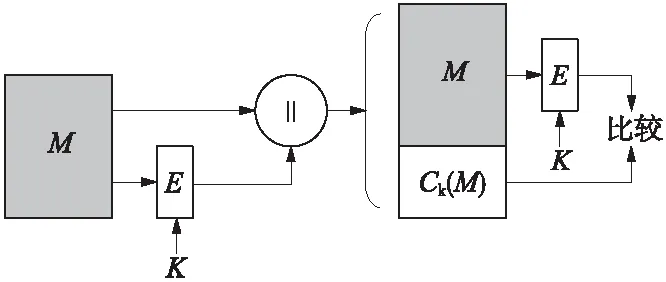

图1为消息认证模型。其中E表示对消息M用密钥K进行加密生成Ck(M),||表示对消息M和Ck(M)进行合并发送。

图1 消息认证模型

高速铁路应用中,RSSP-Ⅱ中消息鉴定安全层认证码算法的实时性,主要是指通信认证双方通过消息认证码算法产生MAC认证码进行认证时的及时性,即实时性。消息认证码算法产生MAC认证码的速度关乎发送方和接收方对于通信双方消息源安全验证程序的快慢,从而为数据传输中消息的真实性、完整性和可用性提供保障。若消息认证码算法产生MAC认证码的时间超出通信双方认证所设定的超时重传时间间隔的最大值,则通信双方认证失败。所以尽量缩短消息认证码算法产生MAC认证码的时间,提高算法的实时性,对于提高RSSP-Ⅱ协议的性能显得尤为重要。

2.2 CBC-MAC算法概述

CBC-MAC算法是基于分组密码算法,并且工作在分组密码的密码分组连接链CBC(Cipher Block Chain)模式下的消息认证码(Message Authentication Code,MAC)[14]。消息认证码是将消息M使用一个密钥,底层通过分组密码方式加密产生一个特定长度的数据分组。MAC类似于加密,但区别是MAC函数无需是可逆的,图2为分组密码工作在密码分组连接链CBC模式下的流程。

图2 分组密码的密码分组连接链模式流程

3 MASL层MAC算法的改进及优化

3.1 改进的基于AES的MASL-MAC算法

3.1.1 AES算法硬件设计

AES算法属于分组密码算法,采用Verilog HDL语言先对底层加密算法AES采用了自底向上的模块化设计思路,模块化的设计思路方便后续的顶层模块整合和对算法的优化处理。本文设计的AES算法FPGA[15]硬件实现主要包括5个子模块,分别是字节代换模块、行移位模块、列混合模块、轮密钥加模块和秘钥扩展模块[16-17]。

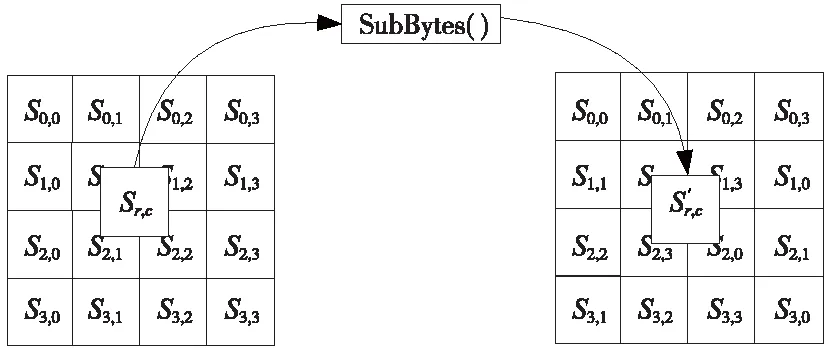

(1)字节代换模块

字节代换是一个非线性变换,目的是将输入或者中间状态的字节通过查表操作映射为另一个字节。映射具体办法是将输入字节高4位作为S盒[18]的行值,低4位作为列值,最后将该行值和列值所对应的元素作为代换结果输出。例如十六进制数0x6D,则对应S盒的行值是6,列值是D,则对应在S盒之后的结果是0x3C。

S盒是一个由16*16字节构成的矩阵,包括了每个字节的8位值所能表达的256种可能的变换。S盒的设计构造方法有如下3个步骤。

Step1:把每一行字节值按照升序进行排列来初始化S盒。第一行是{00},{01},{02},…,{0F};第二行是{10},{11},…,{1F}等。在行X和列Y的字节值是{xy}。

Step2:把S盒中的每个字节映射为它在有限域GF(28)中的逆,{00}被映射为它自身{00}。GF(28)由一组从0x00到0xFF的256个值组成,加上加法和乘法运算。

Step3:对于S盒中的每个字节都记作为(b7,b6,b5,b4,b3,b2,b1,b0)。然后对S盒中每位做如下变换:

b(i+7)mod 8⊕ci

(1)

图3 SubBytes()实现非线性置换

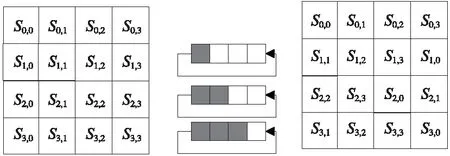

(2)行移位模块

ShiftRows()的设计主要是完成基于行的循环移位操作。即行移位变换作用在中间态的行上,其中第0行不变,第一行循环左移1个字节,第二行循环左移2个字节,第三行循环左移3个字节[19]。图4为ShiftRows()完成循环移位操作示意。

图4 ShiftRows()完成循环移位操作

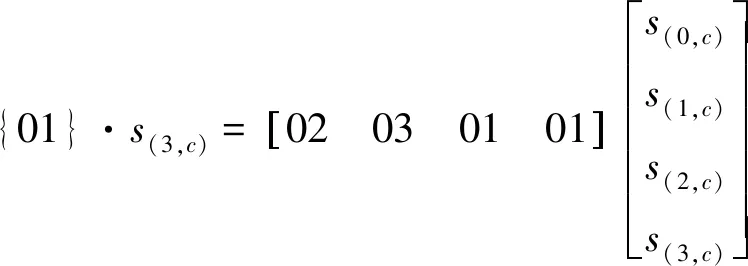

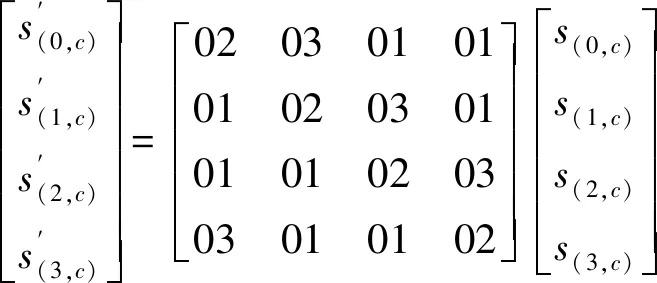

(3)列混合模块

MixColumns()是对每一列进行逐列混合,其具体方法是:

s′(x)=c(x)·s(x)mod(x4+1)

(2)

式(2)中,

c(x)={03}·x3+{01}·x2+{01}·x+{02}

(3)

式(3)中{}内的数表示的是字节

s(x)=s(0,c)+s(1,c)·x+s(2,c)·x2+s(3,c)·x3

(5)

ximod(x4+1)=ximod 4

(6)

可得

{02}·s(0,c)+{03}·s(1,c)+{01}·s(2,c)+

(7)

其余类似,因此,式(7)可用矩阵表示为式(8),图5为MixColumns()列变换示意。

(8)

图5 MixColumns()列变换示意

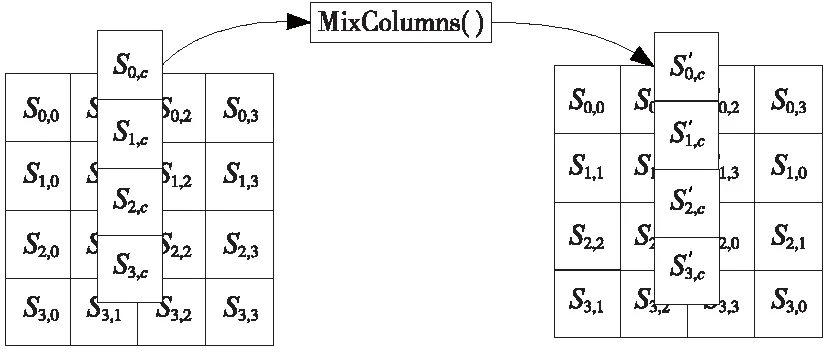

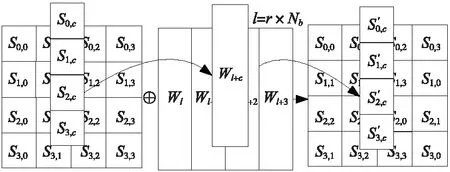

(4)轮密钥加模块

AddRoundKey()的目的是将输入或中间状态S的每一列与相对应的一个密钥字Ki进行按位异或,即AddRoundKey(S,Ki)=S⊕Ki,其中Ki(i=0,1,…,10)是由初始密钥K通过密钥扩展算法产生的。每一个轮密钥由4个字组成,W[r*Nb+c]表示第r轮的第c个轮密钥字[20]。图6为AddRoundKey()变换示意,轮密钥加具体的变换表达式为

[w(r·4+c)]

(0≤r≤10,0≤c≤4)

(9)

图6 AddRoundKey()轮密钥加变换示意

(5)密钥扩展模块

密钥扩展模块的功能是为每一轮的AES加密提供轮密钥。通过生成器产生Nr+1个轮密钥,每个轮密钥由Nb个字组成,共有Nb*(Nr+1)个字W[i](其中i=0,1,…,Nb*(Nr+1)-1)。其中Nb和Nr分别代表中间态的列数和迭代轮数[20]。虽然AES可以使用的密钥大小有3种,分别是128 bit、192 bit和256 bit,但是由明文分组的大小为128 bit,所以本文选择密钥大小和明文分组大小相等的128 bit。

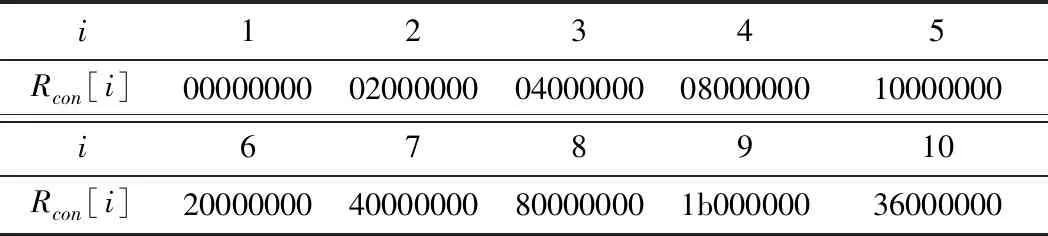

在加密过程中,需要用到Nr+1个轮密钥,需要构造4×(Nr+1)个32位字。前十个轮常量Rcon[i]的值(用十六进制表示)如表1所示。

表1 Rcon[i]数据

对于AES-128,AES密钥扩展算法的输入是4个字(每个字32 bit,共128 bit)。输入密钥直接被复制到扩展密钥数组的前4个字中,得到W[0]、W[1]、W[2]、W[3],剩下的41个字W[i]则由W[i-1]和W[i-4](i>=4)来共同决定,根据不同i值,则有不同的算法。

对于W数组中下标不为4的倍数的元素,采用如下计算方式

W[i]=W[i-1]⊕W[i-4]

(10)

对于W数组中下标为4的倍数的元素,计算方式如下4个步骤:

Step1 RotWord():目的是把输入的4个字节循环左移一个字节,即把字(b0,b1,b2,b3)变为(b1,b2,b3,b0);

Step2 SubWord():基于S盒对输入字(Step1的结果)中的每个字进行S盒替换;

Step3 将Step2的结果再与轮常量Rcon[i/4]相异或;

Step4 将Step3的结果再与W[i-4]异或。

3.1.2 改进的基于AES算法的MASL-MAC算法硬件实现

MASL-MAC算法(MASL层使用的MAC算法)是基于AES的一种更安全变形。输入信息M被分割为P1、P2、…、Pn,若切割后最后一个消息分组块不足128位,则用0补齐。使用AES算法以秘钥Ki加密128位的分组块的过程表示为AES(Ki,Pi),⊕表示异或运算最后输出的MAC值由公式(11)得出

H0=0;

Hi=AES(K,Hi-1⊕Pi),i=1,2,…,n;

MAC=AES(K,Hn-1⊕Pn);

(11)

本文提出的MASL-MAC算法是以AES加密算法为基础,工作在分组链接链(Cipher Block Chain,CBC)状态下的消息鉴别码。本节MASL-MAC算法的FPGA硬件设计采用Verilog HDL语言进行了模块化的设计思路。MASL-AES-MAC算法结构如图7所示。

图7 MASL-AES-MAC算法结构

分组加密算法的特点是明文和秘钥的长度都是固定的,比如DES算法的明文为64位,AES算法的明文分组长度为128位。本文中MASL-AES-MAC算法是基于AES算法的,所以当整个输入消息M的长度不为128的整数倍时,即需要对最后一个不满128位的数据分组块进行Padding补位处理,使其长度达到128位,具体补充处理数学表达式如下

(12)

式(12)中,M_Last为最后一个不足128位的分组块,i代表需要在其后面所加0的个数,r为分组块M_Last所表示的以8位大小为单位的向量的个数,r∈[0,16)。

3.2 对MASL-AES-MAC算法的优化

本文提出的基于高级加密标准AES的MASL层MAC认证码改进算法,但是按照AES基本原理直接在FPGA逻辑电路上实现,会造成大量的逻辑资源浪费,并且效率不高。所以在对核心算法改进的基础之上对改进算法进行进一步的优化处理,使得在获得更高数据吞吐率的情况下尽可能地减少FPGA逻辑资源的消耗,最终获取更高的效率。

3.2.1 轮代换模块优化

本文之前对AES算法的10轮代换模块的设计主要有由4个模块构成,分别是字节代换模块、行移位模块、列混合模块和轮密钥加模块。

结合3.1.1节AES算法硬件设计的数学基础,假设单个轮变化的输入为状态a,字节变换的过程用Sb表示,经字节变换的输出为状态b,经行移位变换的输出为状态c,经列混合之后的输出为状态d,i和j分别表示每个状态矩阵的行和列,则有

bi,j=Sb[ai,j]

(13)

(14)

字节代换模块是每一轮变换的第一步操作,经过分析发现字节代换模块是非线性的字节置换,可以构造一个查找表来实现字节代换的功能,从而避免大量的异或运算和乘法运算。其次轮变换的第二步是行移位模块,是一个循移位操作,是将字节代换模块输出的结果按照行移位之后的顺序进行排列。

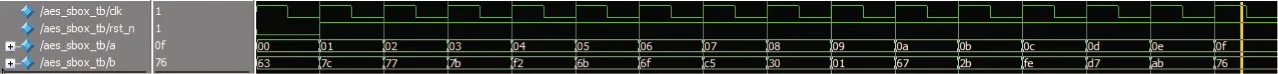

为了减少单独进行字节代换和行移位变换的资源消耗,对这两个模块进行合并操作处理。首先通过预算的方式,计算出所有字节代换的8位输入数据对应的8位输出数据,然后将这个输入数据的高4位作为行值,低4位作为列值,将输出的8位数据作为具体的元素值,最后构成一个16×16的S盒查找表。S盒模块的仿真如图8所示。

图8 S盒模块仿真结果

从图8可以看出,当S盒模块输入信号a为8’h0f且复位信号为高电平时,在时钟上升沿的输出信号b为8’h76,与理论值一致。同理,其他仿真结果均与理论值一致,仿真正确。

当进行字节替换和行移位时,将输入状态矩阵a的每个字节的高4位作为行值,低4位作为列值,取出对应的元素值,输出顺序按照行移位模块的输出顺序输出,这样就完成了字节代换和行移位模块的功能,同时减少了逻辑资源的消耗。

(15)

其中,0≤j

d(0,j)=02·c(0,j)⊕03·c(1,j)⊕c(2,j)⊕c(3,j)

d(1,j)=c(0,j)⊕02·c(1,j)⊕03·c(2,j)⊕c(3,j)

d(2,j)=c(0,j)⊕c(1,j)⊕02·c(2,j)⊕03·c(3,j)

d(3,j)=03·c(0,j)⊕c(1,j)⊕c(2,j)⊕02·c(3,j)

(16)

其中d(i,j)为变换后的状态矩阵d的第j列,按照AES算法数学基础,可得

03·X=(02⊕01)·X=02·X⊕X

(17)

由式(17)可知,式(16)可以转换为式(18)

d(0,j)=

02·c(0,j)⊕(02·c(1,j)⊕c(1,j))⊕c(2,j)⊕c(3,j)

d(1,j)=

c(0,j)⊕02·c(1,j)⊕(02·c(2,j)⊕c(2,j))⊕c(3,j)

d(2,j)=

c(0,j)⊕c(1,j)⊕02·c(2,j)⊕(02·c(3,j)⊕c(3,j))

d(3,j)=

(02·c(0,j)⊕c(0,j))⊕c(1,j)⊕c(2,j)⊕02·c(3,j)

(18)

上述运算都是在GF(28)上进行的,在FPGA硬件实现中,加法运算等效为异或运算,而乘法运算则要分为两种情况:若字节的最高位为0,则与02做乘法运算时只需将字节左移一位即可;若字节的最高位为1,则与02做乘法运算时,将字节先左移一位之后再与字节1B进行异或运算。

在有限域中,所有元素都可以写成02不同幂次的和,所以所有常数的乘法都可以通过分解之后进行多次与02的乘法和异或运算实现。考虑到为了减少算法硬件实现的运算量,对于有限域中一个字节与02乘法运算的256种可能的结果用一个16×16的M盒查找表替换,这样简化了列混合的运算量,降低了FPGA硬件逻辑资源的消耗。

输入的一个字节是M盒元素的地址,其中高4位对应行值,低4位对应列值,最后取出对应M盒的值,这个过程表示为02×Ci,j=M(Ci,j)。优化后列混合单列的变换过程可以表示为

d(0,j)=

M(c(0,j))⊕(M(c(1,j))⊕c(1,j))⊕c(2,j)⊕c(3,j)

d(1,j)=

c(0,j)⊕M(c(1,j))⊕(M(c(2,j))⊕c(2,j))⊕c(3,j)

d(2,j)=

c(0,j)⊕c(1,j)⊕M(c(2,j))⊕(M(c(3,j))⊕c(3,j))

d(3,j)=

(M(c(0,j))⊕c(0,j))⊕c(1,j)⊕c(2,j)⊕M(c(3,j))

(19)

其中,M(Ci,j)表示对于优化后的M盒中第i行第j列所对应的元素进行查表操作,这样避免了大量复杂的乘法运算,仅仅用一个查找表的资源就实现了原来要分多次进行的组合逻辑运算。M盒模块的仿真如图9所示。

图9 M盒模块仿真结果

从图9可以看出,当M盒模块输入信号c为8’h0f且复位信号为高电平时,在时钟上升沿的输出信号d为8’h1e,与理论值一致。同理,其他仿真结果均与理论值一致,仿真正确。

3.2.2 密钥扩展模块的优化

密钥扩展模块用于生成10轮循环的128位轮密钥。轮密钥扩展模块的方式存在纯组合方式和流水线设计方式。考虑到FPGA硬件设计的速度和效率,对密钥扩展模块设计使用了10级流水线,在每一轮基本运算后面放入寄存器进行数据缓存,然后在每一个时钟时刻将上一轮缓存的数据传入下一基本运算单元,以此类推,从而构成密钥扩展十级流水线。密钥扩展模块10级流水线仿真如图10所示。

图10 轮密钥扩展10级流水线模块仿真结果

轮密钥扩展模块首先需要经过10个时钟周期产生第一组的10个轮密钥,由于采用了流水线设计技术,之后每经过一个时钟周期就会产生10个轮密钥,表明正确实现了轮密钥扩展模块10级流水线结构。

4 实验

4.1 设计开发平台与验证工具

首先编写了顶层模块的测试文件Testbench,然后使用Quartus II 13.0选择Cyclone V系列5CSXFC6D6F31C6N芯片,通过使用Modelsim 10.1d仿真工具对改进及优化后的算法进行了功能仿真和时序仿真。最后使用TimeQuest Timing Analyser对算法进行综合和时序约束。

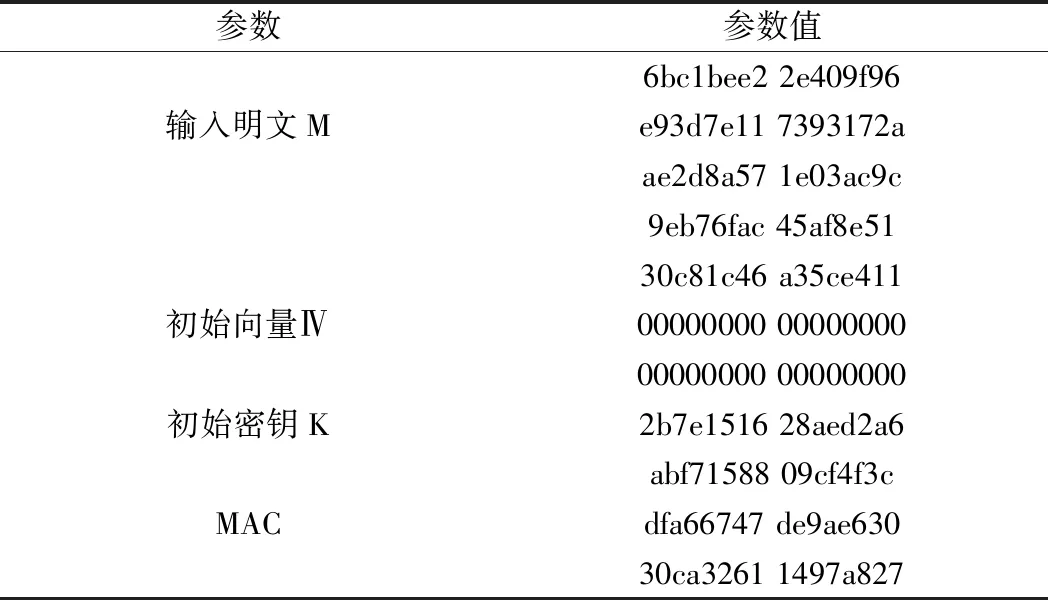

4.2 测试向量的选取

为了验证改进及优化后MASL-AES-MAC整体算法功能的正确性,需要选取测试向量进行验证。本文选择的测试向量如表2所示。

表2 算法功能测试向量

4.3 算法功能仿真测试

首先在整体功能模块仿真中,输入测试明文长度为40Byte,一共有3个明文分组128’b6bc1bee22e409f96e93d7e117393172a、128’bae2d8a 571e03ac9c9eb76fac45af8e51和64’b30c81c46a35ce 411。算法功能仿真结果如图11所示。

图11 整体功能模块仿真结果

从图11可以看出,MAC验证码为输出信号“TextOut”,此时输出信号“TextOut”为128’bdfa66747de9aa63030ca32611497c827,对比表2可知,仿真结果与理论推导结果一致,结果正确。由图11还可以看出,第一次128位数据的加密结果输出需要经过12个时钟周期。

4.4 实验评价标准

在硬件实现MASL-AES-MAC算法的相关设计中,用以下4个重要的指标来反映设计的优劣,分别是最高频率(Fmax)、面积(Area)、吞吐量(ThroughOut)和效率(Efficiency)。其中最高频率表示硬件设计的时序性能,它的值越大代表设计的时序性能越好。面积代表设计所消耗的资源,硬件设计中应尽可能地减少逻辑资源的消耗。通过最高频率和面积的值能够计算出设计的吞吐量和效率。吞吐量和效率的计算公式

(20)

(21)

式中,吞吐量表示设计中在单位时间可以处理的数据的位数,单位为比特率(Mbps),效率表示吞吐量和面积的综合性能指标,数值越大表示设计的优化效果越好。

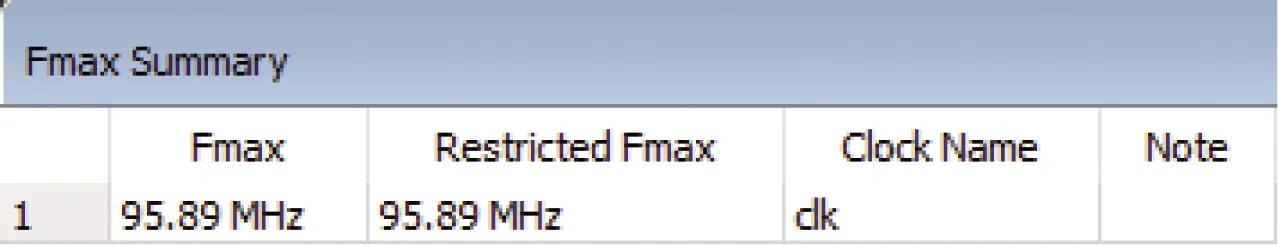

4.5 改进及优化算法的性能指标分析

首先将初始改进并未进行优化处理的算法在Quartus Ⅱ上选择了5CSXFC6D6F31C6N芯片进行了综合和添加书序约束文件SDC并进行时序约束。时序分析报告显示设计的建立裕量和保持裕量分别为10.928 ns、0.267 ns,两者均为正数,则表示设计满足约束文件中的时序约束。通过查看此时产生的FmaxSummary文件,显示最高频率Fmax为95.89 MHz,如图12所示。

图12 Fmax报告图1

由之前的功能仿真图9得知第一次加密结果输出需要经过12个时钟周期。

将本文改进的基于传统AES算法的MASL-AES-MAC算法与文献[6]中传统的基于TDES算法的MASL-TDES-MAC算法进行对比,对比结果如表3所示。通过对比可知本文的算法设计具有更高的最高频率Fmax和更低的逻辑资源消耗。

表3 改进算法前后性能对比

通过将MASL-MAC算法改为安全性能更好的MASL-AES-MAC算法之后,切实提高了铁路信号安全协议在开放性系统中的安全性能。

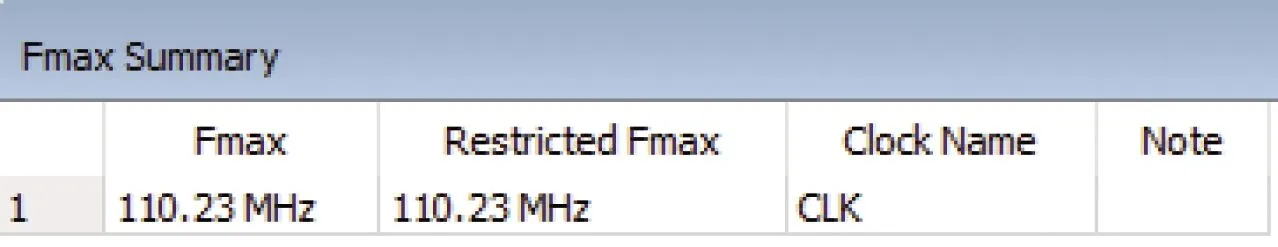

其次,将改进并优化后的算法同样在Cyclone V 5CSXFC6D6F31C6N芯片进行了综合和添加书序约束文件SDC并进行时序约束。时序分析报告显示设计的建立裕量和保持裕量分别为9.571 ns、0.242 ns,两者均为正数,表示设计满足约束文件中的时序约束。通过查看此时产生的FmaxSummary文件,显示最高频率Fmax为110.23 MHz,如图13所示。

图13 Fmax报告图2

通过查看设计的整体编译报告,报告显示设计在Altera公司的Cyclone V 5CSCFC6D6F31C6N芯片上共占用逻辑资源1595 ALMs,占用芯片总体的4%。如图14所示。

图14 改进优化后的MASL-AES-MAC算法综合报告

最后将优化前后MASL-AES-MAC算法性能进行对比分析,分析结果如表4所示。

表4 改进算法优化前后性能对比

通过对优化算法前后性能的对比得出:优化后的算法不仅获得了更高的最高频率,同时还进一步降低了逻辑资源的消耗。

由之前的功能仿真图得出,本文改进的基于高级加密标准AES算法的MASL-AES-MAC算法,在联合仿真实验中对第一次128位数据的加密结果输出需要经过12个时钟周期,算法优化前后的最高时钟频率分别为95.89,110.23 MHz。经计算,联合仿真实验中对优化前后算法在相同条件下分别进行128位数据的加密结果输出需要经过的时间分别为125.14,108.86 ns。而文献[6]传统的基于TDES算法的MASL-TDES-MAC算法中对于第一次64位数据的加密结果输出需要经过26个时钟周期,其最高时钟频率为72 MHz,经计算第一组数据的加密结果输出需要经过的时间为361 ns。

通过上述实验数据对比分析可知,本文提出的基于高级加密标准AES算法的MASL-AES-MAC算法(优化前)比传统的基于TDES算法的MASL-TDES-MAC算法在实时性方面提高了65.34%;通过改进并优化之后的MASL-AES-MAC算法比优化前(改进后)的MASL-AES-MAC算法在实时性方面提高了13%,比传统的基于TDES算法的MASL-TDES-MAC算法在实时性方面提高了69.84%。

综合表3、表4和上述实验对比分析结果得出,本文先后通过对消息鉴定安全层消息认证码算法的改进和优化之后,切实提高了铁路信号安全协议的安全性和实时性。

5 结语

针对铁路信号安全协议RSSP-II中MASL层消息认证码算法的低安全性和低实时性问题,提出了一种基于高级加密标准AES算法的MASL-AES-MAC算法。该算法首先充分利用AES算法的高安全性来保障协议的安全性。其次通过将改进的MASL-AES-MAC算法在FPGA上实现,并利用查找表技术和流水线技术进行优化处理,来获取更高的最高频率和更低的逻辑资源消耗,从而使得协议具有更高的实时性,将高安全性和高实时性结合于一体。最后在Quartus Ⅱ和Modelsim中完成了联合仿真实验,将改进及优化后的MASL-AES-MAC算法与改进前的MASL-TDES-MAC和改进但并未优化的MASL-AES-MAC算法进行对比,结果表明:无论是最高频率还是逻辑资源消耗情况都优于原算法,从而提高了高速铁路通信的安全性和实时性。