引信高频脉冲编码信号测试装置优化

2020-05-18张鹏,谢锐

张 鹏,谢 锐

(中北大学仪器科学与动态测试教育部重点实验室,山西 太原 030051)

0 引言

采用电磁感应技术通过设定出炮口处的线圈,可控制引信工作方式。引信随弹丸发射通过炮口处的发射线圈将编码信号传输给引信的接收线圈,此过程信号频率高、速度快、环境恶劣[1]。引信系统是否能够可靠稳定工作决定着武器的性能能否充分发挥,因此在高冲击、高频率、强干扰的动态恶劣环境下,有效的试验与测试引信输出信号质量是否符合系统设计要求非常必要。

近年来专用数据采集卡迅速发展,例如西安电子科技大学研制的VPX3-SBD读/写速度分别为296 MB/s和304 MB/s,768 GB的超大容量存储[2]。中北大学针对动态数据的采集存储先后研制出侵彻测试的小容量记录仪和多通道弹载大容量记录仪,存储容量大于100 GB,读取速度100 Mbps。但现有数据采集卡不能完成对高频脉冲编码信号的采集。

中北大学研制的500 MHz采样速度的高频脉冲编码信号测试仪在调试过程中电路工作时易发热影响模拟信号质量,而且由于采样时钟的抖动,容易引起ADC采样误差导致信噪比降低。对模拟状态下引信输出脉冲编码信号的测试研究不能满足引信测试的需求。针对上述问题,提出了一种基于高速数据采集存储技术的高频脉冲编码信号采集存储测试装置。

1 高速数据采集技术

高速数据采集存储系统的主要技术指标有模数转换、信号调理、信号完整性、电磁兼容性、电源完整性和存储技术。高速采集系统的关键是高速电路的设计和部分高速信号的时序约束。通常定义的高速电路为数字信号的传输延时大于1/2倍的边沿时间或数字电路的频率大于45 MHz。当系统时钟频率超过100 MHz或上升沿小于1 ns时也称为高速系统。本文采集系统属于高速电路,对高频信号的采集存储必须考虑传输线效应引起的串扰、反射、延时等信号完整性问题以及高频电路中对电容的等效处理问题。

2 基于高速数据采集存储技术的测试装置

2.1 测试装置总体方案

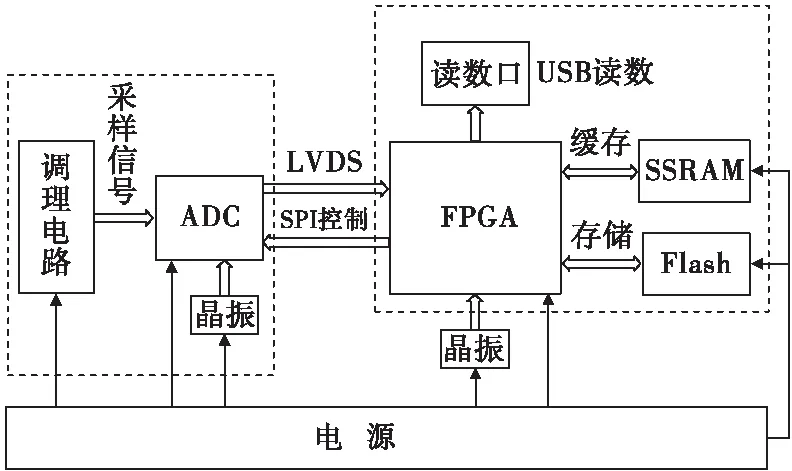

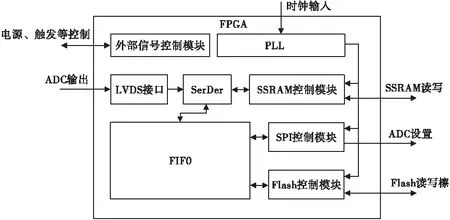

结合高速电路设计,测试系统整体分为模拟部分和数字部分。从采样频率、采样时间、系统低功耗、小体积等方面考虑,模拟部分对信号调理电路设计和高速ADC芯片的选型以及电路原理设计,不仅提高了采样精度与速度,而且解决了时钟抖动引起的低信噪比问题[3]。数字部分以FPGA为控制核心,将采样到的数据缓存到SSRAM,采集完成后再转存到Flash,完成FPGA,SSRAM以及Flash的芯片选型和功能仿真。系统硬件框图如图1所示。

图1 系统硬件框图Fig.1 System hardware block diagram

系统工作流程:系统上电后处于待触发状态,当接受到外部触发信号后,系统进入采集状态,为满足A/D转换输入信号的幅值要求,待测信号首先经过衰减电路,再经差分电路后信号转换为高速LVDS信号并送至A/D转换芯片,A/D转换后输出的数字信号经FPGA处理后写入SSRAM缓存,为使采集到的数据不易掉电丢失,一次采集结束后再将缓存数据全部转存至Flash,此时完成一次完整的采集存储。再用USB3.0专用读数口将回收装置与计算机连接,利用读数软件将数据信号读取到LabVIEW上位机进行显示,并完成进一步的数据分析和处理。

2.2 测试装置硬件电路设计

2.2.1信号的衰减

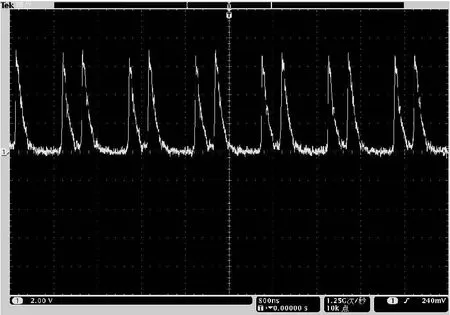

接入采集电路的引信装置输出阻抗为1.2 kΩ,输出信号集中在30 MHz,最高频率分量为50 MHz,最大幅值为7 V,示波器采集到的原始引信信号如图2所示。从图2中明显得知最大幅值在7 V左右(纵轴每格2 V),最窄脉宽约为320 ns,上升时间约为30 ns。而设计要求A/D转换电路的输入电阻不小于1 MΩ,输入电容不大于8 pF。由于输入信号幅值较大需要设计专门幅值衰减电路以匹配后端ADC的输入范围。

图2 原始引信信号Fig.2 Original fuze signal

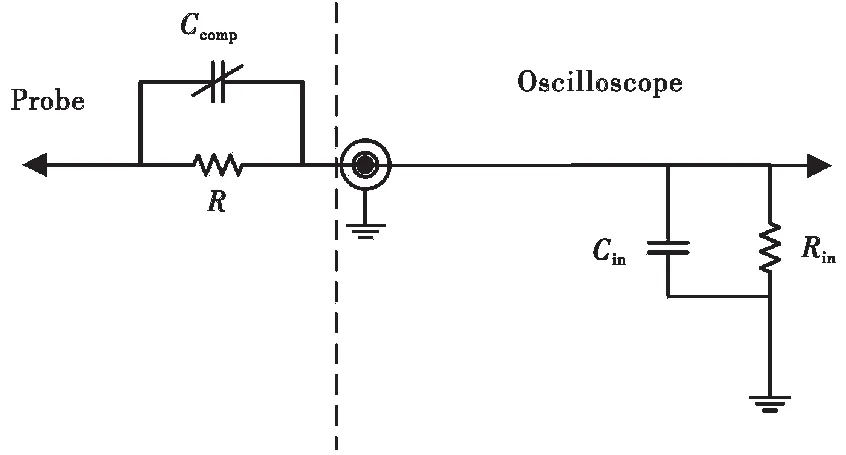

由于待采信号频率高,设计衰减电路必须考虑电阻和电容的分布参数对信号的影响,故设计衰减电路参考示波器带电容补偿的高阻无源探头的衰减原理,如图3所示。探头端由可调补偿电容Ccomp和电阻R并联构成,示波器内部等效为电容Cin和Rin的并联结构,补偿电容用来调整示波器探头的输出电容值使其总电容值匹配示波器内部电容[4]。

图3 示波器无源探头结构Fig.3 Oscilloscope passive probe structure

对以上电路结构做如下分析:

(1)

式(1)中,A为(低频信号的)衰减比例。从示波器的输入端口来看:

(2)

(3)

根据示波器上带补偿的高阻无源探头信号衰减理论,要使此电路对高频输入信号有同样的衰减比例,须保证ZL上的电压幅值与输入信号的幅值之比等于A,即:

(4)

对式(4)进行化简整理可得:

(5)

若要使式(5)对于不同的ω恒成立,即衰减比例与输入信号的频率ω无关,则需要:

RinCin=RCcomp

(6)

又设计要求采集电路输入端电阻不小于1 MΩ,输入电容不大于8 pF。故设计电路中脉冲编码信号通过屏蔽线进入系统,通过可调电容来补偿屏蔽线的分布电容,其输入阻抗为1 MΩ,输入电容约为5 pF。

2.2.2阻抗变换与优化仿真

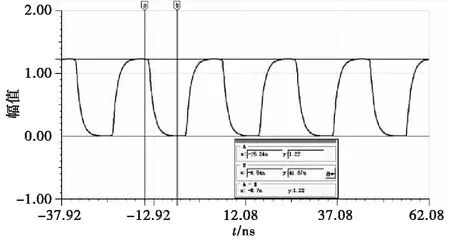

之前研制的500 MHz采样速度高频脉冲编码信号测试仪,引信输出编码信号衰减后直接送入单端转差分运放电路,没有做阻抗匹配设计,导致差分运放的两个反馈回路不平衡,造成输出信号共模电压被抬高出现消顶现象。为隔离高频脉冲测试装置的信号输入端和ADC的驱动运放,从而实现阻抗匹配,故选择ADI公司高速低噪声的宽带运放ADA4817-1实现阻抗变换[5],为了匹配ADC转换器对输入电平的要求,将ADA4817的放大倍数设置为3.5倍。输入方波信号上升沿为1 ns,频率为50 MHz,峰峰值为350 mV,仿真结果如图4所示。幅值为1.22 V,上升沿变慢。被测信号集中在30 MHz附近,对原始信号几乎没影响。匹配电路如图5所示。

图4 ADA4817输出的方波信号Fig.4 ADA4817 output square wave signal

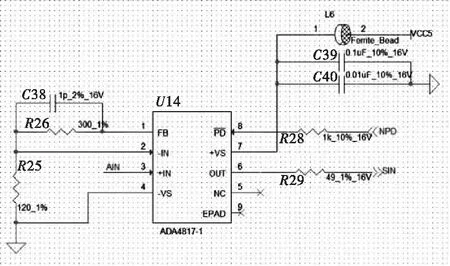

图5 ADA4817原理图Fig.5 ADA481schematic diagram

ADA放大倍数是1+R26/R25=3.5,电容C38和电阻R29是用来降低或者消除运放闭环增益在接近增益衰减处可能出现的增益尖峰。同时R29也作为信号源的输出阻抗和50 Ω传输线相匹配。NPD是ADA4817的掉电引脚,通过FPGA的控制可以实现ADA4817的低功耗。

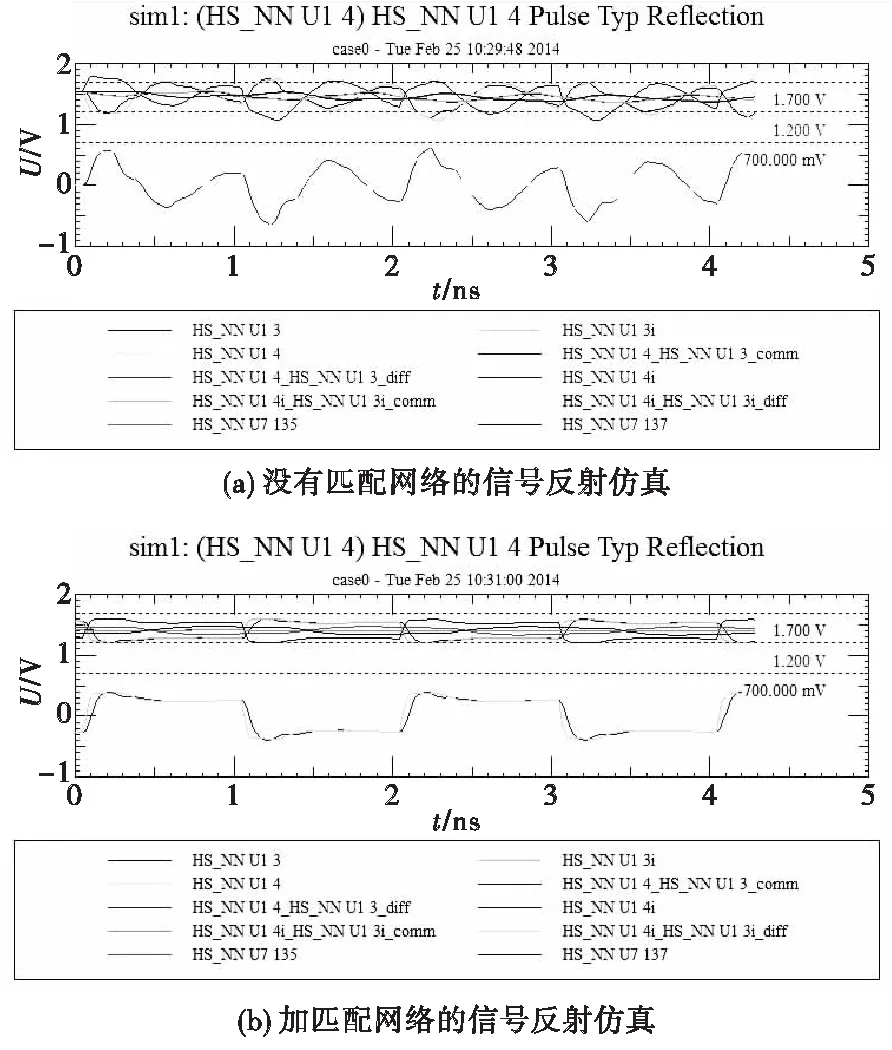

AD9434的输入信号必须为差分信号,而衰减后的信号仍为单端模拟信号,必须对其差分化后才能送至后级A/D转换器。考虑到噪声引入A/D转换的可靠性与准确性以及信号采集的完整性,选用集成调理芯片AD8138实现输入信号的差分化[6]。结合后端电路,为降低AD9434开关电容的影响,在AD8138输出端接一对33 Ω电阻。AD8138连接衰减电路的输出端并联50 Ω电阻以驱动同相输入端500 Ω端接电阻。设置AD9434输出信号为上述方波信号,分别对加匹配网络和没有加匹配网络的电路信号进行反射仿真,结果如图6所示。

图6 反射仿真结果Fig.6 Reflection simulation results

由图6可知,加了匹配网络的仿真结果信号完整性较好,输出基本上为方波信号,而没有加匹配网络的电路信号波形明显失真,出现严重反射现象。

2.2.3高速ADC

ADC是数据采集系统的核心,ADC的性能参数往往决定着整个采集系统的性能[7]。为了提高分辨率,降低共模误差,综合考虑目前市场上常见的500 MSPS的ADC位数、信噪比、有效位数、信纳比等性能指标,输入信号、输出信号类型、功耗和供电等参数选择ADI公司12位的AD9434,它是基于BiCMOS制程工艺的流水线型开关电容ADC,内部集成差分输入缓冲器,且使用LVDS(ANSI-644)差分信号输出采样数据。

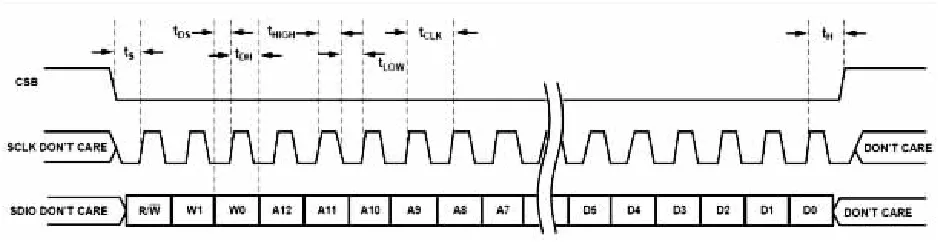

AD9434可以通过SPI接口配置内部寄存器从而实现特定的功能或操作。AD9434有三条SPI控制线,SCLK/DFS(串行时钟)用于同步与ADC的读写通信。SDIO(串行数据输入输出)是一个双向引脚,可以将数据发送到内部寄存器并从中读取。CSB是低有效的片选,用于允许或禁用读写操作。SPI的时序图如图7所示,当CSB有效时,在SCLK的下降沿通过SDIO引脚将数据输出或输入,其中起始位是读写标志位,紧接着是寄存器相关的地址信息。

图7 SPI时序图Fig.7 SPI sequence diagram

2.2.4FPGA主控电路设计

装置选用广泛应用于设备控制领域的FPGA作为主控芯片,其内部逻辑资源丰富,编程灵活多样,易操作,且内部采用并行执行结构,在处理不同事件时不会出现资源竞争[8]。FPGA内部由外部信号控制模块、PLL、LVDS接口、SerDer串行器解串器、SSRAM控制模块、SPI控制模块、Flash控制模块以及FIFO组成。PLL利用外部时钟输入进行倍频分频等操作分别给SSRAM、SPI以及Flash的操作提供时钟。外部信号控制模块主要用于对部分电源的使能、触发信号的响应和低功耗的实现。系统工作时将ADC输入出的数据暂存SSRAM之中,存满即停止数据采集工作并将缓存的数据写入Flash,随后进入低功耗状态。在FPGA内部通过Verilog HDL语言以及IP核设计相应的子模块来完成。图8所示为系统总体逻辑框图。

2.2.5存储器选型及时序仿真

按设计要求存储容量是30.52 Mb,因测试仪存储容量要求不大,故采用SSRAM+FLASH的存储方法。SRAM速度快、效率高、功耗低、操作简单[9],考虑低成本低功耗SSRAM采用ISSI公司36 Mb存储容量的IS61LPS102436B实现采集数据的缓存,其最高时钟频率达到250 MHz,在一个CLK下可以写入4 Byte数据。IS61LPS102436B的管脚中与数据传输有关的引脚主要有32个数据线、4个数据奇偶校验引脚以及18根地址线组成,其他是控制功能和时钟功能引脚[10]。

图8 系统总体逻辑框图Fig.8 System overall logic block diagram

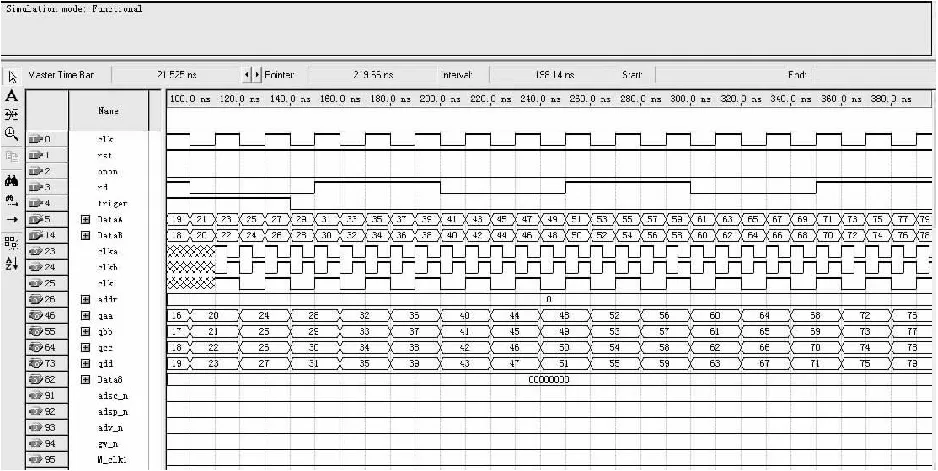

根据设计中存储器的特点和存储容量的需求,Flash选择SAMSMNG公司SLC结构的K9F1G08M0M存储芯片,其存储容量为 (128 M+4096 K)×8 bit。SSRAM读写时首先需要保证片选信号有效,在控制信号有效前也需要保证数据位和地址位有效。本设计系统选用的SSRAM缓存芯片IS61LPS102436B,写周期在时钟上升沿时有效,写数据需要一个时钟周期,读操作需要三个时钟周期,且不能使用同一个时钟信号,因为三个时钟周期的功能不相同,第一个时钟周期主要用于地址的锁存,第二个时钟周期用来锁存内部读取数据,第三个时钟周期主要用于数据输出。写时序仿真如图9所示。图中DataA和DataB分别存放缓存数据,之后顺序写入SSRAM的数据引脚中。

图9 SSRAM读写时序仿真Fig.9 SSRAM read-write timing simulation

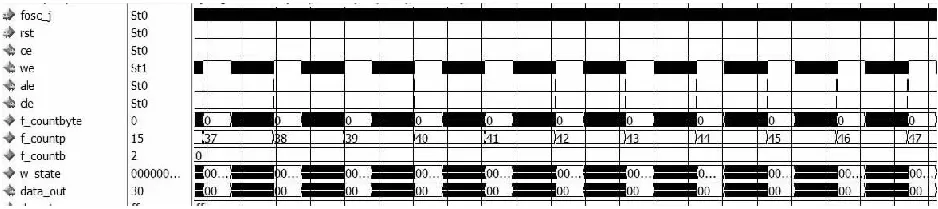

Flash编程时序功能仿真如图10所示。其中ce是Flash的使能端,f_countbyte[10∶0]表示一页2K计数器,f_countp[5∶0]为64页计数器,f_countp[9∶0]表示Flash的1 024块计数器。仿真图中显示f_countp从37页到40页的页操作过程,由于一块是64页,图中f_countb信号仍为第一块,仿真过程与Flash的编程操作时序一致,能够将缓存在SSDRAM中的数据正确转存在Flash中。由于篇幅有限,其余Flash的读取、坏块检测操作功能均能实现,不再赘述。

图10 Flash写操作时序功能仿真Fig.10 Flash write sequence function simul-ation

3 实测采集数据结果分析

在对弹载高频脉冲测试装置调试完成以后,要置于弹体内采集弹丸飞行过程中接收的引信编码信号,在炮口位置安装磁环形成强磁场,采用磁敏感霍尔元件作为触发信号源,装置在出炮口被触发,开始采集。

利用信号发生器作为信号源,输出不同频率的正弦波信号对本装置进行功能验证。

数据采集完成后,通过USB3.0专用读数接口保存至PC机,并通过LABVIEW编写的上位机软件观测采集到数据。

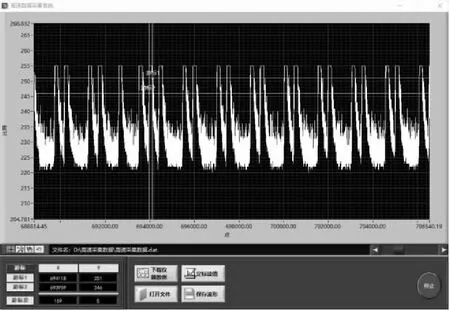

本测试装置硬件电路尺寸3.6×6.8 cm用环氧树脂灌封在直径4.8 cm高9 cm的中空铝材圆柱体内,随弹丸运动时抗冲击性强。采集信号发生器产生的50 MHz正弦波信号如图11所示,横轴是采样点数,纵轴是比特值。图11中横轴游标差值知当以500 MHz采集速率对50 MHz正弦波信号进行采样时,一个周期采集到10个点,采集到的正弦波信号比特值在500~3 000之间对应于183.1~1 098.6 mV(ADC满量程为1.5 Vp_p),符合测试装置的设计要求。

将该测试装置置于弹丸内采集弹丸接收的引信编码信号,图12所示为实测原始引信脉冲信号,图中游标显示最窄脉宽横坐标差值约为160点,对应于时间是342 ns,这与图2示波器采集到的最窄脉宽320 ns基本一致。图12中噪声比特值约为250 b,对应于电压为523 mV(250÷4 096×1.5×20÷3.5=523 mV)。图13是之前实测数据,图13中噪声比特值约为20 b,对应于电压为586 mV(20÷256×1.5×5=586 mV)。相比于图13本文高频脉冲测试装置实测波形明显得到改善,没有消顶现象,提高了信噪比,能很好地反映原始编码信号波形。

图11 采集50 M正弦波信号Fig.11 Acquisition of 50 M sine wave signal

图12 本装置实测数据Fig.12 Actual measured data of this device

图13 之前装置实测数据Fig.13 Actual measured data of previous device

4 结论

本文提出了基于高速数据采集存储技术的高频脉冲编码信号采集存储测试装置,该装置通过阻抗匹配设计解决了消顶现象,对高速ADC综合选型,提高了采样精度,并且解决了时钟抖动引起的低信噪比问题。以FPGA作为主控制器,控制模数转换芯片AD9343进行数据采集和转换,将采到的数据缓存到SSRAM中,采集完成后再转存入Flash避免了存储过程中数据丢失,保证了数据完整性。经实测实验验证,该测试装置采样速度可达500 MHz,采样精度为12 b,且能稳定采集,信号完整性良好,满足测试装置对脉冲信号的采集存储要求,具有一定的使用价值。该装置对信号的串扰,EMI等仍需进一步分析研究,以降低采样中出现的噪声。