抗辐射集成电路单粒子激光试验与仿真分析

2020-05-11张海涛

刘 淼,张海涛

(1.中国电子科技集团公司第四十七研究所,沈阳110032;2.中国人民解放军95979 部队,山东 新泰271207)

1 引 言

集成电路广泛应用于各类电子产品,特别是在功能复杂,性能优越的电子产品中,集成电路通常是其中的核心器件。抗辐射集成电路是指具有抵抗宇宙射线或其他类型辐射射线功能的集成电路[1-2]。在太空环境中,宇宙射线会对普通的数字集成电路和模拟集成电路造成损坏,从而影响航天器的正常工作。集成电路的辐照效应一般分为总剂量效应(TID),单粒子效应(Single-Event Effect, SEE)以及剂量率效应(Dose Rate Effect)。单粒子效应则包括单粒子翻转(Single-Event Upset, SEU),单粒子瞬态(Single-Event Transient, SET),单粒子闭锁(Single-Event Latch-up, SEL),单粒子栅穿SEGR(Single-Event Gate Rupture)等[3-5]。根据集成电路工作环境和使用要求的不同,对抗辐射集成电路的设计要求也有所不同[6-8]。

2 单粒子翻转机理

单粒子效应是单个高能粒子在穿过微电子器件的灵敏区时,在其轨迹上沉积电荷,这些电荷被器件电极收集,造成器件逻辑状态的改变或器件损坏。基本过程是入射带电离子损失能量,形成电离过程,电离过程产生电子-空穴对,自由电子和空穴被电路敏感结收集后,电路逻辑状态被错误触发。容易发生单粒子翻转的器件结构通常是像SRAM 这种利用双稳态进行信号存储的器件,其次是微处理器这种功能复杂,工作频率高的电路,还有就是一些接口电路。单粒子翻转率是单粒子翻转的指标,单粒子翻转率是器件每天每位发生单粒子翻转的概率,计算质子单粒子翻转率的一般公式是:

其中:E0为阈值能量,单位MeV;σp(E)为质子单粒子翻转截面积,单位cm2/bit;φ(E)为质子微分流量。

3 激光试验

脉冲激光模拟单粒子效应技术以其试验便捷、效率高、精确的空间和时间分辨特性等优势,在世界范围内越来越多的被应用于单粒子效应机理研究和工程实践中,已经成为单粒子效应特性评估和防护设计验证的有效手段。

通过对芯片进行激光模拟试验,在显微镜下找到发生单粒子翻转的位置如图1 所示。

图1 脉冲激光模拟单粒子效应试验敏感位置照片

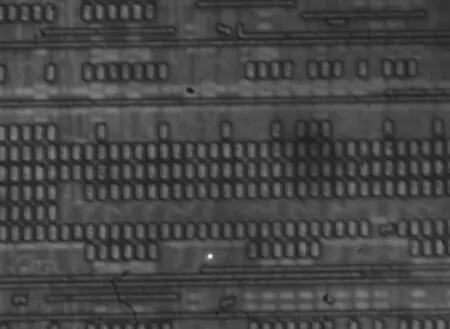

在版图上找到相应位置如图2 所示。分析后证明该位置位于一个AOR21(2 与1 或门)的输出端,靠近PMOS 管与NMOS 管连接处。

图2 发生单粒子翻转的敏感位置版图

4 逻辑分析与优化

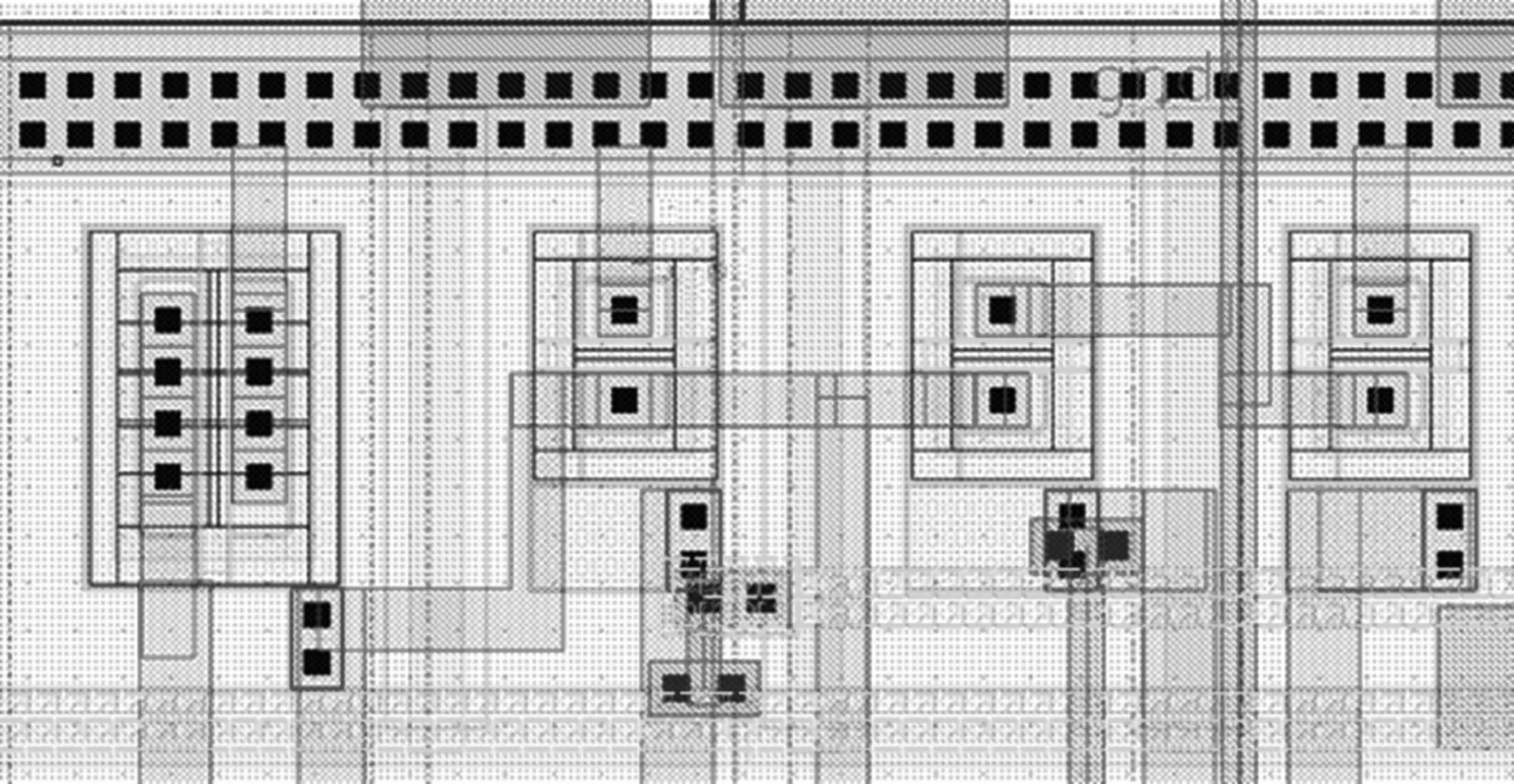

与版图对应的逻辑功能框图,如图3 所示。

图3 逻辑功能框图

图3 中P1、P2、P3 是PMOS 器件,N1、N2、N3 是NMOS 器件,NAND2 是2 与非门,INV 是反相器,AOR21 是2 与1 或门,DFF 是带reset 端的D 触发器。

从逻辑图与版图对照可知,敏感点位于INV3的输入端,即P3、N1、N2 三个MOS 器件的连接端。P1、P2、P3 和N1、N2、N3 构成2 与1 或门,P1、P2、N1、N2 的输入端都接VSS,N2 与P3 的输入端连接后,与AOR21 的输出端连接。模拟单粒子干扰信号由V0 产生,经过INV3 的输入端传输到DFF 的输入端,在触发器的时钟的有效沿,单粒子干扰信号从DFF 的Q 端输出到NAND2 的输入端,NAND2 的另一个输入端接高电平5V,单粒子干扰信号从NAND2 的输出端连接INV2 的输入端,经过输出端连接到AOR21 的“或”输入端,该AOR21 的两个“与”输入端口分别连接INV1 的输出端和VSS。单粒子干扰信号经过AOR21 的输出端连接P3 的栅极,该P3 的漏极连接到INV3 的输入端,这样单粒子干扰信号形成回路。同样模拟单粒子干扰信号经过INV3 传输到DFF 的输入端,在触发器的时钟的有效沿,单粒子干扰信号从DFF 的QN 端输出到INV1 的输入端,通过INV1 后连接AOR21 的“与”输入端,另一个“与”输出端接VSS,“或”输入端接INV2 的输出,单粒子干扰信号经过AOR21 的输出端连接P3 的栅极,该P3 的漏极连接到INV3 的输入端,这样单粒子干扰信号形成第二个回路。干扰信号形成回路后,会持续保持错误状态,从而影响正常信号的传输,形成单粒子翻转。当INV3 的正常输入信号为高电平时,干扰信号会将其拉低形成翻转,这时,P1、P2、P3 三个PMOS 器件就成为敏感器件。通过对敏感器件的宽长比的调整就能够抑制信号干扰,避免单粒子翻转。

5 仿真分析与结果

图3 中V4 是时钟发生器:电压voltage=0v~5v,延时delay time=500ns,上升时间rise time=1ns,下降fall time=1ns,脉冲时间pulse time=25ns,周期period=50ns。

V3 是reset 信号发生器:time=0s 时,voltage=0v,time=400ns 时,voltage=0v,time=450ns 时,voltage=5v。

V1 是高电平发生器:V=5v。

V2 是电源信号发生器:time=0s 时voltage=0v,time=100ns 时voltage=0v,time=150ns 时voltage=5v。

V0 是干扰信号发生器:电流current1=0A,电流current2=IMAX,延时delay time1=1.599005μs,衰减系数damping factor1=30ps,延时delay timing2=1.59914μs,衰减系数damping factor2=200ps。

PMOS 管P1 的 宽=Wp1, PMOS 管P2 的 宽=Wp2, PMOS 管P3 的宽=Wp3。

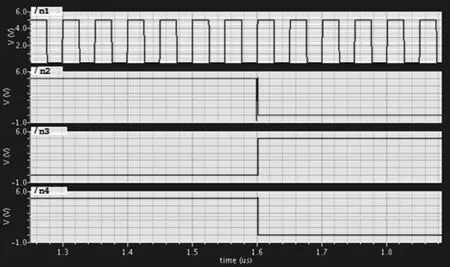

对电路施加干扰信号,当IMAX=3mA,Wp1=4μm,Wp2=4μm,Wp3<4.9μm 时,发生单粒子翻转,INV3 的输入信号由高电平被拉低为低电平,触发器DFF 的Q 端输出信号由低电平翻转为高电平,触发器DFF 的QN 端输出信号由高电平翻转为低电平,并且在后面的多个时钟周期,持续保持单粒子翻转状态。仿真波形如图4 所示。

图4 发生单粒子翻转波形图

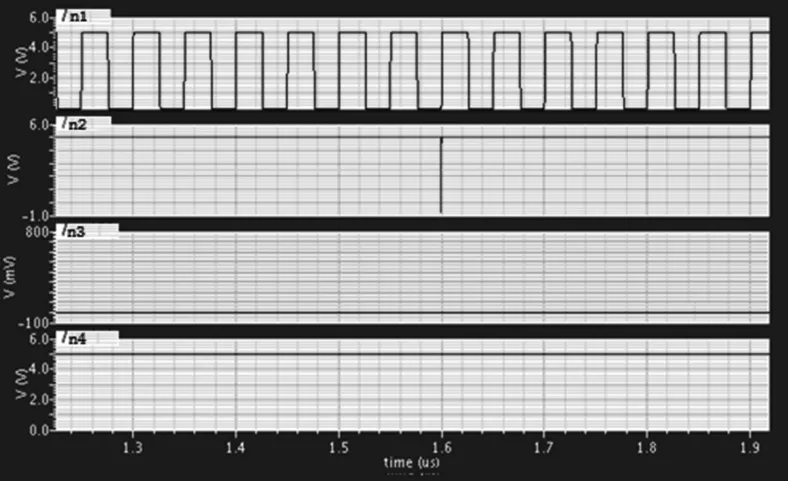

对电路施加干扰信号,当IMAX=3mA,Wp1=4μm,Wp2=4μm,Wp3≥4.9μm 时,未发生单粒子翻转,INV3 的输入信号在单粒子干扰瞬间,由高电平被拉低为低电平,然后迅速恢复高电平状态,并持续保持高电平状态。触发器DFF 的Q 端的输出信号未受到单粒子干扰,持续保持高电平状态,触发器DFF的QN 端的输出信号未受到单粒子干扰,持续保持低电平状态。仿真波形如图5。

图5 未发生单粒子翻转波形图

当IMAX=3mA,Wp3=4μm,Wp1+Wp2≥12.5μm时,未发生单粒子翻转,仿真波形如图5 所示。

当IMAX=3mA,Wp3=4μm,Wp1+Wp2<12.5μm时,发生单粒子翻转,仿真波形如图4 所示。

当IMAX=4mA,Wp1=5μm,Wp2=5μm,Wp3 ≥5.5μm 时,未发生单粒子翻转,仿真波形如图5 所示。

当IMAX=4mA,Wp1=5μm,Wp2=5μm,Wp3 <5.5μm 时,发生单粒子翻转,仿真波形如图4 所示。

当IMAX=4mA,Wp3=5μm,Wp1+Wp2 <12μm时,发生单粒子翻转,仿真波形如图4 所示。

当IMAX=4mA,Wp3=5μm,Wp1+Wp2 ≥12μm时,未发生单粒子翻转,仿真波形如图5 所示。

综上所述,单粒子翻转发生的因素包括干扰粒子的能量、逻辑电路结构、MOS 器件结构等,其中修改MOS 器件宽长比结构能有效抑制单粒子翻转的发生。

6 结 束 语

集成电路在辐照条件下,产生单粒子翻转,其形成原因十分复杂,受电路逻辑结构、加工工艺、使用环境等多方面因素的影响。本设计仅以某普通抗辐射集成电路为例,通过脉冲激光模拟单粒子效应技术,对抗辐射集成电路进行激光实验,在抗辐射集成电路逻辑功能框图中找到引起单粒子翻转的逻辑功能块,通过调整敏感MOS 器件的宽长比属性和仿真激励模型,最终找到解决该集成电路单粒子翻转问题的方案并通过仿真对方案进行验证,所获得的数据和结论具有一定代表意义。所设计的抗单粒子翻转的方法能够应用到集成电路设计中,具有一定的实用价值。