一种重掺衬底上生长硅外延层的工艺研究

2020-05-09傅颖洁李明达

傅颖洁,李明达

(中国电子科技集团公司第四十六研究所 天津300220)

0 引 言

肖特基二极管以其功耗小、正向导通电阻低和响应速度快的优点而获得广泛应用[1]。近年来,随着该类型器件对反向击穿电压、正向压降等特征参数一致性要求的进一步提高,采用重掺衬底为基底制备硅外延层,其过渡区形貌、厚度及电阻率参数指标决定了该器件的正向压降、反向击穿电压等电参数的特性[2]。因此,在外延沉积过程中,有效控制过渡区的宽度以及提高厚度、电阻率参数均匀性指标成为了外延工艺设计的核心和重点[3]。

1 外延层过渡区

在重掺衬底生长轻掺硅外延工艺过程中,影响过渡区宽度的主要因素是各类非主动掺杂影响,包括衬底与外延层之间的杂质固-固扩散和反应系统的杂质气相掺杂。固-固扩散指的是衬底所包含杂质的热运动扩散,非主动掺杂包括钟罩、石英件、基座等杂质的挥发。综合研究表明,过渡区宽度与衬底电阻率、HCl气抛和外延沉积温度等工艺条件密切相关。

1.1 衬底电阻率的影响

重掺衬底掺杂电阻率的范围介于 0.002~0.004Ω·cm 之间,而本文所制硅外延层的电阻率为1.8~2.0Ω·cm,两者电阻率相差已经超过 3个数量级,衬底和外延层载流子浓度之间的差距越大,受此重掺杂影响,外延层的电阻率爬升速率会放缓,过渡区形貌控制难度也将相应加大。

1.2 HCl气抛的影响

在常规外延工艺中,通常会采取 HCl在高温下对硅衬底片实施原位气抛,以消除衬底表面的自然氧化层以及随机产生的各类沾污,通过剥除一部分表层衬底,可以使硅外延层晶格生长质量更高,但气抛工艺也会随之产生大量的杂质并被挥发到反应气氛中,这些杂质随后会随反应过程重新进入后续生长的硅外延层,尤其会居于边缘位置,导致外延层过渡区展宽的风险大增。

1.3 外延沉积温度的影响

生长外延层的工艺温度通常在 1110~1130℃。高温下衬底所含的As杂质原子可以通过基板提供的能量不断向生长气氛中进行挥发,以及向外延层扩散的热运动效应,气相逸出和固-固扩散活动较为剧烈,导致外延过程中非主动掺杂现象颇为严重,致使外延层过渡区宽度增加。

2 厚度和电阻率参数及其一致性

2.1 外延层沉积速率的影响

外延层的沉积速率与外延层的厚度、电阻率参数的均匀性密切相关,通常外延沉积速率越慢,则外延层的沉积越均匀,外延片的厚度参数片内均匀性越好。

2.2 外延温度梯度的影响

反应腔体内硅外延片下方的高频线圈的温度梯度越小,则片内的工艺温度更趋均匀,相应的外延层生长速率和掺杂效率的分布也越均匀,最终制得的硅外延层的厚度和电阻率参数越趋于均匀。

2.3 低温本征及变流吹扫的影响

在外延工艺过程中,通过在较低工艺温度下的本征生长,抑制杂质的挥发,同时在 HCl气抛后以及本征层外延生长后均进行 1次主氢气流的变流量吹扫赶气(290~350~290L/min),这样通过前后实施2次变流量吹扫,可以很大程度上减少了杂质扰动的影响,电阻率一致性可以得到显著提升。

3 外延材料制备

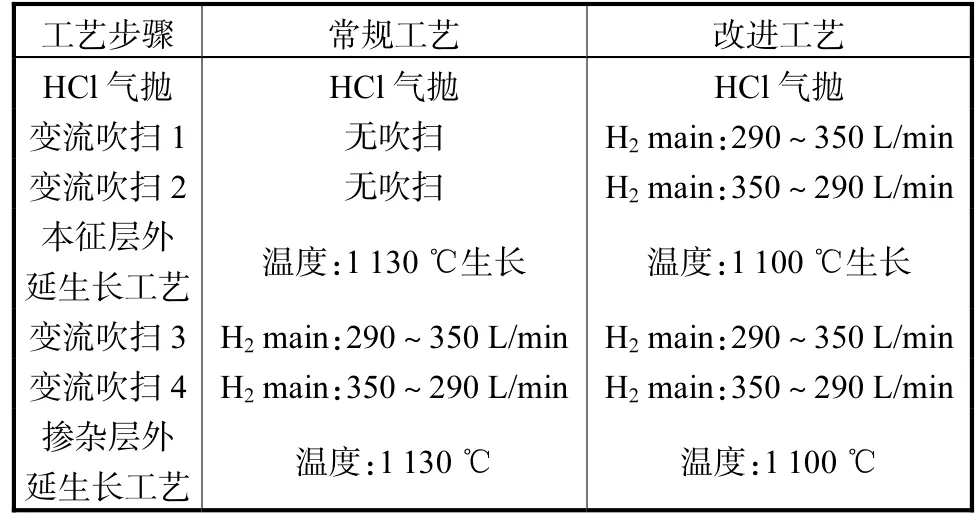

采用如表 1所示的 2种外延工艺条件在重掺衬底上进行硅外延层的沉积。

表1 两种外延工艺条件比对Tab.1 Comparison of two epitaxial process conditions

4 结果与分析

试验结果表明,在对硅抛光片表面的 HCl气抛工艺结束后,随之快速引入主氢气流的变流吹扫,可以减少衬底受热挥发逸出的 As杂质,从而可以降低这类非主动掺杂作用对外延过渡区宽度的影响。随后采用 1100℃的低温本征的沉积工艺,有效抑制了外延层工艺过程中衬底杂质的逸出,降低了自掺杂效应的影响,可缩小外延层过渡区宽度,电阻率由衬底上升的速率明显加快,过渡区宽度由原先的 2μm 缩减为不足1.6μm。

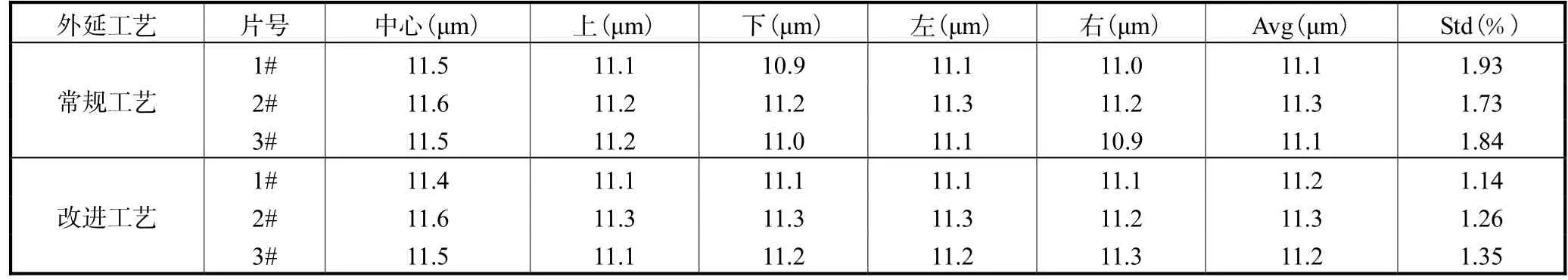

2种不同硅外延工艺下的外延层厚度的测试结果如表 2所示。在改进工艺中,硅外延掺杂层的生长速率因生长温度降低得以放缓,在低生长速率下,硅外延片的片内厚度均匀性较常规工艺相比得到了有效改善。

表2 不同工艺外延厚度测试结果Tab.2 Epitaxial thickness test results by different processes

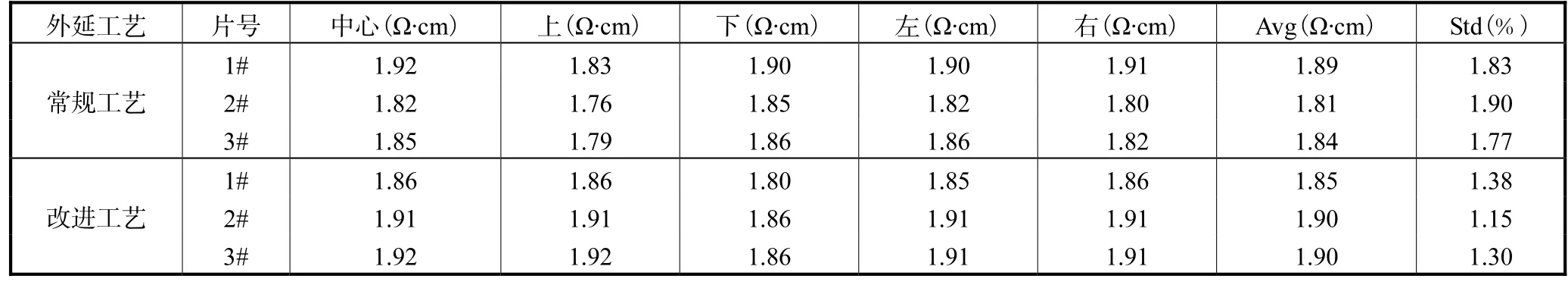

2种不同硅外延工艺下,硅外延层电阻率的测试结果如表3所示。改进工艺中增加一次主氢气流的变流吹扫(290~350~290L/min),最终通过滞留层的厚度快速变化,从而有效抑制了杂质对外延生长过程的扰动,可见外延层电阻率不均匀性较常规工艺明显提高。

表3 不同工艺硅外延片电阻率测试结果Tab.3 Epitaxial resistivity test results by different processes

5 结 论

本文基于常规外延工艺,针对在重掺衬底上制备轻掺硅外延层时面临过渡区宽度和电阻率均匀性控制的问题,综合运用HCl气抛、主氢气流的变流吹扫及赶气、低温本征等工艺,成功实现了对硅外延过渡区宽度、厚度及电阻率均匀性等参数的控制。通过优化外延工艺,抑制非主动掺杂,最终外延层过渡区宽度可小于1.6µm,片内硅外延层的厚度和电阻率不均匀性均小于 1.5%,可以满足肖特基二极管工艺中对正向压降和击穿电压一致性等要求。■