由触发器构成的异步计数器的一种新分析方法

2020-05-07赵显红张晓红张立文

赵显红,张晓红,张立文

(河南科技大学 电气工程学院,河南 洛阳 471023)

0 引言

数字电路系统中,计数器是使用最广泛的时序逻辑电路,其分析方法非常具有典型性。由触发器构成的计数器分为同步和异步两类。同步计数器中全部触发器均用同一个外部时钟脉冲触发;而异步计数器中各触发器则可以采用不同的时钟信号。因为同步计数器中各触发器采用同一时钟,在分析过程中通常不考虑外部时钟的影响,分析过程较为简单;但是,由于异步计数器中触发器的时钟信号不是同时起作用,工作节拍不一致,分析时必须同时考虑触发器的输入、电路的初态、时钟信号等,这就使得分析过程变得更复杂更困难。传统上的异步计数器的分析方法与同步计数器的分析方法有较大的差异[1]。

教科书计数器的分析方法通常采用迭代的方法,同时考虑时钟信号的影响,计算量非常大[1-3];文献中有采用卡诺图分析法[4],其实质仍然是填写真值表方式;唐志兴采用矩阵分析法,从数学模型出发,解决含有未知原状态变量的问题[5];严单贵等的分析方法是采用将次态方程化为状态变量的最小项的标准形式,但是仅用于同步计数器[6];张继军将同步与异步时序逻辑电路的分析方法进行了统一,在分析电路中仍比较繁琐[7]。

在现有的分析异步计数器的方法中,大多比较复杂。没有统一的思路[8,9]。常常采用的方法仍然是迭代法。而利用上述同步计数器的分析方法,因为时钟信号的影响,无法按照次态方程、状态转换表的填写方法一次性完成。

本文以由多个触发器构成的异步计数器为例,给出一种新的分析方法,仅通过修改驱动方程,而其它分析过程不变。这种新的方法来分析计数器,获得了与同步计数器一样简单的状态转换表的填写,简单完美地实现了同步和异步分析方法的统一。

1 同步计数器的分析方法

分析计数器的两个最重要的指标是计数器的模值和自启动特性,状态转换表能完整表述这两点。通常的分析方法是:1) 写出驱动方程;2) 求出状态方程(即次态方程)和输出方程;3) 填写状态转换表。

状态转换表的填写,可以通过两种方法完成:1) 可以通过给定初始值,通过代入次态方程获得次态值,将次态重新作为初态,反复迭代从而获得状态转换表。2) 通过将次态方程化为状态的最小项之和的标准形式,类似填写组合逻辑电路的真值表的方法,直接填写状态转换表。后者是较为优秀便捷的方法[6]。

图1 同步计数器

第一步,首先求出各JK触发器的驱动方程,如下方程组所示:

(1)

将式(1)带入JK触发器的特性方程Q*=JQ′+K′Q中去,于是得到电路的次态方程,并化成最小项之和的标准形式。

根据逻辑图写出输出方程为Y=Q3Q2=∑m(6.7)。

第二步,创建状态转换表。

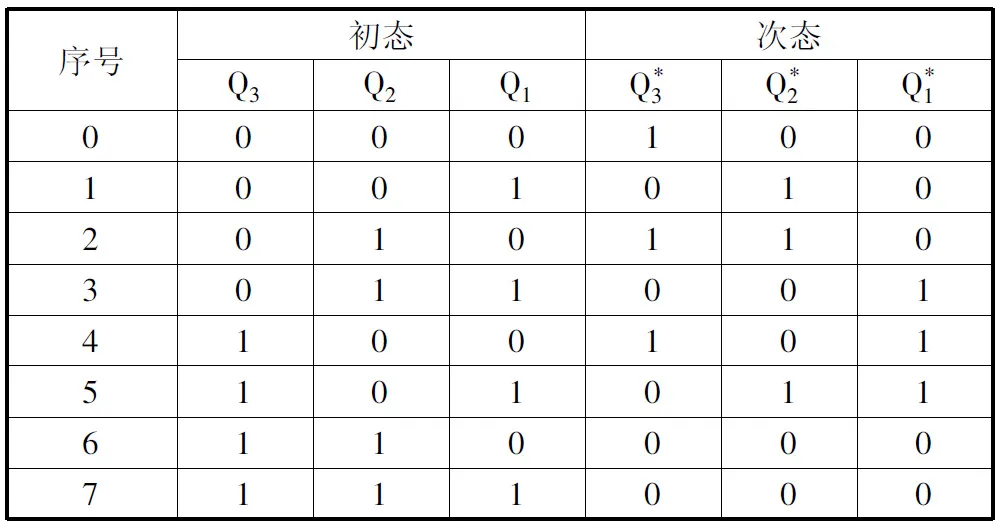

表1 真值表1

2 异步计数器的分析方法

逻辑原理:设n个触发器构成的计数器,第i个触发器,驱动方程为Mi1,时钟信号由前面所有起作用的触发器的时钟信号决定,设其分别为clkr0、clkr1、clkr2、……clkrj,其中1≤j≤n。时钟脉冲触发时,主触发器高电平触发从触发器低电平触发,则采用原变量;主触发器低电平触发从触发器高电平触发,则采用反变量。时钟边沿触发时,下降沿采用原变量,上升沿采用反变量。

将时钟信号作为驱动方程的一部分必要条件,则原驱动方程变为:

(3)

将新的驱动方程带入相应特征方程,即得到次态方程。其余过程完全类似同步时序逻辑电路。使用JK触发器构成的异步十进制加法计数器为例来说明新方法。

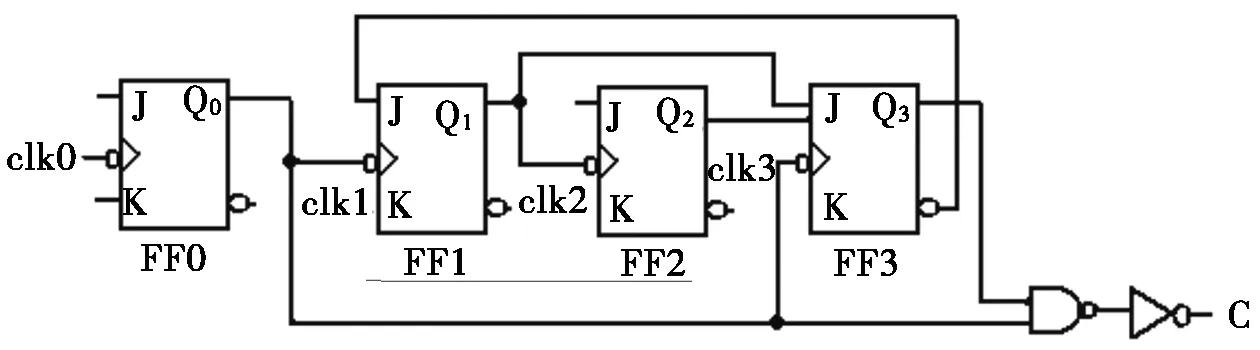

图2 异步计数器

第一步,变化后的驱动方程。

触发器FF0:时钟clk0下降沿触发,因为该时钟为整个电路的外部时钟,故令clk0=1。原驱动方程J0=0,K0=1,代入(3)式得到新驱动方程:J0=1,K0=1。

触发器FF2:时钟由clk0、clk1和clk2的下降沿触发,clk0·clk1·clk2=1·Q0·Q1。原驱动方程J2=1,K2=1,代入(3)式得到新驱动方程:J2=Q1Q0,K2=Q1Q0。

触发器FF3:时钟由clk0和clk3的下降沿触发,clk0·clk3=1·Q0。原驱动方程J3=Q2Q1,K3=1,代入(3)式得到新驱动方程:J3=Q2Q1Q0,K3=Q1Q0。

第二步,获得次态方程。

将新的驱动方程带入JK触发器的特性方程Q*=JQ′+K′Q中去,得到电路的次态方程,并化成最小项之和的标准形式。

(4)

将相应最小项的位置填入1,其余的地方均填入0。可得如表2所示状态转换表。很方便得出分析结果,该时序逻辑电路为加法计数器,计数模值为10,且具有自启动能力。

3 结论

推导了异步时序逻辑电路计数器的次态方程的求取过程。通过修改异步计数器的驱动方程,将次态方程简化为最小项之和的标准形式,简单快捷地填写真值表,获得时序逻辑电路的变化规律,同时便于检查电路的自启动性。实现了由触发器构成的同步和异步计数器分析方法的统一。