基于USB接口功率任意波发生器设计

2020-04-29胡永建孙成芹胡奕然

胡永建, 孙成芹, 胡奕然

(1.中国石油集团工程技术研究院 北京石油机械有限公司,北京 102206;2.北京市八一学校,北京 100080)

0 引言

在石油钻井领域,井下信号的短距离无线传输技术不仅有利于在高频磁耦合信道中使用常规钻具代替造价昂贵的特殊有缆钻具[1],也有利于实现跨越螺杆钻具的近钻头参数测量[2]。井下无线信道由钻井液、钻柱、地层等共同组成。与水声信道类似[3],该信道也具有时间变化大、衰减大、频率低、传播路径丰富等特性[4]。不同信道条件需要不同通讯方式,软件无线电(software defined radio, SDR)适合在同一硬件平台实现不同频段、不同调制方式的通讯[5]。对于井下无线通讯SDR发射机研制而言,需要尽可能地通过软件方式实现除模拟前端(analog front-end,AFE)和数模转换器(digital-to-analog converter,DAC)外的所有功能。

井下SDR发射机研制的常规技术路线是利用上位机(如兼容机)设计信号调制等算法,然后将算法移植到微控制器(microcontroller unit,MCU)、现场可编程逻辑阵列(field programmable gate array,FPGA)、数字信号处理器(digital signal processing,DSP)等嵌入式硬件中,随后通过高集成度发射机输出功率信号。使用任意波信号发生器(arbitrary wave generator,AWG)可以验证算法,如Keysight 81150A脉冲函数任意噪声发生器可以输出14位、512 k采样深度、2 GSa/s采样率的任意波形信号[6]。由于输出功率限制,该信号发生器即便在增加高电压选件后输出功率也仅有0.25 W,不能满足井下SDR发射机的功率需求;使用附加的独立放大器又无法满足高集成度一次性硬件开发验证的需求。

本文设计的USB接口功率任意波发生器的核心硬件与井下SDR发射机完全相同,避免了硬件的二次开发验证。上位机通过USB接口写入设计好的波形数据,功率任意波发生器通过单个高集成度芯片实现DAC、功率放大器(power amplifier,PA)、滤波器等功能,输出功率高达6 W。使用该功率任意波发生器能够缩短井下SDR发射机的研制周期。

1 结构及原理

井下高温高压环境对电子仪器的可靠性是一个挑战,井下SDR发射机的可靠性可以通过高温元器件选型和高集成度设计来提升。

美国德州仪器公司(TI)设计的AFE031电力线模拟前端芯片[7-9]耐温达125℃,内部集成了DAC、PA、可编程增益放大器(programmable gain amplifier,PGA)、滤波器等多种部件,是专为电力载波通讯设计的高集成度芯片。其频率范围满足EN50065 CENELEC A、B、C、D波段的需求,支持频移键控(frequency shift keying,FSK)、扩扩频型频移键控(spread frequency shift keying,S-FSK)及正交频分复用(orthogonal frequency division multiplexing,OFDM)等调制方式,在1.5 A输出时摆幅高达12 Vpp,特别适合驱动低阻抗线路。本文设计的USB接口功率任意波发生器的核心硬件就基于该芯片,与井下SDR发射机结构一致。外部设备通过串行外设接口(serial peripheral interface,SPI)接口与AFE031内部寄存器和DAC通讯。

美国芯科实验室(Silicon Labs)设计的CP2130桥接芯片[10]允许上位机通过通用串行总线(universal serial bus,USB)接口与AFE031芯片的SPI接口通讯。厂家提供了Windows兼容的应用程序编程接口(application programming interface,API)库,对于Linux等平台则提供了LibUSB库。

以150 kHz作为井下SDR发射机的最高发射频率,根据奈奎斯特采样定理,采样频率不能低于300 kHz。由于上位机并非实时操作系统,通过CP2130 UAB-SPI桥接芯片直接向AFE031的DAC写入数据无法满足任意波形发生器对速率和时钟同步的需求。经过实测,使用Windows10操作系统的主流商用计算机通过USB接口向CP2130连续发送指令,一条SPI输出指令更新一次DAC的数据,指令最小时间间隔约为50 μs,即此时任意波形发生器的更新频率(采样频率)低于20 kHz,并且时钟频率无法保持恒定。为了解决该难题,USB接口功率任意波发生器创新性地使用大容量同步高速先进-先出存储器(first input first output,FIFO)作为SPI接口数据缓冲区,实现了:1)USB接口下载波形数据;2)FIFO以SPI协议格式存储波形数据;3)FIFO通过SPI接口控制DAC回放波形数据的过程,该过程通过上位机控制,无需任何嵌入式编程控制。系统结构如图1所示,FIFO将低速的SPI输入指令转换成高速的SPI输出指令,控制AFE031内部的DAC产生信号并经过PA放大输出。AFE031及其外围电路组成了与井下SDR发射机相同的核心硬件部分。

图1 系统结构图

FIFO选用了美国IDT公司的IDT72V2111芯片,该同步FIFO芯片存储深度为512 k,允许级联扩展存储深度,支持可扩展的9位数据存储[11]。选用其中的3位数据来存储所需的SPI通讯的过程信号。

上位机通过CP2130从USB接口转换为SPI接口,通过FIFO与SPI接口的AFE031通讯。AFE031具有两种通讯模式:一种内部控制寄存器的读写操作;另一种是DAC输出的只写操作。对于功率任意波发生器来说,可以通过多次写入内部控制寄存器的操作来保证写入正确,无需读取操作。这样从CP2130到AFE031的SPI操作就是单向数据流动,只需要CS、CLK及MOSI共计3条通讯线,满足FIFO的先进先出的使用条件。上位机发来的非实时SPI指令先存储在FIFO中,然后按照所需的时钟频率实时发送给AFE031,以此来设定AFE031内部DAC特定的数据更新频率,也即信号的采样频率。

CP2130具有多达11个输出引脚,除了用于SPI操作外,部分引脚作为通用型输入输出引脚(general-purpose input/output,GPIO)控制FIFO的操作,其中GPIO.5可以复用为CLKOUT时钟信号输出,为FIFO提供稳定的读写时钟。

2 系统设计

2.1 硬件电路

图2给出了USB接口功率任意波发生器电路示意图。

图2 电路示意图

CP2130内部的稳压器将USB接口的5 VVBUS总线电压降压为3.45 V的VCC输出,为所有数字电路供电。使用默认的输出端口复用设置,GPIO.1和GPIO.1分别控制FIFO的写入使能及读出使能,可以通过分频器设定输出频率的内部振荡器CLKOUT为FIFO提供读写时钟,FIFO在该时钟的上升沿完成读写操作。另外GPIO.6控制AFE031的DAC引脚,选择确定SPI接口的通讯对象:AFE031的控制寄存器或DAC。

IDT72V2111的D0-2是FIFO的3位输入,Q0-2是FIFO的3位输出。FWFT/SI引脚接地选择标准FIFO模式,OE引脚接地使能FIFO输出。

AFE031的内部PA由外部15 V的VPA供电。其内部相关模块如图3所示。

图3 AFE031相关功能模块图

当DAC引脚为高电平时,通过SPI数字接口可以读写控制寄存器;为低电平时,SPI接口直接同DAC通讯。控制寄存器可用来设定PA、Tx各部件的启用与否等功能。

AFE031支持两种工作模式:DAC及脉冲宽度调制(pulse width modulation,PWM)。前者使用内置的10位DAC,后者通过PWM方式输出模拟信号。当Enable1控制寄存器的第5位(DAC)设定为1时,DAC的输出端与TxPGA的输入端相连,此时使用信号失真度更低的DAC模式。对井下SDR发射机的低频载波频率,10位精度的DAC可以满足需求。

Tx低通滤波器的截止频率通过Control1寄存器设定为CENELEC B、C、D波段,其最高截止频率为150 kHz左右[12]。滤波器的Tx_F_IN2引脚需要接地,输出通过电容CIN直接与PA输入端相连,也可以视需要使用外部低通滤波器。电容CIN为功放的传输函数引入了单极点的高通特性,其截止频率fHP与由CIN和PA的输入阻抗RPA(20 kΩ)共同确定。

(1)

其中:CIN单位为nF,RPA单位为kΩ,fHP单位为kHz。当CIN设定为3.3 nF时,高通截止频率为2.4 kHz。

功放是高电压、大电流的反相放大器,电压增益固定为6.5 V/V,满功率带宽为300 kHz,将Enable1寄存器的第0位(PA)设定为1可以使能输出,其输出可以通过RSET电阻来设定电流限制。限定电流ILIM由下式确定:

(2)

其中:RSET单位为kΩ,ILIM单位为A。

DAC的输出电压需要与功放匹配,通过GAIN SELECT寄存器可以将TxPGA的增益设定为0.25、0.5、0.707及1 V/V。TxPGA的输出与Tx滤波器的Tx_F_IN1引脚相连。

AFE031内部的发射机PGA(TxPGA)、发射机滤波器(Tx滤波器)以及功放等均是通过运算放大器实现的,运放所需的偏置电路在图3中未画出。

2.2 更新频率与FIFO操作

IDT72V2111的FIFO读写频率最高可达100 MHz,选用50 MHz的IDT72V211L20即可满足需求。AFE031的SPI时钟频率最高20 MHz,内部DAC的数据更新速率为1.5 MSa/s。CP2130内部的SPI控制器时钟频率最高12 MHz;内部USB控制器支持最高12 Mbps的USB2.0全速模式。

AFE031的DAC更新只需10位数据,但CP2130的API库仅支持字节发送。图4给出了上位机连续发送2字节16位数据(0xFF、0x00)时CP2130 SPI输出接口的波形示意图,时钟相位上升沿有效(CPHA=0),时钟极性高电平有效(CPOL=0),AFE031会自动忽略多余的发送位。

图4 连续2字节SPI写入指令

CS信号低电平启动SPI传输,在SCLK时钟上升沿读入MOSI数据,发送2字节数据后CS重新拉高。其中:Tt是CS低电平时间,Ti是两条连续指令的时间间隔,Tb、Tm与Ta是2字节数据的前、中及后的时间间隔。由于无法得到CP2130的内部逻辑及时序关系,对CP2130允许的7种速率f,使用上位机连续发送指令,不使用SPI延迟,测得各个时间间隔如表1所示。

表1 不同速率的时间间隔测量

如果将CP2130 SPI的输出直接与AFE031相连,在CS信号拉高的上升沿,AFE031的DAC完成数据更新。此时DAC的更新频率fupdate由下式确定:

(3)

由此得到不同SPI时钟速率的DAC更新频率如图5所示。

图5 不同SPI时钟速率的DAC更新频率

由于Ti及Ta的限制,随着SPI时钟速率f的增加,DAC的更新速率增加变缓,在测量中发现Tt的测量值也愈发不稳定(即指令周期不稳定),意味着DAC更新速率的稳定性变差。该结论与上文分析相同。作为缓冲的FIFO的引入解决了该问题。

首先,FIFO作为低速写入与高速读出的缓冲。将CP2130的SPI接口数据按照与SPI时钟速率相匹配的较慢的写入时钟送入FIFO,然后以更快地读取时钟发送给AFE031以保证正常的DAC更新频率。FIFO的读取与写入时钟均选用复用为CLKOUT的CP2130 GPIO.5。需要注意的是,该时钟是独立的,与SPI的SCK并不同步。

其次,FIFO可以消除指令周期不稳定的影响。选用最低的SPI时钟速率93.75 kHz,FIFO的写入时钟CLKOUT为其4倍频(375 kHz),这样可以消除1/4周期内的指令周期的抖动,体现在写入FIFO的CS信号上升沿数据(DAC更新点)具有稳定的重复周期,在FIFO数据回放时,只要保证读取时钟稳定就能保证稳定的DAC更新频率。

2.3 上位机软件

美国芯科实验室提供了上位机软件所需的CP2130驱动及链接库。对于Windows应用,提供了SLAB_USB_SPI.dll API库及C#演示程序,后者提供了大多数函数操作的示例代码[13-14]。函数分为数据传输及控制传输两类。

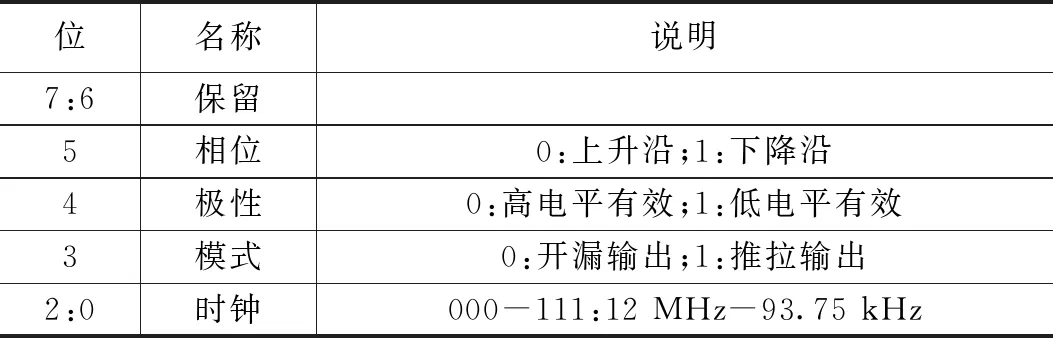

本设计使用VB.NET完成了功率任意波发生器的上位机软件。对于SPI通讯设置,API库提供了CP213x_SetSpiControlByte控制传输函数来设定SpiControlWord控制字,其功能如表2所示。

表2 SpiControlWord控制字

使用推拉输出模式,电路中无需上拉电阻。

对于SPI写入操作,API库提供了CP213x_TransferWrite数据传输函数,按照字节写入。写入成功则返回USB_SPI_ERRCODE_SUCCESS。

CP2130的GPIO引脚可以通过配置其内部的一次性可编程只读存储器(OTP ROM)来配置,本设计使用默认配置。通过CP213x_SetGpioModeAndLevel函数设定引脚功能(输入、开漏输出及推拉输出)和状态;通过CP213x_SetClockDivider函数设定CLKOUT的输出频率,由于设定的是分频系数,不能保证时钟输出的步长恒定,同时在USB接口挂起时无输出。

功率任意波发生器的程序就是对FIFO的读写控制,读写时钟都是CLKOUT,GPIO.1作为写入使能(WEN),GPIO.2作为读取使能。使能后就可以写入或读取3条SPI信号线的过程数据了。图6给出了上位机软件工作流程图。

图6 软件流程图

对于周期或重复信号,无需输入完整的波形数据,可以通过IDT72V2111的RT引脚(使用CP2130的其它空闲GPIO引脚)使FIFO中的单周期数据指令重新发送。作为FIFO读出时钟的CP2130内部振荡器CLKOUT的输出频率是通过分频器设定的,为了实现任意输出周期,需要在写入波形指令前预先设定单周期波形数据的采样率。IDT72V2111的重新发送响应时间是确定且满足设计参数要求的。

通过芯片选型及程序设计,本USB接口功率任意波发生器实现的最大输出功率为6W,输出精度10位,具有512 k的采样深度,最高采样频率为500 kSa/s,满足井下SDR发射机设计需求。

3 试验验证

使用本USB接口功率任意波发生器可以产生所需的高达6 W的输出波形,输出功率由设定的输出信号幅度确定。对于周期性信号,其周期可以通过CLKOUT的输出频率和每周期采样点来确定。输出频率越高、每周期采样点越低则输出频率越高。

通过预设不同的波形,使用示波器测量输出,其输出精度与设计一致,达到了设计要求。图7给出了100 kHz正弦波整形后的输出信号,输出10 V峰峰值,负载50 Ω。

图7 100 kHz正弦波信号输出测量

该任意波发生器已经用于高频磁耦合有缆钻杆系统研制,在井下信号的短距离无线传输的SDR大功率发射机设计中,实现了高集成度一次性硬件开发验证的目的,缩短了研发时间,带来较大的经济效益。

4 结论

USB接口功率任意波发生器设计基于美国芯科实验室的CP2130 USB-SPI桥接芯片、美国IDT公司的IDT72V2111同步FIFO芯片和美国德州仪器公司的AFE031电力线模拟前端芯片,无需嵌入式编程控制,能够实现上位机通过USB接口下载波形数据并通过功率放大器输出波形信号的功能。CP2130桥接芯片实现了上位机USB接口与功率任意波发生器的通讯,FIFO芯片起到了匹配SPI通讯速度和稳定DAC更新速率的作用。AFE031芯片及其外围电路组成的高集成度核心硬件与井下SDR发射机完全一致,输出功率高达6 W。该功率任意波发生器实现了一次性硬件开发验证,缩短了井下SDR发射机的研发时间。