布局5nm,量产7nm、10nm 2020年半导体制造工艺技术前瞻

2020-04-15张平

张平

晶体管制造工艺在近年来发展得不是非常顺利,行业巨头英特尔的主流产品长期停滞在14nm上,10nm工艺性能也迟迟得不到改善。台积电、三星等巨头虽然在积极推进7nm乃至5nm工艺,但是其频率和性能表现依旧存在较大的改进空间。从2019年底到2020年初,业内也召开了多次与半导体制造业相关的行业会议,对2020年和以后的半导体工艺进展速度和方向进行了一些预判。今天本文就综合各大会议的消息和厂商披露内容,对2020年半导体工艺制程相关内容进行汇总,以帮助大家了解未来半导体产业发展的脉络。

半导体工艺制造工艺是制约半导体产业发展的决定性因素之一。从2015年甚至更早时间开始,业内人士就开始对摩尔定律失效、半导体工艺制程发展速度放缓提出了担忧。虽然在商业宣传中,很多厂商依旧在快速迭代着不同代次的制程,但实际上,抛开商业宣传因素,半导体工艺制程的发展速度依旧比之前慢了不少。比如目前市场上大部分GPU和CPU产品依旧在使用五年前的14nm工艺或者其改进版本。新的lOnm、7nm工艺虽然已经上市,但是综合频率、功耗、晶体管密度等因素来看,其表现依旧不能令人满意。进入2020年,也就是21世纪20年代的第一年,半导体工艺制程发展的状况又会如何变化呢?是否会带来一些新的进展呢?

英特尔:10nm快速崛起重返Tick-tock时代

英特尔的发展步伐一直是业内关注的焦点。2019年下半年英特尔先是在IEEE国际电子设备会议也就是IEDM上,公开了一份在之前2019年9月份的路线图上修订的新版路线图,然后又在公司内部的电话会议上谈及了新的7nm乃至5nm工艺,这几次会议和路线图,给出了不少有参考价值的信息。

英特尔路线图:从7nm到1.4nm

首先将目光放到最远,英特尔预计其工艺制程节点将以2年一个阶段的速度向前推进。从2019年推出lOnm工艺开始(实际产品在市场上非常少见),2021年英特尔将发展至7nm,随后在2023、2025、2027和2029年工艺将持续快速推进至5nm、3nm、2nm和1.4nm。尤其是1.4nm,这是英特尔首次在相同类型的幻灯片中展示1.4nm的技术预期。从工艺角度来说,如果1.4nm的特征值得以实现,这意味这个节点的典型值只有12个硅原子连接起来的宽度那么“薄”。

值得注意的是,在今年的IEDM大会上,一些被称为“2D自组装(2Dself-assem bly)“的材料被提及,这种材料的尺寸大约为0.3nm。在工艺界,这样小尺度的材料并非首次被提出,但是在硅材料方面的应用和相关话题还是首次。延展来说,有关2D自组装材料的研究目前在《自然》和《科学》两大顶级杂志上相当热门,其主要内容极为艰深。一些有关2D自组装材料的研究包括:通过将半晶嵌段共聚物BCPs与均聚物选择在合适的溶剂中进行外延结晶,从而引发自组装过程,创建一个自定义尺寸的超分子物体;或者是基于范德华力的相互作用,氢键和偶极相互驱动,在双组份分子系统中实现二位自组装,实现有序均质分子网;另外還有二位等离子体纳米片的自组装过程研究。显然,无论哪种2D自组装过程,在硅材料上的应用都处于初级阶段,英特尔在这方面还需要进行大量、极高难度的研究。因此,对1.4nm的制造工艺目前所采用的实现方式尚缺乏定论,也不需要太过乐观。

除了新的工艺路线图外,在每代工艺之间,英特尔还布置了“+”和“++”这种工艺优化的版本,以便更进一步推高每个节点的性能。唯一例外的是lOnm,实际上我们目前看到的lOnm工艺已经是lOnm+了,第一版lOnm工艺由于最终性能和功耗等问题,已经被英特尔彻底放弃。因此我们将在2020年和2021年分别看到lOnm的第二个改进版本lOnm++和第三个改进版本lOnm+++。英特尔认为,他们可以按照年度节奏进行这样的操作,但是也有另外的同步团队来确保一个完整流程节点的工作。数个团队在同一时间内分别就不同的目标进行工作,同时也互相保持沟通。

英特尔的幻灯片还有一个有趣之处在于提到了反相移植。一般来说,英特尔的芯片在设计时已经和固定工艺制程节点绑定。但考虑到节点延迟等问题,因此英特尔会考虑新的芯片设计也能够在上一代的工艺制程上进行制造,当然所谓上一代”的可选工艺制程范围是有限的。尽管英特尔此前表示,他们正在将芯片设计和制造工艺节点脱钩,但是在某些情况下,必须要先确定制造工艺节点,才能开始进行硅片布局,这就意味着工艺节点和芯片设计相互锁定,尤其是在掩模设计的时候。

英特尔还说明了一些反相移植的例子,比如任何第一代7nm工艺节点都将可能反相移植到lOnm+++,任何第一代5nm工艺节点都可以反相移植到7n m++,以此类推。从目前的情况来看,英特尔在lOnm工艺制程上耗费了太多的时间,对整个产品后续发展带来了比较重大且不利的影响。一些传言显示英特尔可能会将一些为lOnm设计的处理器产品移植到目前成熟的14nm+++工艺上来发布,但目前英特尔没有对这个传言有明确的表态。

除了上述内容外,路线图还显示英特尔正在进行lOnm+++优化工艺和整个7nm工艺的产品开发。从设计角度来看,每一代“+”的开发难度较低,相对应的节点开发难度比较高。接下来英特尔将基于lOnm++开发7nm工艺、基于7nm设计开发5nm工艺,基于5nm工艺来开发3nm工艺,毫无疑问,每一个“+”或者“++”所拥有的技术更新都将有可能进入下一代节点的设计之中。

在7nm节点之后的5nm节点,目前已经有很多讨论了,目前来看5nm的一些改进比如制造、材料和一致性等,最终可能都将呈现在英特尔新的工艺中,但这些改进如何实现,依旧取决于英特尔选择怎样的合作伙伴(历史上都由应用材料公司接手)。另外,5nm工艺在2023年呈现时,也正是ASML开始销售其High NA也就是高数值孔径透镜的时间。所谓高数值孔径透镜,是指新的透镜规格,这将带来光刻机微缩分辨率、套准精度两大核心参数的提升,最高可达70%。目前尚不确定英特尔是否会在5nm或者更远期的3nm上使用新一代高数值孔径设备,这还需要进一步观察。

在2023年之后,英特尔就将处于“寻路”和“探索”模式了o和之前数次类似情形相似,英特尔—直在考虑新材料的引入、新的晶体管设计等。本届IEDM上,出现了很多针对全栅极晶体管的讨论,无论是纳米片还是纳米线,随着FinFET技术在更新工艺下的逐渐失效,全栅极可能会逐渐成为主流。如果英特尔在未来的5nm乃至更新工艺上这样做的话,应该是顺理成章的。

重返Tick-Tock时代英特尔将加速工艺研发速度

在2019年度最后—次的CEO电话会议上,英特尔也带来了新工艺和新产品的信息,其中最重要的就是在放慢了研发和产品节奏多年之后,英特尔决定重回充满活力和竞争力的Tick-Tock日寸代。

简单来说,“Tick-Tock”是—种产品架构和产品工艺交替换代的发展节奏,以一个产品年作为一个发展节点。其中第一年为“Tick”年,在产品生产上使用新工艺,那么第二年会被称为“Tock”年,将使用同代次工艺的优化版,但采用全新的处理器微架构,第三年又会回归到“Tick”,在同代次架构优化的基础上,采用全新节点的工艺,随后的第四年也会依次更替下去。“Tick-Tock”的“工艺一架构”交替发展策略曾经为英特尔带来了巨大的成功,从2005第一代65nm Core架构到2010年的第四代Sandy Bridge架构,英特尔一直在坚持一代架构更新、一代工艺更新的步伐。不过随着Sandy Bridge架构推出后英特尔在架构研发策略上逐渐变得保守,再加上在14nm工艺后英特尔陷入制程瓶颈,“Tick-Tock”逐渐不再被提起,被英特尔事实上放弃了.

回到正文,在电话会议上,英特尔提出了将重新回归“Tick-Tock”的发展节奏。目前的Tick是10nm产品,其中包括第十代Ice Lake酷睿处理器、2020年第三季度交付的lOnm Agilex FPGA產品。此外,2020年英特尔还将发布新的lOnm工艺AI推理加速产品、5G基站SoC、新的Xeon处理器以及GPU产品。

接下来的2021年,英特尔将进入Tock步伐,工艺进步至7nm,首款产品为面向数据中心的GPU。在7nm工艺方面,英特尔提出,光刻技术将成为7nm乃至更新工艺制程的挑战。英特尔计划在进入7nm后才使用EUV光刻(意味着目前的lOnm产品依旧基于传统的DUV光刻技术完成),时间大约是2021年的第四季度(这一点内容和之前路线图上的时间相吻合)。不过和传统的“Tock”不同的是,英特尔没有提到CPU产品何时进入7nm时代。

另外,英特尔还解释了有关lOnm工艺延期以及未来的7nm工艺研发的问题。正如英特尔多次表示的那样,lOnm延期的原因是由于目标设定过高。在从22nm转向14nm时,英特尔带来了2.4倍晶体管密度,在14nm转向lOnm时设定了新工艺提升2.7倍晶体管密度的目标。但此设定过于激进,因此到现在都无法顺利量产。在吸取了这个教训之后,英特尔在自己的7nm工艺设定上要更为保守一些,其密度增加会量力而行。显然,在延迟了4年之后,lOnm工艺预计将在2021年进入大规模批量生产阶段(HVM),7nm也有望顺利进行。英特尔还提到,7nm工艺依旧将使用FinFET,随后的5nm和3nm阶段,英特尔可能会引入纳米片技术,也就是全栅极晶体管,但具体如何实施尚不得而知。

台积电——全面展示5nm工艺,3D易购封装技术日至成熟

作为目前半导体代工业界的一哥,台积电近年来在技术上突飞猛进。在2019年底到2020年初,台积电在多个会议和展会中,全面展示了自研的5nm工艺以及全新的3D封装技术。

台积电展示5nm工艺:EUV、高迁移通道FinFET

台积电对5nm的研发和生产都启动得非常早,在2019年4月,台积电就宣布启动了5nm工艺的风险生产。同样在IEDM 2019上,台积电选择了经过1 000小时高温操作生命周期测试( High Temperature Operating Life Test,简称为HTOL测试),并即将在2020年第一季度投产的工艺进行了详细介绍。这个全新的5nm工艺使用了主要设计规则(栅极、鳍片和M x/Vx间距)的智能缩放来完成的,能够实现7nm到5nm全节点的缩放,并且还能够提高良率。根据试产数据,新工艺生产的SRAM具有0.021平方微米的单元尺寸以及较低的缺陷密度DO。

台积电在5nm上全面使用EUV技术,大幅度提高了效率。台积电的资料显示,5nm工艺中,EUV在切割、接触、过孔和金属线掩模等步骤中,至少可以替代4倍的沉浸式DUV光刻。传统DUV光刻需要5层掩模,EUV光刻1层就可以完成,大幅度缩减了制造周期,并且带来了更好的图案保真度。

在FinFET技术的应用上,台积电从16nm工艺开始首次引入FinFET,随后经过了12nm、lOnm、7nm数代。目前,FinFET的关键性能通道迁移率数据在5nm工艺节点已经停滞不前了,鉴于此,业内其他厂商都在考虑使用全栅极方案。不过台积电另辟蹊径,采用了高移动性信道(High Mob…tyChannel,简称HMC)来解决了这个问题。为此,台积电还展示了FinFET的截面组成,其中和硅晶格相接的是全应变HMC晶格,后者的驱动电流要显著高于前者。同时台积电还展示了通道深度和通道应力之间的关系,所谓通道深度,是指鳍片顶部到底部的电流通道深度。

台积电的数据进一步显示了HMC晶体管的漏极电流Id与栅极电压vg之间的关系,新的HMC FinFET具有极为出色的Id-Vg特性,产生的驱动电流能够比Si FinFET高18%。环形振荡器品质因素也和晶体管电流泄露密切相关。台积电给出了七个不同的vt下截止电流loff-N和loff-P范围以及对待机电流的影响,显示出HMC FinFET技术下漏极感应势垒DIBL降低45mV和35mV,对于P沟道和N沟道晶体管,其摆动幅度分别为60mV和l68mV。

目前台积电展示的5nm工艺是7nm工艺之后的完整节点扩展,台积电为每种晶体管类型设置了7个不同的可用vt电压,这样厂商就可以结合不同的电压来满足SoC设计所需要的功率效率需求以及HPC设计所需要的峰值速度需求。根据台积电的技术展示来看,5nm N5工艺中的eLVT八类能够在相同的功耗下提供最多25%的频率提升,5nm N5 HPC工艺中的eLVT工艺相比N5 eLVT工艺能够进一步提升10%的频率。

eLVT是台积电在新的5nm工艺中推出的全新设计,N5和N5 HPC中均有相应的型号。所谓eLVT是指ExtremelyLow VT,也就是超低vt电压的晶体管。在N5中,eLVT带来了上文描述的25%的频率提升,在N5 HPC中进一步优化采用三栅极标准单元,因此又带来了10%的性能提升。eLVT也可以使用在3D堆叠芯片中,也能够为后续的3D堆叠产品带来性能提升。

互联延迟方面,在传统的产品发展路线中,由于工艺尺度越来越小,因此每一代产品互连延迟相比上一代产品都会变得更差。如果不加干预的话,从N28到N5工艺,后端金属RC和过孔电阻的表现都变得越来越令人担忧。在新的N5工艺上,台积电采用了创新的EUV优化方案,通过按照比例缩放势垒和衬底的ES L/ELK电解质和铜回流焊的尺寸,将互连延迟和电阻等情况维持在和7nm工艺相当的数值范围,大幅度优化了互连延迟并阻止了情况的进一步恶化。

寿命方面,台积电目前已经完成了1000小时的HTOL测试认证。相比7nm工艺而言,新的5nm工艺以及eLVT技术还能够带来改善应力老化特性的优势,SRAM和逻辑缺陷密度的DO数据也比预期表现更为出色。

综合来看,台积电的5nm制造工艺在PPAa(功率、性能、面积、成本、上市时间)目标上实现得非常出色,设计方面协同优化技术也就是DTCO也带来了智能缩放,避免了蛮力缩放导致的工艺成本增加和对产能的负Memory 应用与技术面影响。根据台积电数据,5nm制造工艺的晶体管密度为7nm工艺的1.84倍,性能方面在相同功率下速度提高15%,或者在相同速度下功率降低30%。

最后在工艺方面,再来看看远期的N3也就是3nm工艺的进展。台积电之前的2019年第四季度电话会议中提到了相关内容,目前台积电正在对N3制程进行评估,包括技术实现、成本、成熟度、性能等多个方面。在2020年4月29日,台积电还会在北美技术研讨会上给出更多的细节。目前已知的是,台积电依旧计划在N3阶段采用FinFET,有关全栅极晶体管的方案,台积电目前尚未提到。

3D异构封装技术进展

除了常规的半导体制造工艺外,半导体的封装也是业内研究的重点。台积电在2019年底介绍了自己掌握的数个3D异构封装技术,包括CoWoS、InFO-PoP和SoIC,下面来简单了解—下。

台积电提出的第一个封装设计是Chip-on-Wafer-on-Substrate,简称CoWoS,也就是芯片晶元和衬底三重堆叠技术。其中不同类型的芯片置于晶圆之上,晶圆提供这些芯片之间的互联,最终和电路板也就是基板的连接由中间的TSV硅通孔完成。台积电介绍了相关技术进展,尤其是CoWoS可以实现最大芯片尺寸2倍以上的中介层制造能力,这样可以使得更多的芯片封装在一整块硅片和衬底上,实现更高的集成度。

第二种特殊的3D异构封装被称作InFO-PoP,全称是Integrated FanOut-PoP。这项封装技术是之前InFO也就是集成扇出型封装的更新版本,InFO支持多种不同白勺芯片诵过盲接封装到晶圆上的方式,大幅度提高密度和缩小芯片体积。新的InFO-PoP技术则加入了用于顶部芯片和下部晶圆之间的TIV过孔,使得封装更为紧密、安全,是台积电在移动SoC等设备上主推的先进封装方式。

第三种则是SoIC。这项技术的主要特点在于将之前异构封装所使用的芯片和基板之间的微凸点连接更改为芯片之间的无凸点直接连接。这种新的技术进一步简化了材料的使用,减少了基板层,整体电气性能更为优越,并且能够实现更高的速度、带宽以及更高的封装密度、更低的堆叠高度等。

当然,这三种封装技术并非独立、排斥的,台积电目前准备的新技术将集中这三种封装技术的优点。比如将SoIC技术集成到扇出型封装或者CoWoS封装技术之中,实现整个封装技术的按需配置和统一化。这样一来,能够实现更好的電气性能、更小的芯片尺寸和更可靠的连接,在成本上也可能提高产品的竞争力,令用户更为满意。

三星——来自5nm LPE工艺的疑惑

三星在2019年4月份就宣布旗下的5nm相关工艺开发完成,相比自家的7nm工艺,三星的5nm FinFET工艺在可比条件下,芯片面积缩减25%、功耗降低20%、性能提高10%。除了相关产品外,三星还宣布整个5nm EUV工艺的EDA工具、IP、MPW以及PDK等全部都准备就绪。

虽然宣布时间非常早,但是迄今为止都没有厂商宣布使用三星5nm工艺生产产品,其中原因暂不得而知。不过业内另一份数据比较了三星的5nm、7nm工艺和台积电同代工艺的情况,从这里可以一窥三星目前在半导体制造工艺上的研发情况,形式显然并不乐观。

先来看三星和台积电的5nm工艺对比,表格如下:

从上述表格可以看出,三星的5nm LPE工艺相比台积电的N5工艺,整体表现还是略逊一筹的。在几个关键数据上,晶体管密度和相对成本上,台积电N5工艺的晶体管密度几乎达到了三星的1.37倍,但是成本方面台积电的相对成本反而更低一些。另外,台积电的M2P(金属间距,可以用于确定单元距离)参数为30nm,比三星的36nm更小,显示了台积电在晶体管微缩方面的优势。同理还有多晶硅间距,台积电的数据为50nm,也大幅度小于三星的57nm。综合来看,三星的5nm工艺目前表现情况不佳,因此在宣布后接近一年时间里,尚未有具体产品上市可能与此相关。

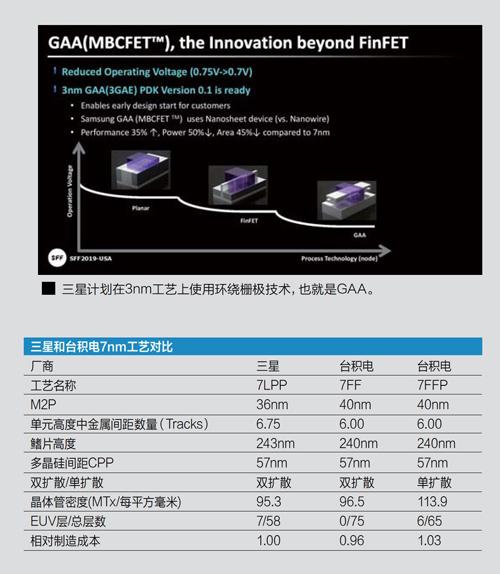

另一个比较来自于三星的7nm和台积电的7nm工艺,值得注意的是,台积电7nm工艺已经上市。从本页的参数对比表格来看,三星的7nm和台积电的7nm有一些差异,比如三星在使用了EUV版本之后,和台积电DUV版本的工艺相比基本处于一个水平线,但是成本略高一些。当然台积电的7nmFFP由于加入了EUV光刻层,因此整体的表现要更胜一筹。

但这都不是重点,重点在于单独比较三星的7LPP工艺和5LPE工艺,可以看出其中M2P、CPP等参数没有变化,尤其是CPP依1日维持在57nm的水准上。值得关注的变化来自于EUV层,两者都使用了58个总层数,但是EUV层在5nm工艺上使用得更多,达到了12层,比7nm LPP多了5层。这里有理由怀疑三星如此早推出的5nm LPE工艺更像是7nm LPP工艺的进一步深度改进版本,增加了EUV层并且微调了一些参数,但是大部分依1日沿用了7nm基本技术逻辑。当然,增加的EUV层带来了更高的晶体管密度,相比之前的7nm工艺,三星5nm LPE工艺的晶体管密度从95.3提升至126.5,实际数据为32%,比宣称的25%要高一些,但是显然低于台积电从7nm FF的96.5到N5工艺的173.1,提升幅度达到了78%。即使以7FFP为参照,提升也高达51%。三星的5nm LEP工艺更像是一个抢时间的“半代”改进版本,再加上其价格更高,目前的商务应用情况不佳也就可以理解了o

总的来看,2020年好消息还是不少的,英特尔lOnm进入了大规模生产阶段,7nm也在预研阶段且比较顺利。台积电方面7nm将正式投入生产,整体表现也不错,再加上封装技术的进步,目前台积电有望继续保持全球第一大半导体代工企业的地位。三星在5nm工艺上抢先发布,但是由于性能和商业策略问题,暂时还没有看到积极的消息,希望三星能够在2020年进一步推出改进的5nm工艺,争取更多客户的同时,也为代工市场带来一些竞争。毕竟“一枝独秀不是春,百花齐放才能春满园。”