基于FPGA的千兆UDP/IP协议栈的实现及其在高速图像传输中的应用

2020-03-25熊光阳李志茹张维纳

熊光阳,王 野,李志茹,张维纳

(桂林电子科技大学 电子工程与自动化学院,广西 桂林 541004)

0 引言

目前,系统设计中常用的高速数据传输接口技术有USB、PCI/PCI-E、千兆以太网和万兆以太网接口等。而现在的计算机都提供千兆以太网卡,利用千兆网接口有着接口普及、设计成本低等优势[1]。

为了实现千兆以太网图像数据的传输,需要在硬件上实现MAC(数据链路层)和PHY(物理层)。现有的千兆网接口往往采用具有MAC 功能的IP 软核来实现该部分的功能,该方案存在移植性差和消耗FPGA 资源量大的问题[2]。本文利用FPGA 可编程逻辑门阵列的特点,使用硬件描述语言实现MAC 功能,而物理层使用专用的PHY 芯片来简化UDP/IP 协议中对物理层设计的工作[3]。

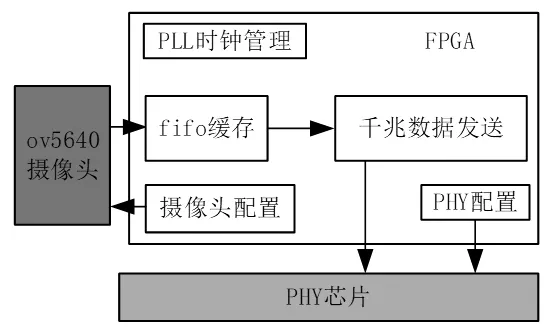

图1 总体设计框架Fig.1 Overall design framework

1 系统的总体方案设计

构成千兆以太网图像数据传输及图像采集接口总体设计框架如图1 所示。

FPGA 中设计逻辑接口对型号ov5640 的摄像头工作方式进行初始化配置,摄像头配置好后采集图像数据。图像数据进入FPGA 后,因为摄像头输出的图像数据和千兆数据发送模块的数据不在同一个时钟域,所以在数据进入FPGA 后存入FIFO 缓存,千兆数据发送模块读取FIFO 中的数据,在千兆数据发送模块中根据标准的UDP 数据包格式完成数据打包,该模块输出的UDP 数据包通过RGMII 接口传输至PHY 芯片,这里PHY 芯片执行的是千兆以太网的物理层功能,数据在通过PHY 芯片后就可以经由网线传输给下一级数据处理模块。PLL 时钟管理模块完成的是对FPGA 内部模块提供符合设计需要的稳定时钟。本设计选用的PHY 芯片KSZ9031RNX 支持多种工作方式,PHY 配置模块完成是对PHY 芯片的工作方式配置。

2 各功能模块实现

2.1 PLL时钟管理

PLL 时钟管理模块完成的功能是向本设计的其他模块提供时钟,其中摄像头系统时钟24MHZ,配置摄像头的IIC 接口时钟100KHZ。为了简化设计,对于这两个模块工作时钟来源使用的办法是调取PLL IP 核,经过外部输入的50MHZ 时钟倍频产生;对于千兆以太网,FPGA 与PHY 间通过RGMII 接口通信,RGMII 支持全双工,具有两条不同方向的125MHZ 时钟线,千兆数据发送和PHY 配置模块的时钟,来源于PHY 芯片向FPGA 输入方向的时钟。

2.2 FIFO缓存

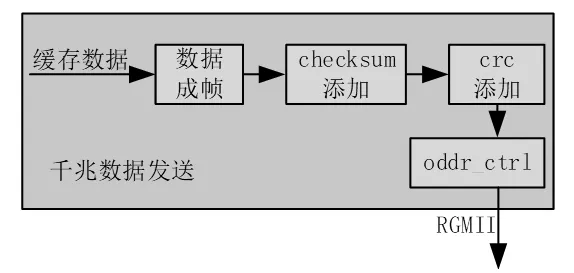

图2 千兆数据发送Fig.2 Gigabit data sending

当配置好摄像头的初始化后,摄像头就会按照一定时序一直输出图像数据。本设计配置的输出数据是RGB565格式,速率60sf/s,720P 的图像。而千兆UDP 数据包来源于对读取的缓存FIFO 数据根据标准UDP 协议的封装[4]。连续传入FPGA 的图像数据和需要封装成UDP 数据包并外传之间的速率和是时钟不同,因而,就需要将采集到的图像数据在FIFO 中缓存,再读FIFO 取出数据封装成千兆以太网UDP 包。由于图像输出时钟和从FIFO 提取数据的时钟不同,所以调用异步FIFO 来解决这一矛盾[5]。

2.3 摄像头配置

本文选用的摄像头是ov5640,支持IIC 通信协议访问内部的配置寄存器[6],综合考虑将其配置成主要参数为720P、60sf/s、rgb565、像素时钟84MHZ 的输出。

2.4 PHY配置

PHY 芯片支持全/半双工速率自适应工作方式,本文根据设计需要将芯片配置成1000Mbit/s、全双工工作方式。PHY 芯片支持软件和硬件配置两种方式,软件配置方式和上文摄像头配置类似,往相应寄存器写入设计的工作方式对应的寄存器值[7]。本文采用硬件配置的方式,即在芯片功能引脚串接一定阻值的电阻使其获得高电平状态,在芯片上电后,串接相应电阻而获得的电平状态就会写入其对应的寄存器,从而确定芯片工作方式。

2.5 千兆数据发送

千兆数据发送功能模块完成的是将FIFO 缓存中取出的数据进行UDP 封装再发送给PHY 芯片的过程,该模块框架如图2 所示。

数据成帧模块的功能是将缓存的数据组成初步的千兆以太网帧[8],这里的初步千兆以太网帧指的是没有加入IP CHECKSUM、UDP CHECKSUM 以及CRC 校验的数据帧。在checksum 添加模块中,根据UDP 协议计算出checksum的值,将这个计算出来的值填充进去初步以太网帧。CRC添加模块功能与checksum 添加模块类似,计算出crc 校验值,然后将此计算出的值填充进已经添加有checksum 的上一模块数据流。在本设计中选用PHY 芯片完成以太网的物理层功能FPGA 与PHY 通过RGMII 接口通信,oddr_ctrl 模块完成的是将上一模块输出的数据转换为符合RGMII 接口的数据形式。

表1 UDP/IP数据帧格式Table 1 UDP/IP Data frame format

2.5.1 千兆以太网协议

千兆以太网协议主要是UDP/IP 协议和RGMII 接口协议,UDP/IP 协议是将数据封装成符合IEEE802.3a 标准的数据包的规则[9];RGMII 接口协议是FPGA 与PHY 通信的一种接口形式。在经典以太网标准下,设计千兆以太网UDP/IP 数据帧格式见表1。

一个完整的UDP 数据包应符合表1 的格式要求,其中前同步码为连续的7 个55、1 个d8,它们共同表示一个帧的开始[10];目的地址6 个字节存放目的设备的物理地址,即MAC 地址;源地址存放发送端设备的物理地址;0800 表示IP 协议;包自增标志是为了数据接收端验证数据在传输中有无丢失;IP 长度描述的是IP 首部字节数、UDP 首部字节数和用户数据字节数的算术和;用11 表示UDP 协议;IP_CHECKSUM、UDP_CHECKSUM 以及CRC 是对数据差错的一个校验;IP 源地址和IP 目的地址分别表示数据发送端和接收端的IP 地址;PORT 源和PORT 目的分别表示数据在处理他们的应用程序传输的端口;用户数据填充需要传输的数据。

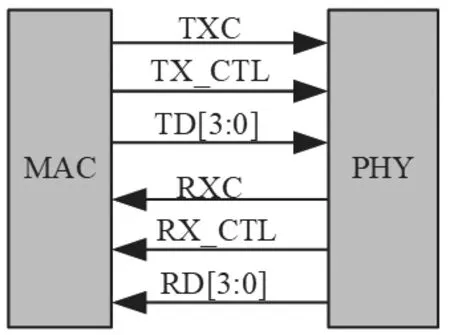

RGMII 是本设计UDP/IP 协议栈中MAC(数据链路层)和PHY(物理层)之间的一种数据传输接口协议,本设计中的千兆数据发送模块完成的就是MAC 功能,协议形式如图3 所示。

RGMII 采用4 位数据接口,工作时钟125MHZ,并且在上升沿和下降沿同时传输数据,传输带宽可以达到1000Mbps。图3 中TXC 和RXC 为数据传输时钟,TX_CTL和RX_CTL 为数据有效信号,TD 和RD 为双沿4 比特有效数据。本设计选用的PHY 芯片支持全双工数据传输方式。

图3 RGMII接口Fig.3 RGMII Interface

2.5.2 数据成帧

千兆数据发送模块提取采集的缓存在FIFO 中的图像数据,然后在数据成帧模块中完成对数据的初步封装,按照表1 所示的数据帧格式,在FPGA 中生成数据流的基本帧格式,除了IP_CHECKSUM、UDP_CHECKSUM 以及CRC校验位,数据帧的其他部分都可以在这一模块完成。

设计1 个UDP 数据流中含有1280 个字节的图像数据,设置时钟缓存FIFO 的深度为2000,当FIFO 中存够1280个数据后,缓存模块可以生产一个flag,数据成帧模块接收到flag 信号后就可以开成组帧,组帧到表1 序号17 的位置时就可以拉高一个使能,该使能信号是读FIFO 的使能,这样将读取到的FIFO 数据填充到数据帧的用户数据位置。

2.5.3 checksum添加

CHECKSUM 包 括IP_CHECKSUM 和UDP_CHECKSUM的计算以及将这两个的计算结果填充进数据成帧模块中原本用8’h00 代替的位置处。IP_CHECKSUM 和UDP_CHECKSUM 的计算是将一定范围内的数据按照每相邻2byte 即16bit 作为一组,把每组的这16bit 数据相加,如果计算和大于FFFF,那么就把超出FFFF 的部分与计算和的低16 位相加,直到结果为16bit。最后的结果取反即为CHECKSUM。其中,IP_CHECKSUM 计算的范围包括以太网数据帧中的IP 版本到IP 目的地址之间的数据,UDP_CHECKSUM 计算的范围包括从PORT 源到最后一个用户数据结尾之间的部分。

因为计算CHECKSUM 结束后,数据流已经到了一帧数据的末尾,这样就不能在正确的位置填充CHECKSUM。设计在计算CHECKSUM 的同时将数据存入RAM,待计算完成后读取RAM 数据,然后将计算好的CHECKSUM 填充进读出来RAM 数据的CHECKSUM 正确位置处。

2.5.4 crc添加

数据经由千兆网传输,实际上传输的是数据和校验码的组合——码字,这样的算法是对整个数据帧在传输过程中正确性的校验,其中校验码的生成依据的是CRC 校验算法,在数据接收端根据再计算一遍码字与发送端的码字相比较来判断传输差错与否。

图4 实验验证系统Fig.4 Experimental verification system

2.5.5 oddr_ctrl

在千兆数据发送模块中处理的数据是8bit 位宽,对应125Mhz 系统时钟,FPGA 与PHY 芯片通过RGMII 接口连接。RGMII 接口协议上文已有阐述,传输的是双沿4bit 数据。因此,需要在oddr_ctrl 模块中把系统的单沿8bit 数据转换成双沿4bit 数据,实现与PHY 芯片的正确通信,这里的处理办法是在vivado 中调取IP 核oddr。模块中设计的数据位转换条件是边沿触发,双沿数据指的是在时钟线上升沿和下降沿同时转换数据。使用RGMII 接口可以在保证千兆带宽的前提下,节省FPGA 的引脚使用。

3 实验验证

实验验证的主要内容是硬件设计的正确性。实验验证系统如图4 所示。

设计的实验是将千兆以太网数据发送向PC,在抓包软件wireshark 上抓取实时数据包,摄像头采集的分辨率是1280×720、格式RGB565 的图像。在设计UDP 包时,一包UDP 数据帧填充1280 个字节,一张图片需要填充这样的UDP 包1440 个,而UDP 数据帧除开用户数据外,还有帧头、校验字、IP 地址等这些表1 所描述的部分,一共1332 个字节;设计FPAG 的IP 地址192.168.0.1,即以太网的IP 源地址,向PC 发送广播包即IP 目的地址255.255.255.255;为了验证没有丢包设计自增1 标志每发送一包数据该标志自加1,该标志从1 计数到1440(1440 的十六进制是05a0)。观察wireshark 界面上抓取的数据帧,抓取的实时数据传输到PC 端wireshark 截取界面如图5 所示。

图5 是截图的一张图片发送的第一个UDP 数据包和最后一个数据包,图中方框标志2 处是抓取UDP 数据帧的长度,和实验设计FPGA 发送端一样;图中方框标志3 是以太网接口的IP 源地址和目的地址,和实验设计FPGA 发送端一样;图中方框标志4 是自增1 标志,其计数范围和设计一样;实验截取的数据包的范围在图5 中的标志1 处,(b)图相对(a)图共有数据包568231-566792+1=1440。实验结果表明本设计是正确可靠的,符合设计预期。

图5 抓包截取结果Fig.5 Capture results

4 小结

本文采用FPGA+PHY 的架构,利用FPGA 实现了千兆以太网传输系统。该系统具有较高的可靠性,且易于实现,对于一些成本低、体积小,速度要求较高的图像记录器设计具有重大的应用价值。