通用型高频宽带ADCP 信号处理系统设计与实现

2020-03-23王忠康

冯 宏,王忠康

(杭州应用声学研究所,浙江杭州310023)

0 引 言

海洋流场是海洋动力环境的基本要素,对海洋流场进行监测在海洋科学研究、经济建设及国防建设等领域均具有极其重要的意义。声学多普勒流速剖面仪(Acoustic Doppler Current Profilers, ADCP)是进行海洋流场监测的一种重要设备,它能够对海洋环境参数进行长期自主式观测和记录,可提供高分辨率、高精度、信息海量且完整的数据,在海洋科考、海上调查和军事海上安全保障等领域应用广泛,具有非常良好的市场前景。

宽带声学多普勒流速剖面仪是利用编码相干脉冲串信号进行收发和处理。宽带测流方式通过高分辨率编码形式与灵活的相干测量相结合的方式,以保证速度估计具有较高的精度[1]。高频宽带ADCP 对系统采样率和数据处理能力有非常高的要求。传统的处理方式是使用模拟手段实现正交混频滤波,将回波信号频率降低,转换成为相互正交的两路基带信号。这种方式虽然可以降低系统的采样率,但是难以实现正交通道的绝对平衡,且容易引入零漂和测量误差。

本文介绍了一种高频采集、数字解调滤波的通用型ADCP 信号处理系统的设计和实现过程。该系统以现场现场可编程逻辑门阵列(Field Programmable Gate Array, FPGA)+数字信号处理器(Digital Signal Processor, DSP)+低功耗单片机(Mixed Signal Processor 430, MSP430)为架构形式,很好地解决了高频宽带ADCP 高采样率、高数据处理能力及低功耗的应用需求,在保证数据处理速度的基础上实现了相位的严格正交,且通过参数化配置实现了多频段的通用性设计。现场可编程逻辑门阵列(FPGA)因其丰富的内部可编程逻辑资源、高度的并行性、低功耗、高集成度等特点,广泛应用在高速数字信号处理中。数字信号处理器(DSP)编程灵活、处理能力强且可扩展性强,在复杂算法处理中极具优势。低功耗单片机(MSP430)接口丰富,功耗极低,非常适合用于系统控制中。本设计充分利用FPGA、DSP 和MSP430 在数字信号处理中的优势,对系统流程进行软硬件划分,采用软硬件协同设计方式完成了整个通用型高频宽带ADCP信号处理系统的设计与实现。

1 原理简介

宽带声学多普勒流速剖面仪的基本工作原理是利用声电换能器向海底和海水介质发射由伪随机相位编码调制的声脉冲信号,并接收从海底和海水中各散射层声波散射体反射的回波信号,通过分析波束回波信号的多普勒频移信息,从而得到海底和海水相对仪器的运动速度、方向及仪器距离海底和海水的剖面深度等信息。

多普勒测频技术是宽带ADCP 的关键技术之一,基于谱矩理论的复相关算法可以在低信噪比情况下快速精准地进行测频,具有运算量小、精度高等优点,在工程应用中得到了广泛使用[2]。本文对设计中使用的编码信号和复相关测频基本原理进行简单介绍。

1.1 编码信号

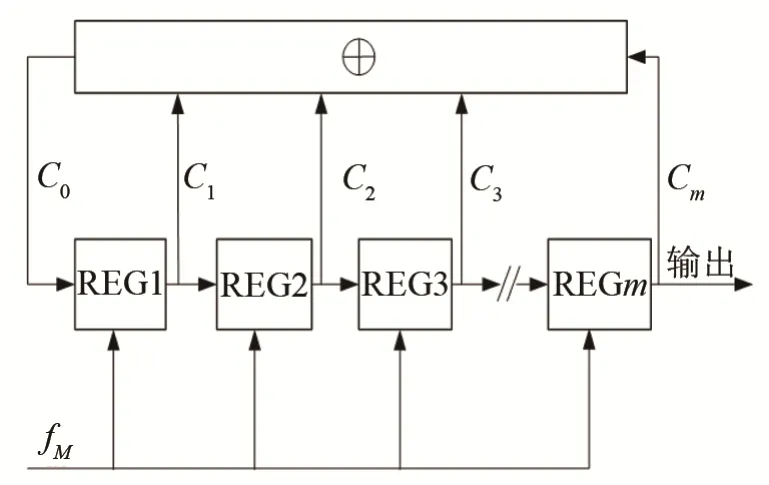

宽带ADCP中使用伪随机编码对发射脉冲进行相位调制,M 序列编码信号是一种伪随机二相编码调相信号,具有优良的自相关特性,易于产生和复制。编码调相信号可以用复数表示为

其中,f0为发射脉冲中心频率;a(t )为编码信号的复包络:

式中:T 为编码信号长度;rect 为构造矩形函数;∆t为码元宽度;N 为码长,则编码信号的长度T = N ×∆t。φk为调相角度,当φk取值为0 或者π 时,信号即为二相调制码。设φk= akπ,ak为二进制序列,也就是二相调制码的编码形式。

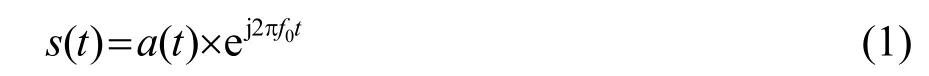

M 序列是伪随机序列,它具有与随机噪声相似的尖锐相关函数特性,可以将C0通过m 个移位寄存器相级联的方式实现[3]。图1 为M 序列码生成器的模型,移位寄存器的抽头系数和Cm恒为1,C1~ Cm−1可以为0 或1。当给定时钟频率 fM=1 /∆t时,系统输出码元宽度为∆t,码长为 2m−1−1的编码脉冲信号。只要选择合适的C1~ Cm−1值,在输出端即可得到2m−1 位的M 序列伪随机码[4]。

图1 M 序列码生成器模型Fig.1 Model of M sequence code generator

1.2 复相关测频

由于回波信号是实信号,而复相关方法需要根据实信号得到它的复数形式[5]。已知一个实数信号,可以通过希尔伯特变换(Hilbert Transform, HT)变化来构造复数形式:

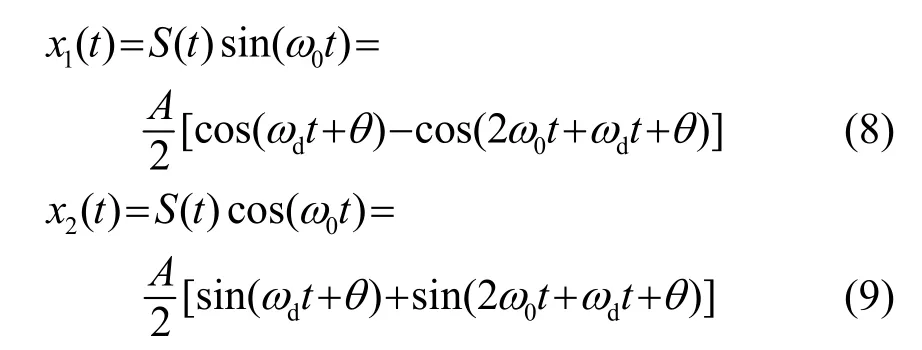

对于常用的单频余弦信号有

实际中可通过正交解调获得基带信号的复数形式。简化回波信号为

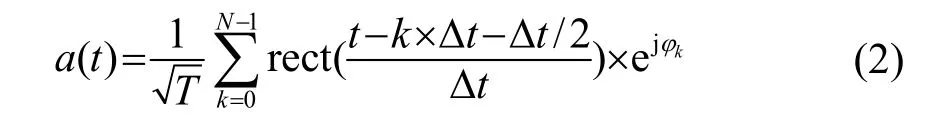

式中: ω0为中心频率;ωd为回波信号频移。用相互正交的两路信号分别与接收的回波信号S (t )做乘法运算,得到混频信号,再通过低通滤波器(LPF)滤除高频部分,得到送入复相关运算的复基带信号xR、 xI最后得到X (t )。正交解调框图如图2 所示。

图2 正交解调框图Fig.2 Block diagram of orthogonal demodulation

通过低通滤波滤除高频分量,可得到:

用于复相关运算的复观测信号X (t )为

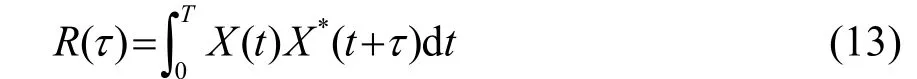

进而可求得复相关函数R (τ )为

结合式(12)和式(13)可得:

可知,复相关值仅与回波信号的多普勒频偏有关,且复相关函数的相位φ (τ )表示为

则有:

得到频偏参数后,根据多普勒频移公式完成测速工作。

2 系统设计

2.1 系统架构设计

本系统是针对通用型高频宽带ADCP 而设计,系统频率可以覆盖300、600 kHz 及1.2 MHz 等频段。为了避免模拟解调引入的相位失调、零漂等问题,本系统采用直采方式,即对回波信号先采样后做数字解调滤波处理,这就对AD 模块的采样速率、处理器的批量数据处理能力及系统功耗等方面提出较高的要求。综合考虑目前各种主流处理芯片在数字信号处理及逻辑控制中的优劣势,设计中采用FPGA+DSP+MSP430 系统架构形式来实现。

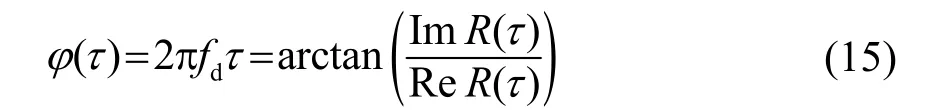

对系统流程进行软硬件划分,其架构形式如图3 所示。MSP430 模块是系统的主控单元,实现整体逻辑控制和值班电路控制,同时完成与上位机的数据交互功能(RS232 串口通信)。FPGA 模块负责完成发射/接收控制和数据流的预处理,包括高速AD 信号采集、复解调运算、低通滤波和降采样处理等操作,并将处理后的数据经高速数据通用并行端口(Universal Parallel Port, UPP)总线传输至DSP端。DSP 模块是系统的核心处理单元,对FPGA 端预处理后的数据按照上位机设定的模式进行解算,并完成数据的存储和上传(网络通信)等功能。

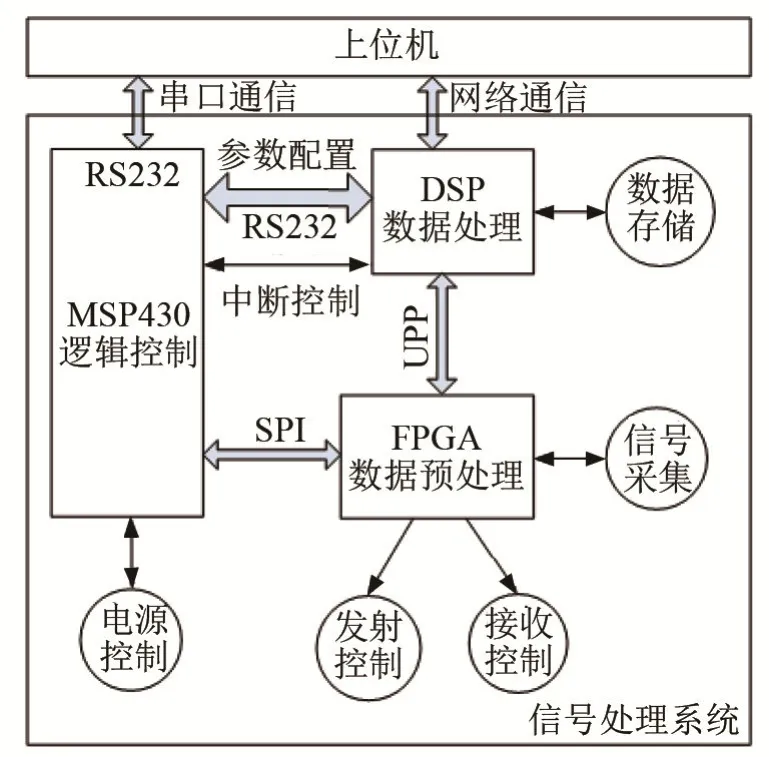

本系统是多频段通用型处理系统,对各频段的数据量分析如表1 所示。

图3 系统架构框图Fig.3 System architecture diagram

表1 多频段数据量分析Table 1 Data volume analysis for different frequency bands

单通道采样点数为Tfs,采样时长 T =D / c /2,声速取值c=1 500 m·s-1。采样频率fs与作用距离D和采样时长T 均成反比,因此在标称作用距离情况下,各频段的数据量一致,处理时长一致,易于实现各频段的通用性设计。此外,ping 间隔(最小发射周期)取决于采样时长和处理时长两部分,因此当频率增加时可以降低ping 间隔来提高系统的工作效率和精度。

2.2 系统软件设计

本设计中,根据功能可以将软件系统划分为逻辑控制软件和数据流处理软件两大部分,其中逻辑控制软件主要由MSP430 完成,数据流处理软件在FPGA 和DSP 的协同作用下完成。本文对数据流的处理过程进行重点介绍。

2.2.1 数据预处理

数据预处理操作在FPGA 控制单元完成,主要包括发射、接收控制、高速数据采集、复解调、低通滤波和数据抽样等,其数据流向如图4 所示。

图4 预处理单元数据流向Fig.4 Data flow direction of preprocessing unit

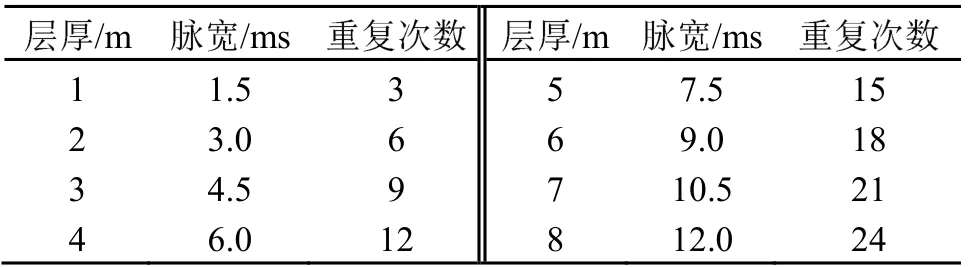

发射控制信号为两路相位相反的M 序列编码信号和一路发射包络信号。本设计中使用15 个码元的编码方式,每个码元填充10 个单频方波信号,占空比为50%,信号频率为系统频率。由于本系统可以兼容多个频段,因此在设计过程中对填充信号频率做参数化处理,可通过上位机配置信息实现不同频段的自由切换。M 序列编码信号发射脉冲长度为1 个M 序列编码信号乘以重复次数,重复次数可根据上位机设定的频段及层厚进行设计,例如,300 KHz ADCP 发射脉冲宽度如表2 所示。

表2 300 KHz ADCP 发射脉宽Table 2 Pulse width of 300KHz ADCP

接收控制信号主要是一路时间-增益控制信号,该部分功能由数-模转换(Digital to Analog, DA 转换)模块实现。本设计是在FGPA 中完成DA 转换的驱动程序并生成相应的控制曲线,输出至接收机中。

本设计中使用LTC2170-14 芯片完成AD 采样,该芯片可支持5~25 MHz 的采样率,根据系统通用型设计要求,对回波模拟信号采用4 倍采样原则,综合各个频段的采样需求,ADC 的采样率为1.2、2.4、4.8 MHz。对于采样率<5 MHz 的情况,采用过采样后抽取的方法实现,例如以9.6 MHz 进行采样,1/8 抽取得到等效采样率为1.2 MHz,1/4 抽取得到等效采样率为2.4 MHz,1/2 抽取得到等效采样率为4.8 MHz。程序设计过程中,通过对采集模块时钟频率参数化设计来实现不同采样率的自由切换。

FPGA 芯片具有丰富的内部逻辑资源,且可以实现高度的并行处理,非常适合复解调运算这种模块固化后的流水线批量操作。低通滤波功能是通过调用FIR(Finite Impulse Response, FIR)滤波器的IP(Intellectual Propert, IP)核实现,由于本设计中先完成了复解调操作,将系统中心频率已搬移至零点,因此不同频段设计中滤波器是可以通用的。降采样通过数据抽取方式来实现。

2.2.2 高速数据通道设计

本系统设计中,FPGA 获取ADC 采样数据并处理后传输至DSP 端进行后续解算,FPGA 与DSP之间通过UPP 总线实现高速数据传输。

UPP 是一种高速数据传输通道,其包含内部DMA(Direct Memory Access, DMA)控制器实现了最大化吞吐量,减少了数据传输时处理器的干预。UPP 总线接口数据位宽为16 bit,最高时钟速率可达到75 MHz。对于本系统,DSP 的UPP 接口工作于接收模式,由FPGA 提供接口时钟,当采样率为6 MHz 时,UPP 接口的时钟速率为6 MHz,完全满足所需的传输速率要求。

UPP 模块的软件设计主要包括初始化程序和中断程序两部分。初始化针对系统需求配置接收通道,其配置代码需按照下列步骤完成:

(1) 使能引脚的UPP 复用功能,包括数据引脚和控制引脚;

(2) 配置数据宽度、格式、速率等;

(3) 使能UPP 中断和外设功能;

(4) 分配数据存储空间;

(5) 配置DMA 通道描述符;

(6) 清除相应的标志位,开启接收等待状态。

UPP 中断可以定义为多种方式,I 路和Q 路的行中断、窗中断,以及溢出、出错中断等,上述中断处理均放在同一个函数,通过uPP_DMA_CHI、uPP_DMA_CHQ 获取确切的中断类型然后做相应处理。本系统设计中将UPP 设定为窗中断,当接收数据量达到一个窗的设定值时触发产生窗中断。窗中断参数配置示意图如图5 所示,图中Line 表示行信息。

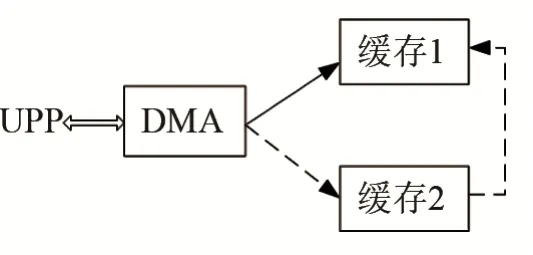

为了实现数据的连续采集处理,DSP 端在DDR2 中开辟乒乓缓存,通过DMA 方式缓存来自UPP 的数据并分批进行处理,缓存方式如图6 所示。

2.2.3 数据处理

图5 窗中断参数配置Fig.5 Parameter configuration for window interruption

图6 高速通道数据乒乓缓存Fig.6 Ping-Pang buffer of high speed data

DSP 控制单元选用C6748 芯片,其最高主频为456 MHz , 运 算 能 力 可 达 到 3 648 MHz 和2 746 MFLOPS(Million Floating-point Operations per Second,即每秒百万个浮点操作),具有并行总线UPP,可与FPGA 之间实现高速数据传输,具有DDR2、10/100 MHz 以太网、MMC/SD、UART、SPI、I2C 等丰富的外设,且该芯片工作于300 MHz时的典型功耗仅为480 mW,非常适合低功耗设计。

本系统设计中,DSP 端上电复位后,等待MSP430 中断,完成参数配置和模式选择操作,然后等待UPP 中断完成数据传输,再在设定模式下完成数据搬移、复相关运算、流速解算、传感器数据解析以及结果数据的存储或上传等操作。

本系统实现了自容式和走航式软件的一体化设计。当系统配置为走航式时,数据解算模块可以根据配置情况完成测流、测底等功能,并将处理结果实时上传至上位机中。配置为自容式时,系统根据设定时序完成一个TE(Time per Envelope)周期的测流工作,并将结果存储在SD 卡中。DSP 端的处理流程如图7 所示。

3 试验结果及分析

本系统已经成功应用在SLC300-1 型ADCP 设备中。为了对系统的性能进行验证,在某湖上进行了对地测速精度的考核试验。

图7 DSP 数据处理流程图Fig.7 Flow chart of DSP data processing

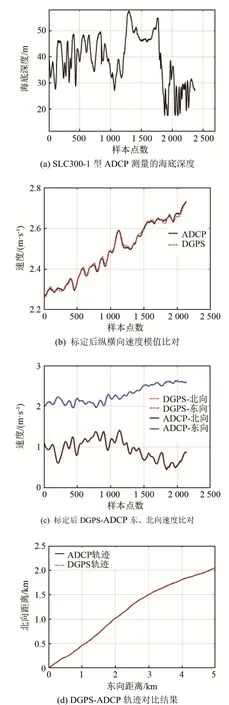

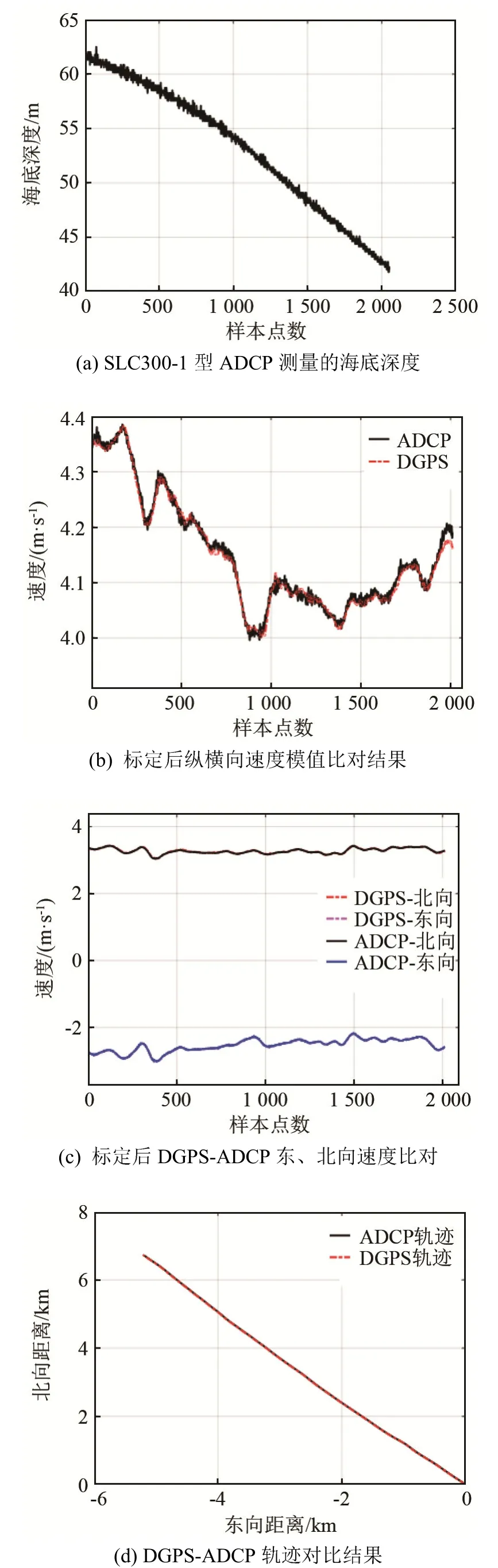

在对地测速精度考核试验中,试验船分别以预定的4 kn 和8 kn(实际航行速度以DGPS 为准)的测速点航行,每个航速下航行时间不小于1 h,试验过程中同步录取ADCP 的底跟踪数据、罗经航向数据和DGPS 数据进行比对分析。

图8~9 为两个速度点下的考核航次数据比对结果,表3 所列的数值为数据处理后得到的数据质量分析结果。

表3 中,DGPS 速度为外置GPS 的合成速度,试验中以该速度作为流速比对标准;ADCP 速度为试验设备的合成速度;相关系数r 用来表征ADCP速度与DGPS 速度的相关性,该系数越接近1 说明设备的测速性能越优;置信概率用来表征有效样本数据占总样本数的百分比,其中有效样本数据的统计依据海洋行业标准HY/T 102-2007《声学多普勒流速剖面仪检测方法》[6]中的数据处理方式进行;检测数据组数是指参与比对处理的样本总数,一般情况下取10~20 个原始流速数据做平均得到一个比对样本,试验要求样本总数不少于100 组。

图8 对地测速性能比对测量图(航速约4 kn)Fig.8 Comparisons of velocity measurement charts in bottom mode (Speed is about 4 kn)

图9 对地测速性能比对测量图(航速约8 kn)Fig.9 Comparisons of velocity measurement charts in bottom mode (Speed is about 8 kn)

由表3 的底跟踪对地测速精度检验试验记录表可知,两个受检速度点下的测速性能考核均满足技术指标(≤0.5%V,其中V 为滑动平均速度)规定的要求。

表3 测速精度检验试验记录表Table 3 Test record table for velocity accuracy inspection

SLC300-1 型ADCP 的试验结果表明,采用高频宽带编码技术的多普勒测速精度优于0.5% V,且由于宽带编码系统相对于传统的窄带系统可以获得更优的测速零偏,系统的测速稳定性得到了技术保障。

4 结 论

本文介绍了一种基于FPGA+DSP+MSP430 架构平台的高频宽带ADCP信号处理系统的设计和实现过程,采用数字解调方式提高了系统测速精度,并成功应用于SLC300-1 型ADCP 设备中。经试验验证,系统测速精度高,性能稳定可靠。此外,系统还实现了多频段自容式和走航式的一体化设计,通用性强,有助于缩短新产品开发周期,降低开发成本,对于其他高频海洋设备的研制也具有一定的参考价值。