基于FPGA的高分辨率数字脉冲信号发生器的设计与实现

2020-03-23施赛烽郑子贤徐南阳

田 宇, 施赛烽, 郑子贤, 徐南阳

(合肥工业大学 电子科学与应用物理学院,安徽 合肥 230601)

0 引 言

在现代量子物理实验中,需要研究一些演化过程非常快的物理现象。为此人们对研究设备时间分辨率的要求越来越高,同时也要求这些设备也必须在很小的时间尺度内保持可控,即需要高分辨率的脉冲信号来控制这些设备。比如在量子控制实验[1-2]中用脉冲信号控制声光调制器(acousto-optical modulators,AOM)来控制激光的通断,以及控制微波开关来调节发送微波脉冲的时间长度,进而调控量子自旋状态等。

传统的脉冲信号发生器多是由专用集成电路(application specific integrated circuits,ASIC)芯片设计制造的,这种方式虽然能够获得较高的工作频率,但成本非常高昂,且由于芯片上的逻辑设计已经固定使得内部逻辑功能无法进行更改,进而无法灵活地根据需求来修改设计;再者就通道数固定,不利于实验系统间的集成[3-4]。本文拟采用现场可编程门阵列(field-programmable gate array,FPGA)芯片作为核心芯片。FPGA作为可编程逻辑门阵列,其独特的内部硬件结构使其逻辑设计可以反复更改,较好的扩展性使其能够极大地降低设计成本,且FPGA具有很好的并行运算能力使其在多通道方面具有独特的优势。随着集成电路的规模越来越大,对于存储容量需求也日益增高。而同步动态随机存储器(synchronous dynamic random access memory,SDRAM)芯片具有容量大、成本低以及速度快等特点。因此,本文拟采用FPGA结合SDRAM芯片实现多通道脉冲发生的方案,该方案能提高设计的灵活性、提升存储容量、降低设计的成本与周期。

1 系统结构

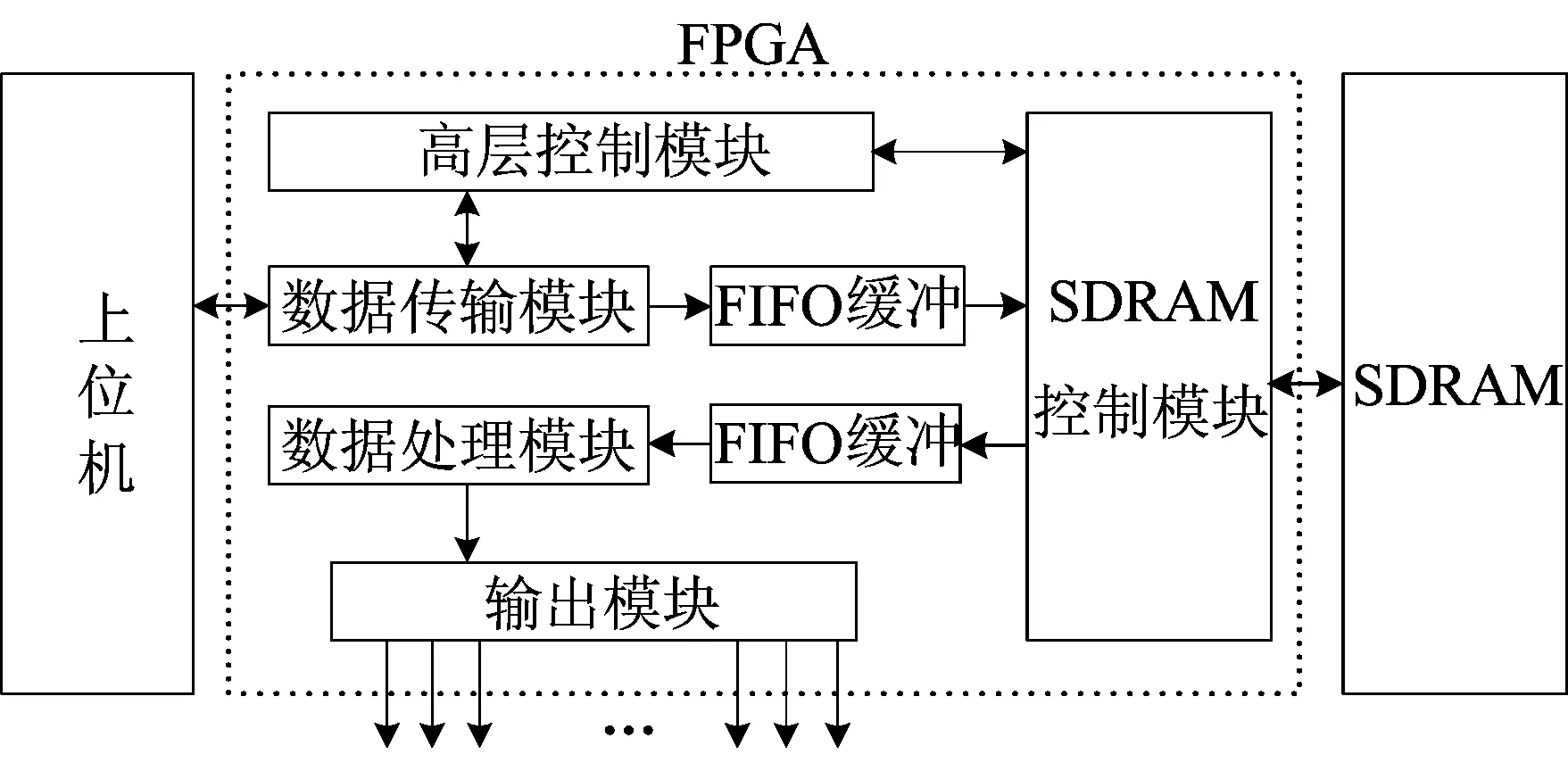

数字脉冲发生器的系统结构如图1所示,该系统主要由3个部分组成:① 上位机系统,即软件部分,采用python语言[5]编程,主要实现数字脉冲序列的编码以及向FPGA发送指令并接收反馈信息;② FPGA的数字逻辑,主要包括数据传输模块、FIFO[6]缓冲模块、SDRAM控制模块、数据处理模块以及控制模块;③ SDRAM芯片,用来存储上位机发来的脉冲序列数据。

图1 数字脉冲发生器的系统结构框图

1.1 软件设计

采用直接波形产生方式[7]生成脉冲信号,即将所需数字脉冲以时间片的形式进行切片,每一个时间片所对应值代表脉冲在该时间段是高电平还是低电平,其时间长度即为最小时间分辨率。该种方式直接以时间顺序描写脉冲信号生成脉冲数据,能够直观地表现脉冲的状态,但会产生大量需要储存的数据,使得最终输出脉冲信号的时间长度完全受限于存储空间的大小。本设计在直接波形的基础上,对这些二进制数进行编码,过滤掉大量的冗余信息,从而降低通信流量,减小了硬件上的存储资源,使脉冲信号的最大持续时间得到加长。

编码后的每条脉冲数据为128 bit,其数据格式如图2所示,由图2可以看出该数据结构主要有3个部分:① stop 最高位为标识位,当其为1时,表示这一组脉冲数据传输结束;② count 剩下的中间31位的值为该条脉冲数据运行的次数;③ sequence 低96位为24个通道的脉冲序列,每个通道占4位。之后将这些数据发送到FPGA,同时向FPGA发送控制指令,控制FPGA内部逻辑的运行状态以及设定该脉冲信号的循环指令LOOP。

1.2 硬件设计

硬件部分主要芯片为FPGA和SDRAM芯片,其中,FPGA为XILINX公司生产的Spartan-3E系列的XC3S1200E-4FTG256芯片;SDRAM为Micron公司生产的MT48LC16M16芯片,其最大存储空间为256 MB。

FPGA的数字逻辑模块结构如图1中虚线框内所示。由此可知,FPGA的数字逻辑模块包括数据传输模块、FIFO缓冲模块、SDRAM控制模块、数据处理模块、输出模块以及高层控制模块,其中,SDRAM控制模块、数据处理模块和输出模块为主要功能模块。数据传输模块用以实现对上位机的数据发送和接收,高层控制模块主要根据上位机发送的控制指令来控制SDRAM的读写状态以及将SDRAM的当前状态通过数据传输模块反馈给上位机,FIFO缓冲模块主要实现对传输数据的缓冲、对数据传输位宽的转换和不同时钟域的分割。

1.2.1 SDRAM控制模块

为节省FPGA上的RAM资源,本设计在板上添加了一片SDRAM芯片来存储上位机发来的脉冲数据,对SDRAM芯片的控制由FPGA的SDRAM控制模块实现。SDRAM控制器模块的状态机如图3所示,图3中tRP为内存行地址控制器预充电时间(row precharge timing);tRFC为SDRAM行刷新周期时间(row refresh cycle timing);tMRD为加载模式寄存器命令与行有效或刷新命令之间的延迟(MRS to MRS command timing)。

根据SDRAM芯片的工作原理,该模块对SDRAM发送多种命令:① 预充电命令(percharge);② 自动刷新命令(auto refresh);③ 模式寄存器设置命令(MSR);④ 空操作命令(NOP);⑤ 自我刷新命令(self refresh);⑥ 行激活命令(active);⑦ 读命令(read);⑧ 写命令(write)[8]。

图3 SDRAM控制模块的状态机

1.2.2 数据处理模块和输出模块

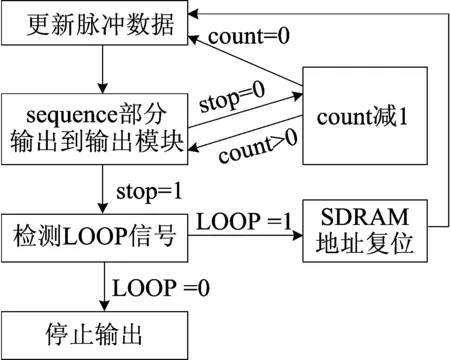

FPGA接收并储存于SDRAM中的数据是经过软件部分编码处理的,因此要正确输出所需的脉冲信号,必须对脉冲数据根据编码规则进行译码。译码的流程示意图如图4所示。在单次发送脉冲过程中,为保证输出脉冲的连续性,sequence脉冲序列部分的数据一直向输出模块中发送。脉冲数据的更新由count部分和stop部分共同控制,count的值为当前脉冲数据输出的次数,count为0时,更新脉冲数据;当stop为1时,停止脉冲数据更新,单次脉冲发送结束,此时检测LOOP信号以判断是否循环发送脉冲。若LOOP为0,则停止脉冲输出;否则将SDRAM的读地址复位,开始下一次的脉冲发送过程。

Sequence部分的数据为96位,包含24个通道的脉冲序列,每个通道包含4位数据。在输出模块中,对每个通道并行输入的4位数据进行并转串处理,同时利用时钟上升沿和下降沿触发使脉冲序列最终输出时的比特率是最大时钟频率的2倍。最终输出24个通道的脉冲信号,输出的电平标准设为LVCOMS25。

图4 译码过程的流程

2 测试结果

本文使用普源的DS4054示波器进行测试,其带宽为500 MHz,采样率为4 GSa/s。系统产生的脉冲信号如图5所示。脉冲信号发生器的3个通道同时产生3个脉冲,它们设定的脉冲宽度分别为2、4、6 ns。由图5可以看出,其实际输出信号和设定值基本吻合,这表明:可以产生最小2 ns脉宽的脉冲信号;最小分辨率为2 ns;上升沿时间和下降沿时间小于 1 ns(上升沿和下降沿时间均为幅值的10%和90%之间的时间);在多通道同时输出时,可以正常工作并输出稳定。

图5 脉冲信号的测试结果

3 结 论

本文设计并实现了基于FPGA的多通道数字脉冲发生器。该系统以FPGA芯片为核心,SDRAM作为扩展存储器,实现了脉冲信号数据编码、传输、译码以及最终产生脉冲信号。整个系统结构简单,硬件主体仅需FPGA+SDRAM芯片,成本较低;采用上位机对FPGA的工作状态进行控制,同时实时接收FPGA反馈回来的状态,不仅极大地方便了对该系统的使用,而且更有利于和其他系统进行集成。对系统产生的脉冲信号的测试结果表明,脉冲发生器的最小分辨率达到了2 ns,而且多通道同时输出时脉冲信号稳定。