二氧化硅掺杂钛酸锶钡陶瓷的介电性能与电卡效应

2020-03-21欧阳林虹王文倩王文伟吴洁茹

欧阳林虹,王文倩,王文伟,吴洁茹,薛 昊

(厦门大学材料学院,福建厦门361005)

随着氟利昂及氟氯烃化合物等制冷剂的大量使用,臭氧层被严重破坏,严重威胁着人类健康。 电卡制冷以其无氟环保、体积可控、制冷效率高等优点成为当前新型制冷技术的一个重要分支,有望代替传统的制冷剂。 电卡效应(electrocaloric effect)是指在极性晶体中,净极化值随着外加电场的增加而增大,通过降低体系的熵而使材料的绝热温度升高,且该效应是可逆的。 具有电卡效应的材料主要包括聚合物、无机铁电反铁电单晶、陶瓷等。 其中聚合物薄膜需在高电场下发生等温熵变 (ΔS), 电卡参数(ΔT/ΔE)远不如陶瓷[1];一级相变单晶BaTiO3具有非常高的电卡效率[2],但是因其居里温度高达130 ℃使其实际应用困难。相较于聚合物和单晶材料,陶瓷的电卡效应在铁电相变附近表现优异。 研究表明,(Pb,Nb)(Zr,Sn,Ti)O3陶瓷在160 ℃附近具有2.6 ℃的温变值[3-4]。大多数的铅系陶瓷在较高的温度下才具有显著的电卡温变,且含铅背离了环保的初衷,很难得到实际应用。近年来,Ba1-xSrxTiO3(BST)陶瓷由于具有居里温度可调、介电常数高、介电损耗小等优点成为无铅电卡材料的重点研究对象[5]。 目前针对BST 体系的研究工作集中在降低居里温度(TC)、提高电卡绝热温变(ΔT)等方面。Kumar 等[6]通过掺杂10%ZrO2(质量分数)使得Ba0.9Sr0.1TiO3陶瓷的TC降至60 ℃。 Xu 等[7]合成了MnO 和Y2O3共掺杂的BST 陶瓷, 该陶瓷在室温、电场为2.39×10-7℃·m/V 条件下ΔT为2.63 ℃。Liu 等[8]通过放电等离子体烧结法制备了MnO 掺杂的BST 陶瓷,并将ΔT从0.83 ℃提高到3.08 ℃。 因此,通过氧化物掺杂可以提高BST 陶瓷的电卡温变和降低居里温度。

笔者选取廉价、原料丰富、热性能稳定且介电损耗较小的SiO2为添加剂来制备SiO2掺杂无铅Ba0.65Sr0.35TiO3(BST)陶瓷,系统研究了陶瓷的介电性能与电卡效应,以期得到介电性能及室温下电卡效应优良的BST 陶瓷。

1 实验部分

1.1 实验原料

BaCO3、SrCO3、TiO2、SiO2、聚乙烯醇(PVA),均为分析纯。

1.2 SiO2 掺杂BST 陶瓷的制备

采用传统固相反应法制备SiO2掺杂Ba0.65Sr0.35TiO3陶瓷。 按照化学计量比准确称量BaCO3、SrCO3、TiO2粉末,球磨12 h,干燥后在1 080 ℃预烧3 h 得到Ba0.65Sr0.35TiO3(BST)粉体。 加入SiO2粉体(质量分数分别为0%、1%、2%、3%、5%),球磨6 h,烘干后过筛,加入质量分数为6%的PVA 溶液造粒,在50 MPa下压制成直径为10 mm、厚度为2 mm 的坯片。 将坯片在600 ℃排胶3 h,然后以5 ℃/min 升温到1 360 ℃并保温3 h,得到BST+x%SiO2(x=0、1、2、3、5)样品。烧结后的样品通过精密减薄器减薄至0.5 mm 左右,并于1 200 ℃退火处理2 h 以消除减薄过程中产生的应力对后续样品性能测试的影响。 最终在陶瓷样品表面镀上厚膜银电极,进行介电性能和铁电性能测试。

1.3 表征方法

采用BS210S 型分析天平和阿基米德原理测量样品的密度。 采用TM3000 型扫描电镜(SEM)进行样品的表面形貌分析。 采用Bruker D8-A25 型X射线衍射(XRD)仪进行样品的物相分析。 采用HP4284A 型LCP 测试仪测试样品在-20~120 ℃及0.02~1 000 kHz 的电容(C)和介电损耗(tan δ),升温速率为1 ℃/min。 其中介电常数(ε)计算公式:

式中:C为电容量,pF;d为样品厚度,mm;D为电极直径,mm。 采用Netzsch DSC204 Cell 型热分析系统测量样品在0~130 ℃的比热容, 以氮气作为保护气体,升温速率为10 ℃/min。 采用TD-88A 型铁电性能综合测试仪测量样品在20~90 ℃的铁电性能,每隔10 ℃测量各样品的电滞回线,测试频率均为10 Hz,并采集其极化值。 为保证样品内部的温度符合设定值,在各温度下保温50 min,并使用AM330型红外线测温仪确定,精度为±1 ℃。

1.4 电卡效应的计算

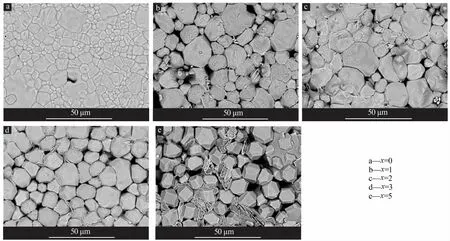

采用间接法计算电卡效应, 选用电卡绝热温变(ΔT)和ΔT/ΔE两个参数来衡量电卡效应,其中参数ΔT/ΔE可衡量不同厚度材料的电卡效应。 根据麦克斯韦方程:

得到ΔT计算式:式中:ρ 为样品密度;E1和E2分别为低电场强度和高电场强度;T为温度;CE为材料的比热容;P为极化值。将测量得到的极化值P对温度T做图,将P-T曲线进行拟合、微分,再横向对每个温度下不同电场的∂P/∂T积分得到ΔT。

2 结果与讨论

2.1 物相及微观形貌分析

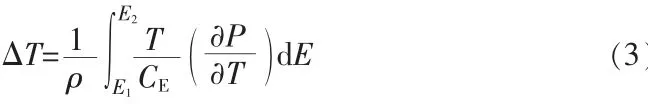

BST+x%SiO2陶瓷XRD 谱图见图1。 由图1 看出, 所有SiO2掺杂样品和纯BST 样品均为单一相,各峰位与BST 标准衍射峰(PDF#44-0093)位置一致, 说明在1 360 ℃下粉体充分反应, 结晶性能良好,SiO2的加入并未改变BST 陶瓷的晶型结构。

图1 BST+x%SiO2 陶瓷XRD 谱图

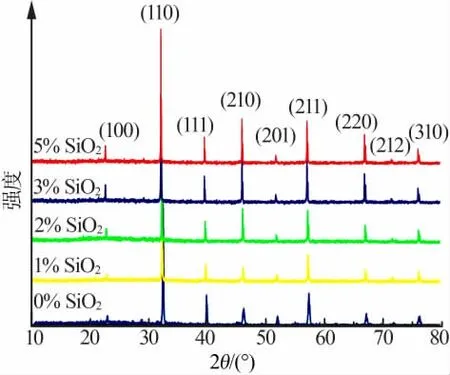

图2 是BST+x%SiO2陶瓷SEM 照片。 从图2 看到,未掺杂SiO2的BST 陶瓷主要由较小尺寸的晶粒和异常长大的晶粒组成,晶粒均匀性较差,同时晶粒表面存在气孔; 掺杂少量SiO2有助于晶粒的生长,如图2b、c, 其晶粒尺寸大于纯相BST 中的晶粒,这是因为掺杂的SiO2作为优良的烧结助剂[9],能够促进晶粒生长得较为致密,使晶粒表面没有气孔,并且提升晶粒的均匀度; 当SiO2掺杂量继续增加时,陶瓷晶粒尺寸又逐渐减小,见图2d、e,这是由于过多SiO2的加入阻碍了烧结颗粒的直接接触, 延缓了固相反应中的传质过程,从而限制了BST 晶粒的长大。

图2 BST+x%SiO2 陶瓷SEM 照片

2.2 介电性能分析

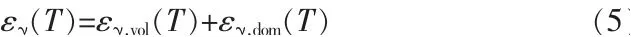

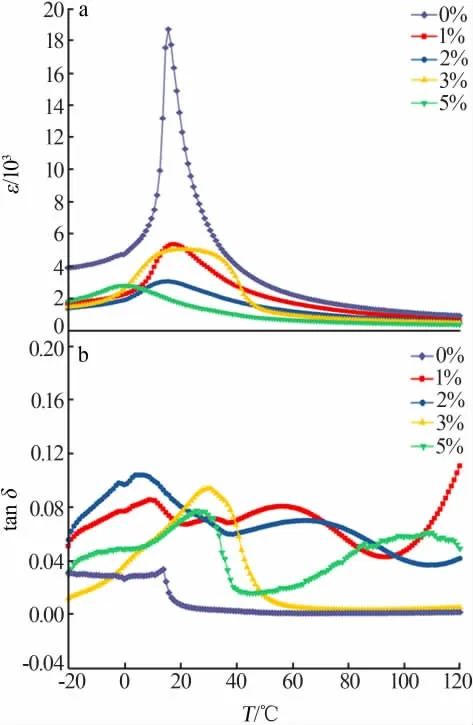

图3 为BST+x%SiO2陶瓷在不同温度下的介电常数(ε)和介电损耗(tan δ)。由图3a 发现,所有样品的介电峰都只有一个, 该峰对应样品从铁电相到顺电相的转变,并且随着SiO2掺杂量增大,介电峰整体上也变得较为弥散。当SiO2掺杂量不超过3%时,其居里温度为20 ℃左右, 当SiO2掺杂量为5%时,其居里温度降至0 ℃, 这是由于体系中不同微区的居里温度不同, 实验测得的居里温度是各个微观区域居里温度的总和,当SiO2掺杂量达到5%时,各微区的居里温度降低, 最终使得材料的居里温度降至0 ℃。 另一方面,掺杂3%SiO2的样品介电峰最弥散,这可能是由于在BST 陶瓷体系中,随着SiO2掺杂量增加,形成的相变微区尺寸减小,使得顺电-铁电相的弥散逐渐增加,当SiO2掺杂量超过3%时,相变微区的尺寸增大,这就使得体系弥散特性降低[10],因此BST+3%SiO2样品具有最显著的弥散特性。 与此同时,随着SiO2掺杂量增加,材料的介电常数呈现单调递减的趋势,这是由于SiO2是玻璃相的低介电材料,根据复合材料介电常数的计算式(式4)[11]可以看出, 随着SiO2掺杂量增大,SiO2掺杂BST 陶瓷的介电常数将随之减小。式中:εi为第i相的介电常数;φi为第i相的体积分数。 另一方面,晶粒尺寸也会影响材料的介电常数。BST 陶瓷的介电常数主要由单晶和电场中铁电畴壁两部分组成,见式(5)[12]:

式 中:εγ,vol和εγ,dom分 别 表 示 温 度T下 单 晶 介 电 常数和铁电畴壁介电常数。 在升温过程中,BST 陶瓷从四方相转变为立方相, 同时伴随着应力的产生。为满足能量最低条件,材料中会形成90°铁电畴以释放应力[13]。 随着晶粒的尺寸减小,四方相比例下降,单位体积畴壁随之下降,从而使介电常数也随之降低。 虽然纯相BST 陶瓷晶粒小于掺杂5%SiO2的样品,但其介电常数却高于后者,表明SiO2对样品介电性能的降低起主要作用。 另外,掺杂3%SiO2的陶瓷样品在居里温度处的介电常数高于添加2%SiO2样品的介电常数,这是由于在相变点处陶瓷中的Ba2+在BST 晶格中的扩散得到提升而取代了部分Sr2+的位置,从而造成了介电常数的异常增加[14]。

图3 BST+x%SiO2 陶瓷在不同温度下的介电常数(a)及介电损耗(b)

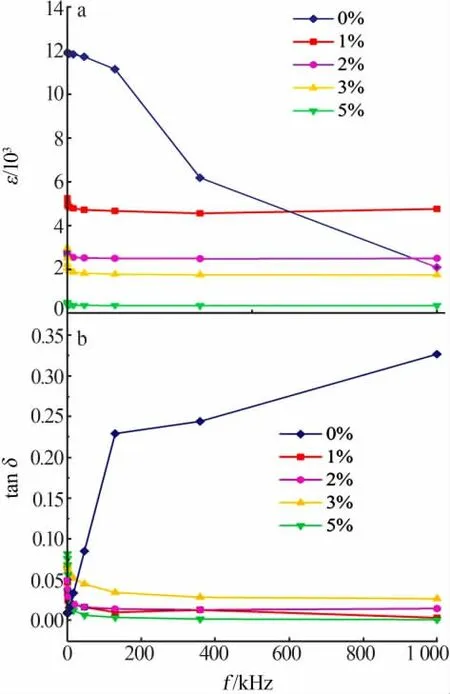

图4 为不同频率下BST+x%SiO2陶瓷的介电常数及介电损耗。 由图4 可知,纯BST 陶瓷在高频区发生介电常数的突降和介电损耗的跳跃式增加,介电损耗远远大于SiO2掺杂的样品,而SiO2掺杂的样品在测试频率范围内其介电常数、 介电损耗均平稳降低。 由图4a 看出,介电常数随SiO2掺杂量的增加而逐渐减小,主要是由于随着频率的增加,BST 陶瓷内部的电子位移和离子位移逐渐减弱, 材料内部极化强度降低所致。 由图4b 看出,SiO2掺杂的BST 陶瓷的介电损耗均低于纯BST 陶瓷;随着SiO2掺杂量增大,介电损耗呈现先增加后减小的趋势,当SiO2掺杂量超过3%以后介电损耗开始下降,并且各样品的介电损耗均低于0.03,这比纯BST 陶瓷的介电损耗小得多。 与此同时,随着SiO2掺杂量增加,介电常数、介电损耗平稳变化的趋势依然保持,与庄后荣等[15]制备的BST 陶瓷相比,本研究制备的SiO2掺杂BST 陶瓷介电常数的频率稳定性有了明显提高。

图4 不同频率下BST+x%SiO2 陶瓷的介电常数(a)及介电损耗(b)

2.3 电卡效应分析

2.3.1 样品的极化值

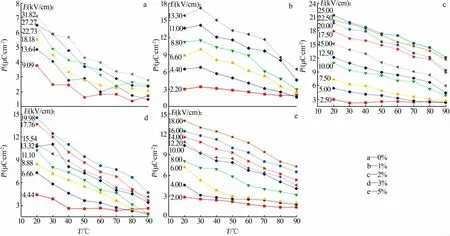

极化值的突变与陶瓷电卡效应有关, 理论上讲突变越明显则电卡效应越显著。 各样品饱和极化值随温度和场强的变化见图5。 由于各样品的厚度和击穿场强不同,故各样品施加的最大电压有所不同。由图5 发现,同一样品在恒定温度下,极化值(P)随电场强度(E)的增加而增加,这主要是外电场越强,电畴转向与外电场方向一致性越高,即极化越彻底。在恒定电场下, 极化值随温度的升高总体上呈现降低的趋势, 这是由于热波动逐渐破坏了偶极子的有序度。 在相同电场下,掺杂了SiO2陶瓷的极化值均大于纯BST 陶瓷的极化值,这是由于SiO2掺杂的陶瓷晶粒均大于纯BST 陶瓷,晶粒越小,晶粒中的内场就会减小,使得偶极子间的长程作用减弱,同时晶粒减小带来比表面积的增大,当电场存在时,对电畴起钉扎作用而使电畴难于转向, 而大晶粒对于形成完整的畴结构非常有利,并且畴的反转易实现,故铁电性能较好[16]。 另一方面,随着SiO2掺杂量增加,在相同电场下SiO2掺杂BST 陶瓷的饱和极化值逐渐递减,这是因为SiO2是非铁电相,其掺杂量越大,材料的铁电性越弱。 各样品在不同电场下的饱和极化值偶有增加的现象, 主要是由样品中的漏电流引起的[17]。

图5 BST+x%SiO2 陶瓷在不同电场(E)作用下的饱和极化值(P)随温度的变化

2.3.2 电卡效应的计算

根据DSC 测量结果发现, 在测量电卡效应的20~90 ℃,陶瓷的比热容基本无变化,故在计算过程中将不同温度下的比热容取做常数。 各样品的比热容(CE)和密度(ρ)见表1。

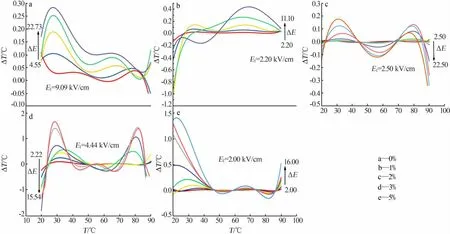

图6 BST+x%SiO2 陶瓷的ΔT 曲线

图6 为BST+x%SiO2陶瓷的温变曲线。 不同SiO2掺杂量(x=0、1、2、3)样品的最大电卡绝热温变(ΔTmax)及对应温度(T)分别为0.28 ℃(28 ℃)、0.18 ℃(30 ℃)、0.19 ℃(30 ℃)、1.6 ℃(30 ℃)。 铁电陶瓷中的一级铁电-顺电相变对电卡效应的贡献最大,因此各配方样品的ΔTmax均出现在其居里温度附近。对于BST+1%SiO2样品,其ΔTmax处对应的温度高于居里温度,这是由于采用Maxwell 计算方法在对P-T曲线进行6 次项拟合时产生了一些虚假的峰值, 而实际出现ΔTmax时的温度仍为30 ℃。BST+5%SiO2样品的居里温度为0 ℃,理论上其ΔTmax应出现在0 ℃附近, 然而本实验工作中只采集了20~90 ℃的极化值变化情况, 故无法判定BST+5%SiO2样品最终的ΔTmax。当SiO2掺杂量小于3%时,样品的电卡温变变化不大;当掺杂量为3%时,样品ΔTmax=1.6 ℃,这是由于该样品中的晶粒尺寸合适、 晶粒均匀度较好,当施加电场时,陶瓷内部的电荷移动更容易,更易获得较大的电偶极子熵变, 有助于提升电卡效应。这 一 现 象 与Yoo 等[18]和 陈 墨[19]报 道 的 研 究 结 果 相类似。

采用ΔT/ΔE可以更好地衡量电卡效应。 不同SiO2掺杂量(x=0、1、2、3)样品的ΔTmax对应的ΔE分别 为31.82、13.30、25.00、19.98 kV/cm,则ΔTmax/ΔE分 别 为 8.80 ×10-8、1.35 ×10-7、7.60 ×10-8、8.00 ×10-7℃·m/V。综合ΔT和ΔT/ΔE两个参数可知,BST+3%SiO2样品具有最优的电卡效应,并且该样品出现1 ℃以上温变的范围为25~35 ℃, 电卡效应半峰宽Tspan达到10 ℃左右, 有利于在较宽温度范围内应用。 另外,由图3a 可知,BST+3%SiO2样品的介电峰弥散性最强,材料中发生弛豫相变同样有利于提升电卡效应[20]。

3 结论

1)SiO2掺杂未改变BST 陶瓷的晶体结构, 促进了晶粒表面的致密化, 提升了晶粒尺寸的均匀度,同时提升了样品介电性能频率的稳定性。 2)随着SiO2掺杂量增加,BST 陶瓷介电常数逐渐降低,介电弥散特性增强。此外,SiO2的加入有助于降低BST 陶瓷的居里温度。3)BST+3%SiO2样品具有最优的电卡性能,获得最大电卡绝热温变(ΔTmax)的温度为30 ℃,ΔTmax和ΔTmax/ΔE分别为1.6 ℃、8.00×10-7℃·m/V。此外,SiO2掺杂BST 陶瓷的电卡效应半峰宽Tspan保持在5~10 ℃。