2.5D封装有机基板制造工艺研究

2020-03-11刘晓阳陈文录

刘晓阳 陈文录

(江苏无锡35信箱 214083)

1 引言

有机基板与TSV(硅通孔)转接板的作用是将CPU芯片的信号管脚节距逐级放大,最终将信号引出与PCB及其它器件互连,从而形成具备完整功能的模块。从材料热膨胀系数、形变量以及焊点节距对形变的容差综合考虑,结合对热机械应力的设计仿真结果,芯片凸点节距180 μm,转接板的凸点放大后信号区域节距270 μm,内核区域为360 μm,有机基板的BGA(球栅阵列)节距1.0 mm,经过逐级放大后,各个层级对材料热膨胀带来的形变缓冲容忍度大大增强,提升了封装的可靠性。与直接FCBGA(倒装球栅阵列封装)的有机基板相比,采用TSV转接板的2.5D封装整体技术复杂度提升,可靠性和集成度将大大提升,大尺寸芯片的封装能力指标也提高一个数量级。同时,布线层向转接板的转移,将有机基板的布线密度相对降低,客观上降低了有机基板的工艺难度。但是,有机基板作为高端阵列式封装的关键部件,产业界和学术界对其设计、材料、工艺的研究从未停止[1]。本文将针对在2.5 D封装中实际应用的有机基板,从工艺路线设计、材料选择、关键工艺难点控制等方面开展研究与实验,并形成小批量产品的制造能力。

2 有机基板制造工艺选择与设计[2]-[7]

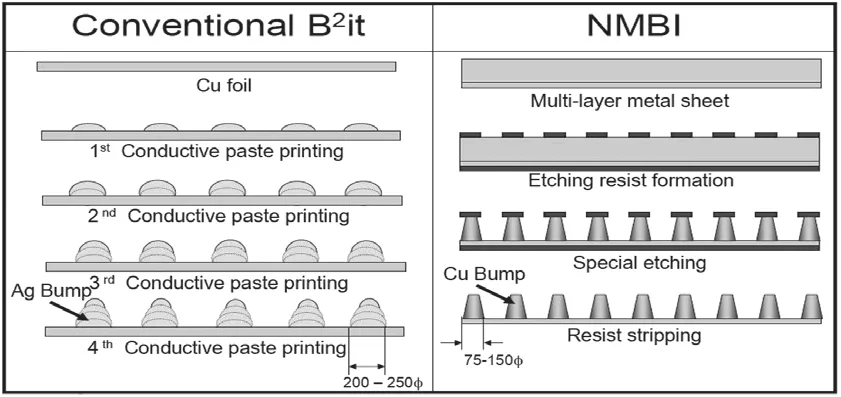

有机基板一般根据层间互连的形成方式分类,包括:ALIVH(Any Layer Interstitial Via Hole)(任意层内导通孔)、B2it(Buried Bump Interconnection Technology)(埋入凸块焊点互连技术)、NMBI(Neo Manhattan Bump Interconnection)(新曼哈顿凸点连接)、激光盲孔等,均是以层间互连采用的不同工艺来区分的,而ALIVH从广义上可以包含后几种技术。ALIVH即任意层间互连导通孔,其导通材料可以是电镀铜、导电银浆凸点、激光盲孔镀铜、铜凸点等,典型的B2it和NMBI流程对比(如图1)。

图1 B2it和NMBI工艺的比较示意图

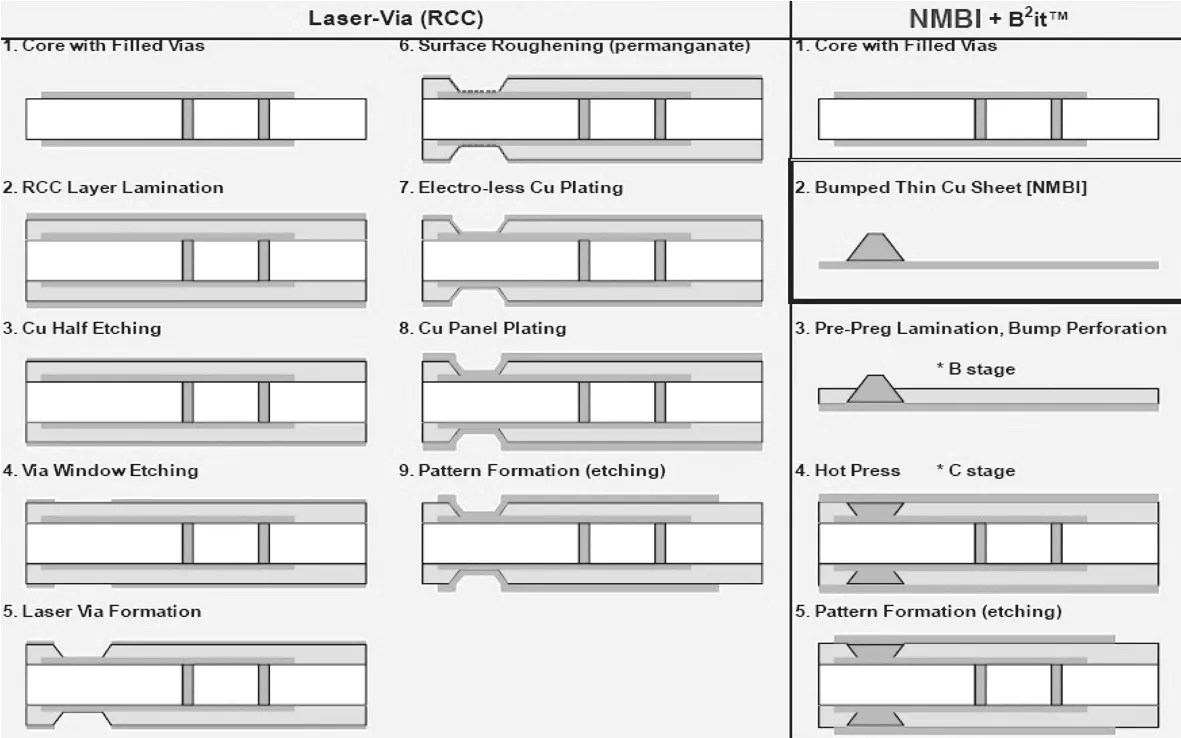

图1中B2it工艺是多次印刷导电膏并多次固化,要求每次印刷的位置精度和导电膏量的精度很高,导电膏可以使用铜浆或银浆,此工艺的缺点在于多次印刷均匀性难以控制,导电膏的直径无法进一步缩小,印刷导电膏与两面导体的结合对可靠性是很大挑战。NMBI工艺采用图形的方式,将多层金属片进行选择性刻蚀,从而形成层间互连所需要的铜凸点,再利用压合的方式将凸点与下一层金属结合,此工艺的优点是铜凸点的一致性好,进一步提高了互连密度,缺点是凸点与下一层的结合是机械压力接触式结合带来的可靠性问题,应力释放带来的变形和尺寸精度等问题。将B2it和NMBI相结合,以NMBI的铜柱代替导电膏,结合了二者的优点,与激光钻孔工艺形成的ALIVH的流程对比如图2所示。图2给出的两种ALIVH工艺的流程中,采用NMBI+B2it工艺的优点在于提高了布线密度,互连界面的可靠性问题仍然存在;采用激光盲孔工艺利用涂树脂铜箔(RCC)与芯层压合,再通过薄铜、开窗、激光钻孔、电镀、蚀刻等流程,完成互连图形的制作,多次积层重复该流程,因该流程图形采用减成法,蚀刻工艺,当铜厚10 μm以上时,线宽/间距很难达到50 μm以下。因此,该工艺会在布线密度上遇到瓶颈,同时电镀填孔的凹陷会带来可靠性隐患。

图2 激光钻孔工艺与NMBI+B2it流程示意图

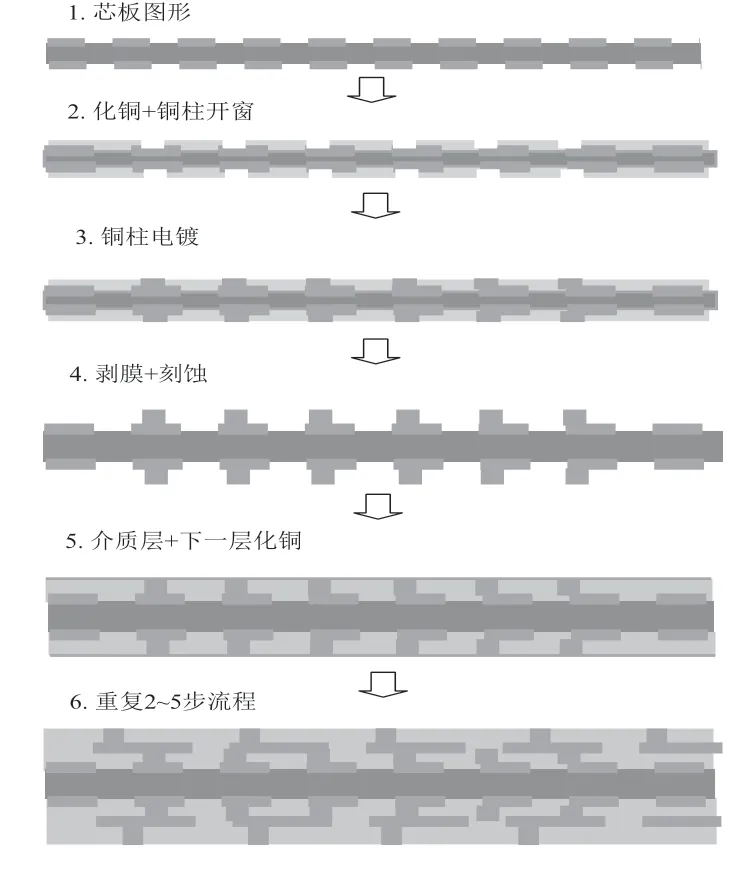

为实现超高密度互连的ALIVH技术,本文提出了半加成法(SAP)+铜凸点相结合的工艺路线,工艺流程设计(如图3)。半加成工艺可实现15 μm,甚至更加精细的线路,关键在于工艺路径设计,以及工艺过程控制。本文提出的铜凸点采用图形光成像+电镀的工艺路线,在理论上光成像可实现直径30 μm的凸点图形,最小节距可低于100 μm,大大提高布线互连密度,与SAP结合可实现很高密度的互连布线,关键在于如何保证凸点负像图形和铜电镀的一致性问题,以及一系列工艺控制问题。

图3 SAP+铜凸点工艺流程示意

针对图3中给出的工艺流程,主要关注以下几个方面:一是材料选择,包括用于基板本身的介质材料、导体材料以及过程关键物料的性能参数与选择原则;二是精细线路的SAP实现,包括:线路与介质材料的结合力、精细线路图形转移工艺、刻蚀工艺等;三是铜凸点的图形以及电镀实现技术,包括:凸点图形显影、电镀以及刻蚀工艺研究;四是介质的形成以及厚度均匀性控制工艺,包括:介质形成方法、介质厚度均匀性控制等。

3 材料选择

有机封装基板是玻纤布、有机树脂、铜导体、陶瓷填充颗粒等组成的复杂非均相材料。不同材料热膨胀系数(CTE)差异很大,硅基芯片的CTE为0.0005%/℃~0.0007%/℃(5 ppm/℃~7 ppm/℃),而有机基板基材x、y方向的CTE0.0012%/℃~0.003%/℃(12ppm/℃~30 ppm/℃)。由于基板与芯片之间热膨胀系数的差别,在焊接温度由高温向低温变化过程中会产生热残余应力(在焊点处形成剪应力),这种残余应力将会导致焊点界面疲劳断裂[2]。有研究表明,芯片CTE和基板的CTE之差应小于0.0005%/℃~0.0007%/℃(5 ppm/℃~7 ppm/℃),才能保证这类产品焊接封装的可靠性[8]。

根据有机基板的设计要求,本文实验中选择的材料包括:芯板材料为某公司的超细玻纤改性环氧板材,积层材料选用某公司的有机绝缘膜,主要成分为环氧树脂和无机颗粒填料。

4 关键工艺技术与流程设计

采用SAP研发封装基板要解决的关键工艺包括三个方面:精细线路工艺、层间互连工艺(微导通孔工艺)以及介质形成工艺。

4.1 精细线路工艺流程设计

精细线路实现是决定SAP能力最关键的技术之一。本实验设计的精细线路制造流程如下:

介质层基底材料粗化→化学沉铜种子层→感光层制作(干膜压合)→曝光→显影→图形电镀→抗蚀层剥离(剥膜)→差分刻蚀,转入层间互连工艺流程(铜柱工艺)。

4.2 层间互连工艺(微导孔工艺)设计

本实验提出有机基板采用实心铜柱(凸点)作为层间互连导体,层间互连关键在于铜柱如何制作,以及与介质层制作的先后顺序,一般传统激光钻孔工艺均采用先介质层后层间微导孔,此处采用先完成铜柱的工艺路线,设计流程如下:

精细线路电镀完成→感光抗蚀膜压合→选择性曝光→显影→铜柱电镀→剥膜→差分刻蚀,转入介质层流程。

4.3 介质层形成工艺设计

采用环氧和无机填料预成型的薄膜作为介质,既可以采用先激光钻孔再填孔互连,也可以采用先完成铜柱再制作介质层,设计的流程如下:

差分蚀刻后→层间绝缘膜压合→精密研磨→化学镀铜,转入精细线路流程,进入下一个循环。

4.4 样板制备的工艺试验过程及结果讨论

样板技术指标设计(见表1)。

表1 实验样板技术指标

4.4.1 精细线路制作

工艺试验采用的精细线路最小线宽为15 μm~20 μm。其关键点在于:导体与介质的结合力、图形及电镀精度、刻蚀精度等。本实验采用半加成工艺方法,在介质上制备铜线路图形,主要通过选择性电镀的方式制备形成精细线路,再利用精密刻蚀工艺去除种子层。首先,用化学镀铜作为种子层保证介质表面导电,然后进行后续的电镀;其次,利用感光抗蚀材料将不需要形成线路的部分保护起来,需要电镀的部分露出;第三,选择性将线路电镀到一定厚度;第四,剥除感光抗蚀材料,露出种子层;最后,利用精密刻蚀工艺,进行精细线路蚀刻。

(1)导体与介质的结合强度。

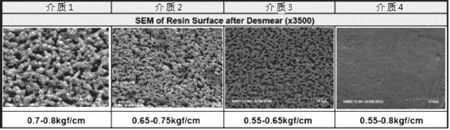

导体与介质的结合力是进行精细线路制作首要解决的问题,其关系到后续线路工艺的可实现性和可靠性。采用化学镀铜作为线路电镀的种子层,化学铜层与介质的结合强度决定了后续线路结合强度,而化学铜与介质材料的结合主要是物理结合以及较弱的范德华力,因此,决定其结合强度的主要因素是化学镀铜前的介质表面粗糙度。

介质表面粗糙度与SAP精细线路的结合强度的关系如图4所示。从图中可以看出:一方面绝缘介质膜表面形貌越粗糙,后续SAP导体铜层制作时,铜与绝缘介质膜结合力越好;另一方面,粗糙的介质膜表面,会造成导体铜层渗入介质过深,层间导体小于安全距离,导体间隙变小发生电迁移短路,后续刻蚀精度降低等问题,图5解释了粗糙度对精细线路影响示意图。

从线路精度来说,表面粗糙度越低,平整度越好,对线路精度越有利;从导体与介质结合强度考虑,表满粗糙度越高,接触面积越大,线路剥离强度越高,结合强度越高,对线路可靠性有利。因此根据精细线路的结合强度要求,采取适当的处理,使表面达到适当的粗糙度,既保证线路精度又保证适当的结合强度(如图4)。

表面粗糙度一般用Ra和Rz两个指标来表示,Ra表示平均粗糙度,Ra越大表示粗糙度越大。Ra表明了平均的粗糙度概念,但不能完全表示表面的状况,没有界定表面高低起伏的极差范围,即使Ra很小,但表面也可能很粗糙,因此,采用Rz表示表面的极差状况,表面粗糙度指标Ra和Rz越大,则表明板面粗糙度越大,线路底部与介质的接触面积越大,对物理结合而言,接触面积与结合强度是正相关的。图4下方对应的拉力测试数据证明这种相关关系,测试是采用IPC-4104标准的测试方法,研究经验表明要获得较好的粘结强度,粗糙度Ra应大于0.2 μm,Rz大于2 μm,一般Ra在0.3 μm~0.6 μm,Rz在4 μm~6 μm,会得到较好的结合力。

(2)种子层——化学镀铜。

化学镀铜所形成的种子层主要作用是在线路及铜柱电镀时作为导体层,对于精细线路而言,化学铜种子层越薄,对于精细线路的线宽精度控制越有利,但同时要考虑线路电镀时的微蚀去氧化过程损失铜厚,确保化学沉铜层的完整性。一般化铜厚度控制在3 μm~5 μm,均匀性±0.5 μm。化学铜层与树脂表面的结合力除取决于树脂表面粗糙度外,化学沉铜的晶粒大小也是重要影响因素,沉积速度不宜过快,晶粒细小致密,并能渗透到树脂粗糙的间隙内,才能保证一定的抗剥强度。另外,化学沉铜前后都要将基板烘干处理,化学沉铜前烘烤主要将树脂内的残留水汽全部烘干,防止水汽残留导致后续化铜起泡、脱落等问题;化学沉铜后烘烤一方面消除化铜层内应力,另一方面化铜层经过烘烤处理晶格重排,进一步增加化学铜与树脂的结合力。

图4 几种介质膜粗化后表面形貌图

图5 介质膜表面粗糙度对精细线路制作的影响

(3)精细线路的图形转移。

采用SAP的精细线路是通过选择性电镀方式获得。如上所述,在化学铜面选择性电镀线路,需要将不需要电镀的部分保护起来,电镀部分露出。感光抗蚀剂就是通过掩模选择性曝光发生光化学反应,再通过显影的方式,得到精细线路图形的过程。完成显影后即可进入线路电镀流程,根据线路厚度要求,采用适当的电流和电镀时间,保证电镀均匀性。若仅进行单层线路,电镀后即可将感光抗蚀干膜剥离,露出化学铜面,最后通过差分刻蚀,将非线路部分的化学铜层刻蚀掉。

实验中精细线路和铜柱的成像设备采用玻璃掩模或软菲林掩模的平行光曝光设备。选用解析能力8 μm的高解析度干膜(感光抗蚀剂),干膜厚度18 μm~20 μm,化学沉铜后微蚀前处理后贴膜,再通过真空压膜增加干膜与铜面的结合力。影响精细线路精度和良率的因素有以下几方面:化学沉铜前处理将影响感光抗蚀层与铜面的结合;曝光时间、抽真空时间、曝光能量等因素决定线路图形精度;显影过程与曝光过程是交互影响图形精度的因素。

当线宽/间距达到20 μm/20 μm或者以下时,光线的反射、折射、衍射等会使线路边缘缩小或者扩大,这种影响会随着曝光时间的加长而越发明显,恰当显影是指前处理压膜参数、曝光参数、显影参数协同作用的结果。铜面粗糙度对线宽精度和干膜结合力的影响作用相反,粗糙度大线宽精度难以达到,粗糙度小使干膜结合力差造成飞线,与前述介质和化学铜的结合原理相同,不再赘述。

实验结果显示:化学沉铜后采用H2SO4+H2O2体系进行微蚀,表面粗糙度Ra值有较明显增大,微蚀将疏松的化学铜界面刻蚀掉,但对表面高度差即Rz改变不明显。而先采用喷砂或浮石粉刷磨处理再进行微蚀处理,表面粗糙度明显改变,Rz改变主要是由于机械处理改变了表面高度差,再经过微蚀增大了Ra,可得到明显的粗化面。对于显影后的线路,表面粗糙度对线路底部和边缘的影响明显,因Rz值增大到一定程度,抗蚀剂贴膜时无法完全填充间隙,导致在显影时溶液将底部掏空的现象。过大的机械处理和较大的微蚀量造成的粗糙度过大不仅无法增大感光抗蚀干膜的结合强度,反而出现底部剥离,线路边缘粗糙,电镀时发生短路、夹膜的风险增大。因此,在进行精细线路制作时,应控制好表面粗糙度Ra和Rz(见图6)。

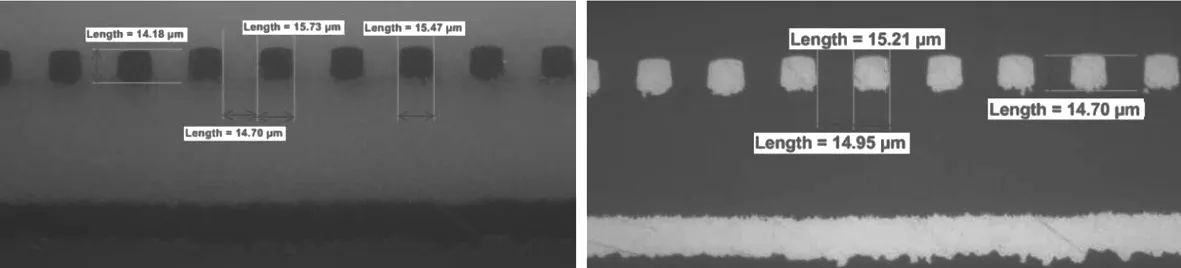

图6 前处理和线路显影后精细线路表面形貌

对于SAP工艺,选用一定厚度的高解析度感光抗蚀膜、平行光设备、恰当的表面处理、曝光参数以及显影参数共同影响形成精细线路图形的形成过程,而完成抗蚀剂的转移过程只是完成线路图形的“填充模具”,填充的过程就是线路电镀过程。完成电镀后,要剥离感光抗蚀膜,对于超细节距线路,电镀均匀性不良会有夹膜问题,造成后续刻蚀过程短路。精细线路图形电镀,镀铜厚度及均匀性14.5 μm±3 μm,图形电镀工艺上采用精密整流器控制和特殊阳极结构设计小电流长时间的电镀方式,改善精细线路镀铜的均匀性,防止小间距处电镀不均匀而出现夹膜问题;同时电镀挂板采用满挂方式,不足的加图形陪板,避免两侧电流密度集中而出现夹膜问题。图形设计上,在板边无效图形区增加了相应的辅助图形,辅助图形的分布密度按照图形区的密度设计,可以有效改善板边电流密度过大而出现夹膜的问题。

化学沉铜同时伴随析氢过程,氢可能被滞留于化铜层之中,通常晶体缺陷包括位错、孪晶、晶粒边界等;化学镀铜层的铜百分含量、密度、延展率通常均低于电镀铜,因此,快速蚀刻后化学铜面与介质层之间易形成侧蚀进一步降低线路的接触面积。侧蚀咬蚀量取决于化铜层厚度、化铜与介质结合强度、精细线路间距三个因素,由于IC封装基板的线宽/间距越来越小,通过降低化铜层厚度,并采用专用蚀刻液以降低侧蚀,进而降低超精细线路制作过程线路剥离概率。采用H2SO4+H2O2体系和表面活性添加剂的蚀刻药水,各喷头压力可调的喷淋蚀刻设备,蚀刻量控制在3 μm~5 μm,将化学铜层蚀刻掉,形成精细铜线路,完成了精细线路图形的制作。各主要流程工艺参数优化后,进行精细线路综合试验,得到理想的精细线路图形,设计线宽15 μm/15 μm,线路厚度约15 μm(如图7)。

4.4.2 微铜柱(凸点)制作

采用感光抗蚀干膜作为模板提供三维局限空间用于铜柱的电镀,对铜柱的形态及尺寸起了决定性的作用。利用负性感光抗蚀干膜通过UV曝光成像的方式,形成规则均一的圆形阵列,再通过显影的方式得到柱形空间,最后利用电镀方式将柱形空间填满形成铜柱。铜柱尺寸精度影响因素主要有以下几个方面:干膜厚度及均匀性决定铜柱高度、解析度决定铜柱直径规则性,曝光、显影、电镀和刻蚀等参数决定最终铜柱形貌。

(1)感光抗蚀干膜的选择。

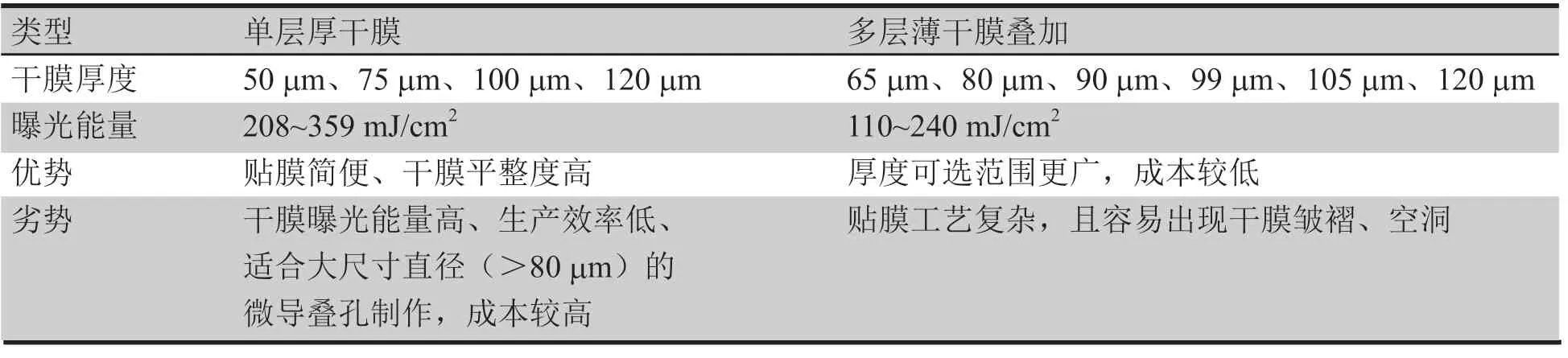

感光抗蚀干膜的选择与铜柱最终的高度是紧密相关的。初始设计干膜厚度要高于最终铜柱的高度,主要是考虑在后续的刻蚀、介质层研磨过程中会有工艺损耗,同时板面线路间隙填充也降低了干膜的实际厚度。在完成线路电镀后压合铜柱图形干膜,可以采用两种压膜方式,即单层干膜和多层干膜压合,其厚度选择和优劣势比较如表2所示。可以看出采用多层薄干膜,厚度有更加灵活的选择,可以采用不同解析度和感光度的干膜进行压合,解决了单层厚干膜解析度不能满足超细铜柱图形的解析度要求。

(2)铜柱成型

铜柱图形工艺要解决以下两方面问题:一是采用多层薄干膜叠加设计时多次压膜的界面结合问题;二是曝光成像及厚干膜的显影残留问题。对于铜柱图形工艺问题,主要解决厚干膜微开孔(65 μm~100 μm)、底部残胶和干膜类型及厚度设计问题。经多次试验测试,多层薄干膜叠加,光敏度由底层向上依次增大,采用真空压膜的方式,并且要将设计厚度流出工艺冗余;底部残胶问题与干膜厚度,曝光能量、显影时间有关,更主要是与开孔直径以及厚径比有关,干膜越厚、孔径越小,显影难度越高,需要将显影点提前到30%以内,大大增加显影时间,同时显影后的清洗采用超声清洗和压缩空气与高压水结合的方式,保证孔内冲洗彻底。

图7 精细线路截面切片(×500)

表2 感光抗蚀干膜比较

(3)铜柱电镀工艺。

实验中采用干膜开微盲孔,然后通过电镀填孔形成铜柱,电镀铜柱在线路层的焊盘上以干膜开孔后直接电镀获得微导叠孔。铜柱电镀工艺要解决以下问题:①铜柱图形盲孔表面浸润和铜面洁净问题;②铜柱底部界面结合力问题;③电镀后铜柱高度均匀性问题。采用等离子体处理干膜微盲孔内表面,其实质是解决干膜微孔内的清洁并改善改善干膜界面的表面能,从而增加溶液的浸润性。在等离子处理前必须进行80 ℃、30 min烘烤,去除板面及孔内的水汽,否则将影响等离子体处理效果。采用等离子体处理,可以有效清除铜柱底部的干膜异物残留,同时还能达到润湿干膜的效果,提高干膜的表面能,有利于后续铜柱电镀时的药水交换,获得完整的铜柱图形。等离子体润湿处理后,使干膜开窗底部干净、无异物残留,然后再进行微蚀处理,彻底去除铜柱底盘的氧化和污染,使开窗底部获得洁净的铜面,有利于铜柱电镀。

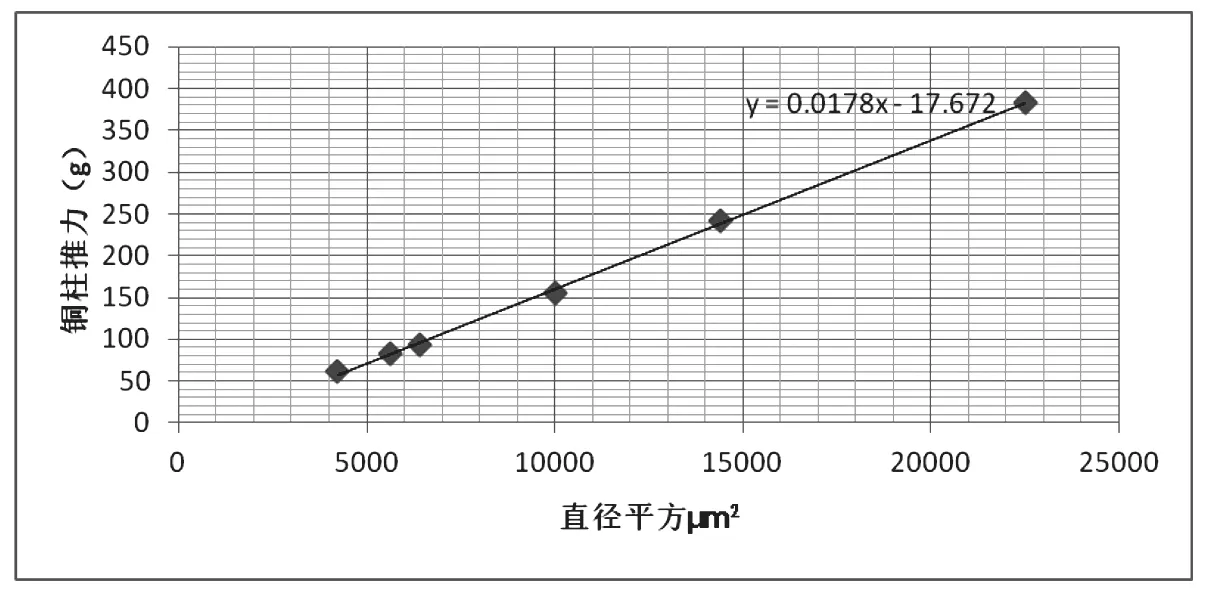

铜柱结合力与基底铜的结合力取决于电镀前的铜面洁净程度,电镀填孔过程参数控制,特别是初始电镀时的参数控制,更主要的是铜柱直径,决定了铜柱与基底铜的接触面积。优化初始电镀电流参数,采用小电流电镀主要目的在于使结晶更细密,界面接触更好,从而有效提高铜柱底部结合问题,再利用较大电流电镀,提高铜柱生长速度。采用上述措施和参数,设计不同直径的铜柱图形并用相同的电镀参数电镀,通过对铜柱推力测结果来看,铜柱结合力整体较好。对于铜柱直径与结合力的关系趋势,如图8所示,推力与铜柱直径的平方是线性关系。当铜柱直径不断缩小时,结合力将急剧减小,而铜柱与基底铜的结合力最小的临界值决定了铜柱的最小直径,也就是决定了铜柱的最高密度。当铜柱直径缩小到50 μm时,推力的估测值为25 g,经试验证实,铜柱直径50 μm左右时发生铜柱机械性剥离、缺失等缺陷概率大大增加。

图8 铜柱结合力随铜柱直径变换关系

电镀后,铜柱都会高出干膜5 μm~10 μm,高出部分由于不受干膜限制而向各个方向沉积结晶,形成俗称“蘑菇头”的铜帽(如图9)。

图9 铜柱研磨前后形貌对比图表

为保证下一层线路及堆叠孔的高度一致性,需要将“蘑菇头”削平,同时保证整个板面的共面性良好,须采用精密的机械刷磨工艺。机械研磨方式根据刷磨材料分为:砂带研磨、陶瓷刷研磨、不织布研磨三种方式。通过研究陶瓷刷轮、不织布刷轮、砂带研磨三种机械研磨方式各项特性,将三种研磨方式优化搭配研磨,先用砂带粗磨将高出的部分快速磨平,再用不织布刷磨提高表面粗糙度的均匀性,最后用陶瓷刷轮精磨起到板面整平和进一步提高表面粗糙度均匀性的作用,为下一步沉铜及图形制作提供平整均匀的表面。

(4)铜柱去膜工艺。

铜柱干膜较厚,去膜时优选有机胺体系高效去膜液,采用非接触式去膜方式,并适当降低去膜速度。当常规去膜后仍有夹膜时,可以采用等离子体处理,再水平剥膜,确保精细线路、铜柱之间无任何夹膜。去膜的关键点:①带干膜铜柱研磨的参数和去披峰微蚀量要匹配,使铜柱呈现完美的圆形;②控制去膜速度及去膜液成分的有效成分;③当去膜不净时,采用等离子体处理,在能够去除夹膜的前提下最大限度减少处理时间,避免等离子体对化铜层下树脂的攻击。

4.4.3 介质层制作

积层介质层材料一般分两大类,感光性树脂和热固性树脂材料,每种材料又有两种产品形态。一种是液态状,一种是薄膜状。液态材料形成绝缘介质层的加工方法多为涂覆方式,薄膜状材料形成绝缘介质层多为辊压或真空贴压方式。实验中采用薄膜介质作为封装基板的积层介质材料。

(1)介质厚度选择。

介质膜的最终厚度是根据电性能需求确定的,而工艺过程的厚度设计是与流程损耗密切相关的,结合工艺试验和理论计算,得出如下公式:

介质厚度=理论介厚+树脂填充厚度+树脂咬蚀余量+研磨余量;

介质膜工艺研磨余量=5 μm~15 μm;

实验中采用65 μm的标称厚度薄膜介质可满足上述要求。

(2)薄膜介质的压合工艺。

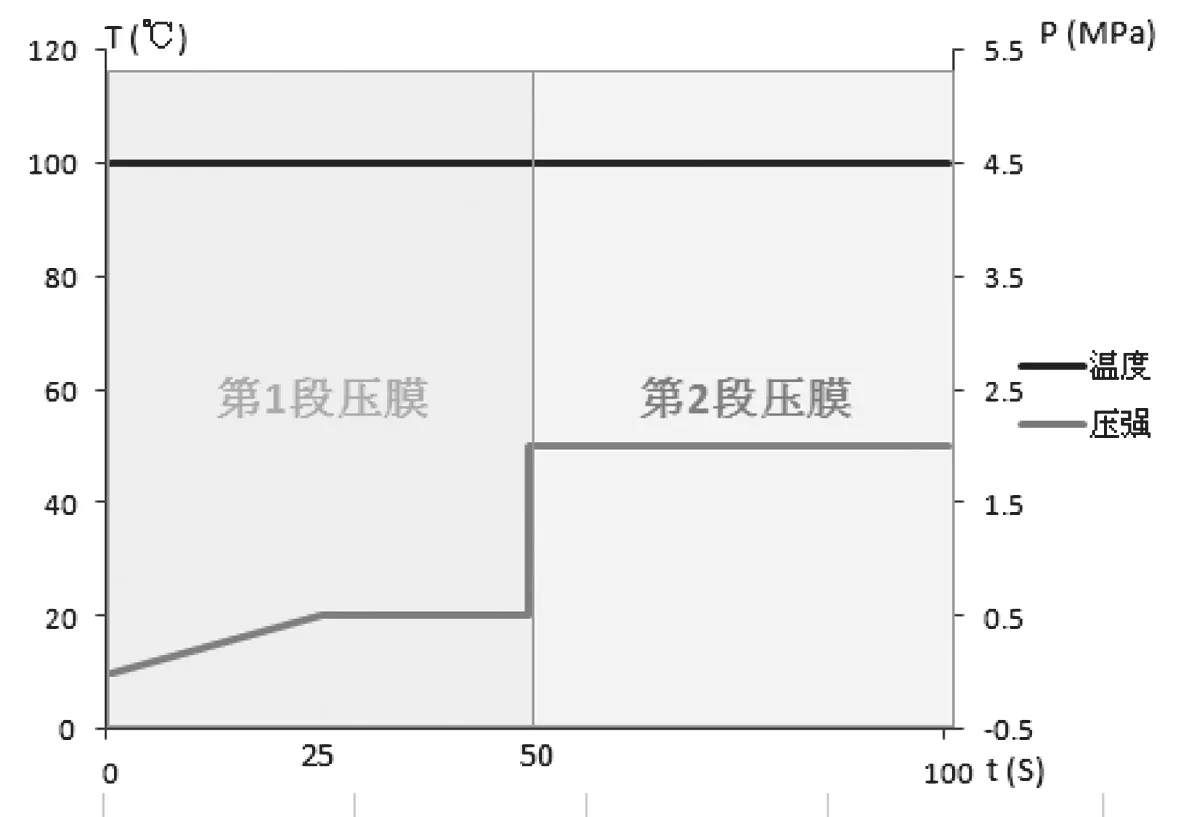

真空压介质层薄膜工艺是指采用真空压膜机将绝缘薄膜材料贴覆在完成微导叠孔制作的基板上。真空压膜机能有效防止压膜过程出现薄膜皱褶及气泡,真空压介质层薄膜温度及压力随时间变化曲线(如图10、图11)。

图10 真空压介质层薄膜温度及压力随时间变化曲线

图11 薄膜介质不同升温速率固化曲线

真空压薄膜介质层薄膜过程中,薄膜材料受热粘度降低,出于流动状态,在压力和真空作用下完全填充到微导线和铜柱之间的间隙。经过真空压膜后的薄膜材料还需要进一步加热固化,原来B阶树脂材料转化为C阶,发生完全交联反应。实验表明,薄膜加热固化过程,温度曲线的控制影响到介质层表面树脂沉积。升温速率越快,固化后薄膜表面SiO2填料越少,树脂越厚。经粗化处理后对比可以看出,升温速率快的试验组,其树脂表面更加粗糙,这种相对粗糙的树脂表面有利于增加抗剥离强度。

(3)介质层平整。

薄膜压制后,要使介质膜层厚度均匀、表面共面性良好,需要对表面进行整平。采用砂带+陶瓷辊+不织布刷辊相结合的研磨方式,通过砂带粗磨+陶瓷刷大电流粗磨、小电流精磨+不织布抛光相结合等方式,使表面共面性、平整性、粗糙度都适合下一个循环的精细线路和铜柱工艺。经过试验得出优化的平整参数如下:采用1000#砂带粗磨,功率0.2~0.6 kW,研磨1~2遍,再用4×800#陶瓷刷粗磨,电流1.0 A,研磨1~3遍,然后2×800#陶瓷0.5 A小电流精磨1遍,最后2×1000#不织布0.5 A小电流抛光一遍。最终达到控制整板面绝缘层介厚及均匀性目的,确保最终介厚与均匀性达到技术指标要求(如图12)。

图12 薄膜研磨后露出平整的铜柱情况

(4)样板试制。

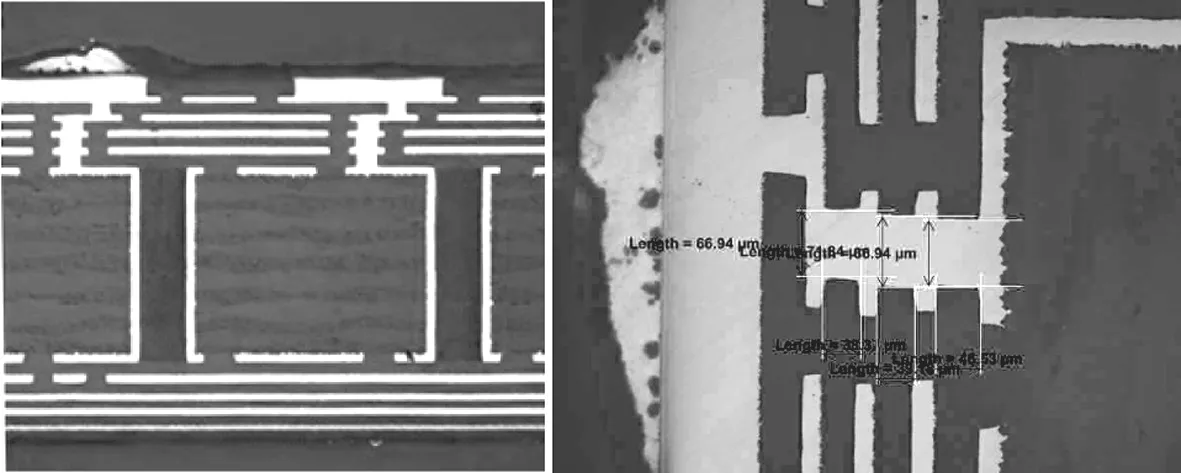

经过各分工序的实验与研究试制,完成了有机基板的综合试制,样板金相截面如图13所示。从图中可以看出,样板经过5次积层的任意层互连,层间对准度±8 μm,介质平均厚度40 μm±5 μm范围内,经过电测,其互连性能完全符合设计要求。

图13 逐层对位、5次积层有机封装基板金相图

5 小结

针对2.5 D封装用有机基板的技术发展现状,以一款实用高性能CPU的2.5 D封装有机基板为研究对象,本文对实现有机基板样品制备的流程、工艺和技术难点进行了实验和讨论,最终完成了合格样板的制备,并具备小批量产品的生产能力。本文研究的有机基板制造工艺方法是半加成(SAP)工艺,关键技术包括三个方面:一是精细线路的实现技术,二是可多次积层的层间微导孔互连工艺,三是超薄介质层制作工艺。