基于ZedBoard的真随机数发生器实验设计

2020-03-09万国春丁国鹏童美松

万国春,丁国鹏,童美松

(同济大学 电子与信息工程学院,上海 200092)

Xilinx 公司推出的ZedBoard 是基于Xilinx Zynq-7000 SoC 的低成本开发板,实现了双核Cortex-A9 MPcore 和28 nm 制程的7 系列可编程逻辑器件的紧密集成,在视频处理、图像识别、航天航空等领域得到了广泛的应用[1-7]。

本实验旨在让学生了解熟悉较先进的开发技术,掌握Xilinx 可编程嵌入式芯片的原理和使用方法,为进行更加深入的科研训练打下良好的基础,使其能够基于ZedBoard 实现更多更为复杂的工程与应用。实验中所实现的真随机数发生器作为与信息安全和密码学相关的多种算法的基础[8-10],也具有很高的实用价值与实际意义。

1 实验系统结构

本实验主要涉及Zynq-7000 SoC 开发和PC 端工具的使用,在Zynq-7000 中的可编程逻辑(programmable logic,PL)部分使用Verilog 硬件描述语言实现熵源与采样,再通过通用异步收/发传输器(universal asynchronous receiver/transmitter,UART)通信将采样得到的随机数在可编程系统(processing system,PS)中经算法处理之后转发至PC 端,在PC 端保存数据,并借助Cygwin平台进行NIST 随机性标准测试检验生成的随机数的质量。

1.1 ZedBoard 基本信息

ZedBoard 开发板中主控芯片为Zynq-7020,是由Xilinx 公司推出的全可编程嵌入式控制芯片,其特殊之处在于集成两个ARM Cortex-A9 和现场可编程逻辑门阵列(field programmable gate array,FPGA)资源,将很多场景中使用到的ARM+FPGA 双芯片架构整合到了一块SoC 上,提高了两者之间的数据交换效率,同时还提供了大量的相关IP 核,极大地便利了开发者的使用,降低了开发成本,为各种应用提供了便捷的解决方案[5]。实物图如图1 所示,包含了丰富的外设接口,通过板载USB 接口进行比特流与程序烧录,开发十分便利。

PS 部分主要包含嵌入式处理器和其处理资源,在应用处理单元(APU)中,包含双核Cortext-A9、256 KB片上内存、512 KB 二级缓存,并通过高级微控制器总线架构(advanced microcontroller bus architecture,AMBA)与PL 端及各类I/O 外设相连,其中包含以太网、USB、UART、CAN、SPI、I2C 和GPIO 等。

图1 ZedBoard 实物图

PL 部分主要为可编程逻辑资源,基于Artix-7 和Kintext-7 系列FPGA,主要包括通用FPGA 逻辑资源、XADC 模数转换器、独立时钟、高速DSP 以及RAM。

Zynq-7000 系列SoC 的内部结构如图2 所示。

图2 Zynq-7000 系列SoC 内部结构框图

1.2 真随机数发生器

在加密系统中具有极其重要地位的真随机数发生器,需要通过对物理随机现象进行提取,从而得到随机数,其核心部分是噪声源(熵源),通常由电路或物理实验实现。而使用特定结构的电路作为熵源具有实现简单、成本低、速率高等优点[8-11],故在本实验中对基于FPGA 的真随机数发生器进行实现与验证。

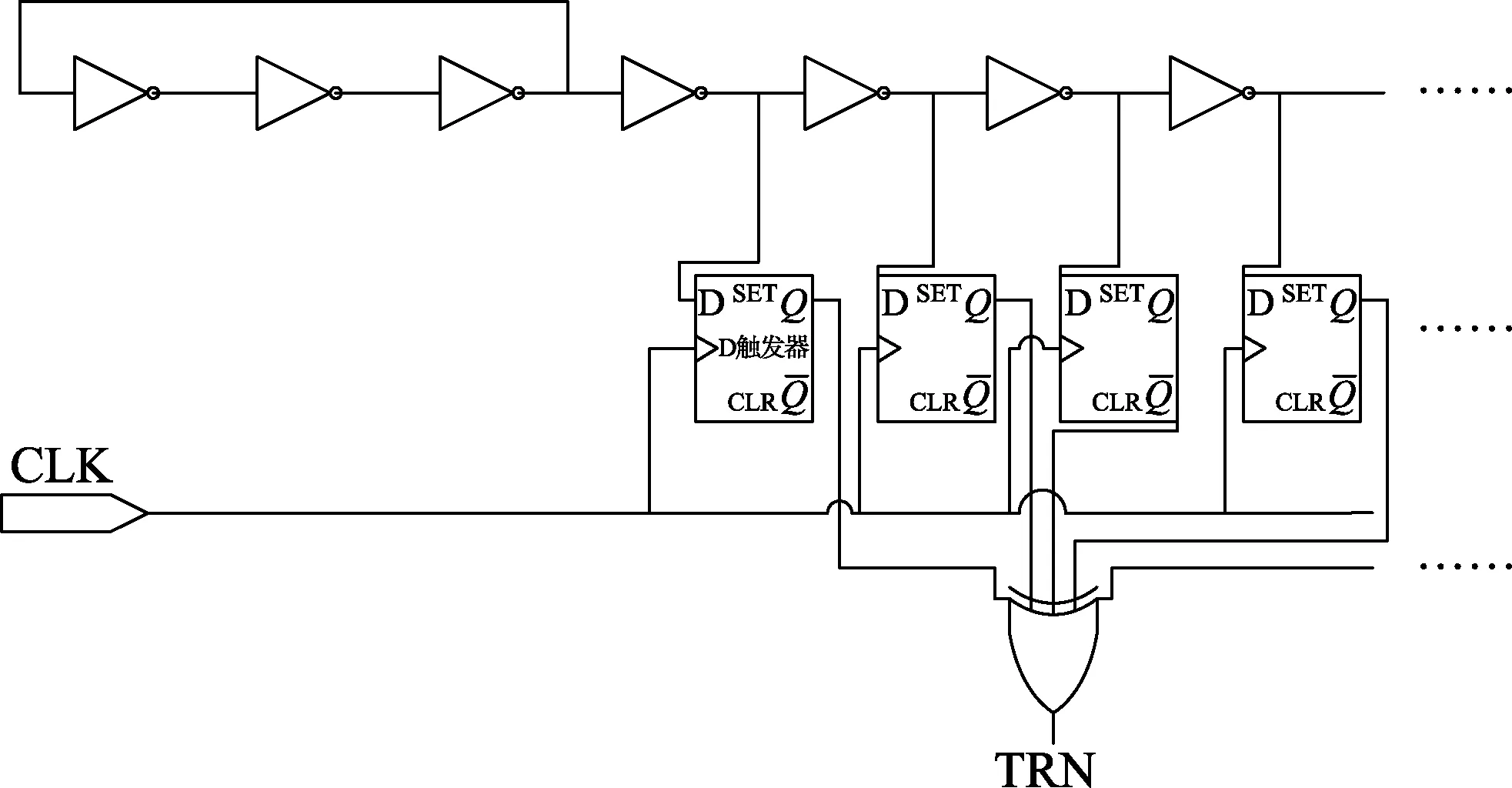

本实验采用基于环形振荡电路与D 触发器的结构作为熵源,使用3 个反相器组成环形振荡器产生频率较高的振荡,并利用D 触发器需要输入信号满足建立时间与保持时间的要求,否则输出随机的特性产生随机数,结构如图3 所示。在环形振荡器后增加反相器延迟链后,对每个反相器后信号使用D 触发器进行采样,只要其中一个D 触发器的采样CLK 到来时,其输入信号也在进行跳变,便可产生随机数。当在环形振荡器后使用512 个及以上反相器和D 触发器时,可保证产生足够的随机性[9],即几乎每次采样都有D 触发器的输入信号不满足建立时间和保持时间的要求。

图3 基于环形振荡器和D 触发器的熵源结构

1.3 UART 通信协议

通用异步收发器通信协议作为常见的通信协议具有无需时钟信号、仅需tx 和rx 两个接口、简单易实现等优点。本实验采用UART 通信协议将熵源采样电路生成的随机数序列发送至与PS 连接的AXI Uartlite IP,从而使PS 端接收到这些随机数。UART 通信过程中发送数据的时序图如图4 所示。空闲时输出时钟为1,起始位为一个时钟节拍的低电平,随后为8 位数据位,数据发送结束后输出一个时钟节拍的高电平,表示停止位。

图4 UART 通信发送时序图

在FPGA 中实现串口通信需要编写简单的状态机实现数据的发送,状态转移过程如图5 所示。其中IDLE 状态等待send 信号,tx 输出始终为1,当检测到send 的上升沿时,开始一次数据发送,进入START状态;START 状态下发送起始位,即tx 输出0,下一 个时钟节拍进入SEND_DATA 状态;SEND_DATA 状态下串行发送8 位数据,当count 为8 时即8 位数据发送完毕,此时进入STOP 状态;STOP 状态下发送停止位,即tx 输出高电平,一个时钟节拍后回到IDLE状态。

图5 UART 发送状态机状态转移图

1.4 AXI Uartlite IP 核

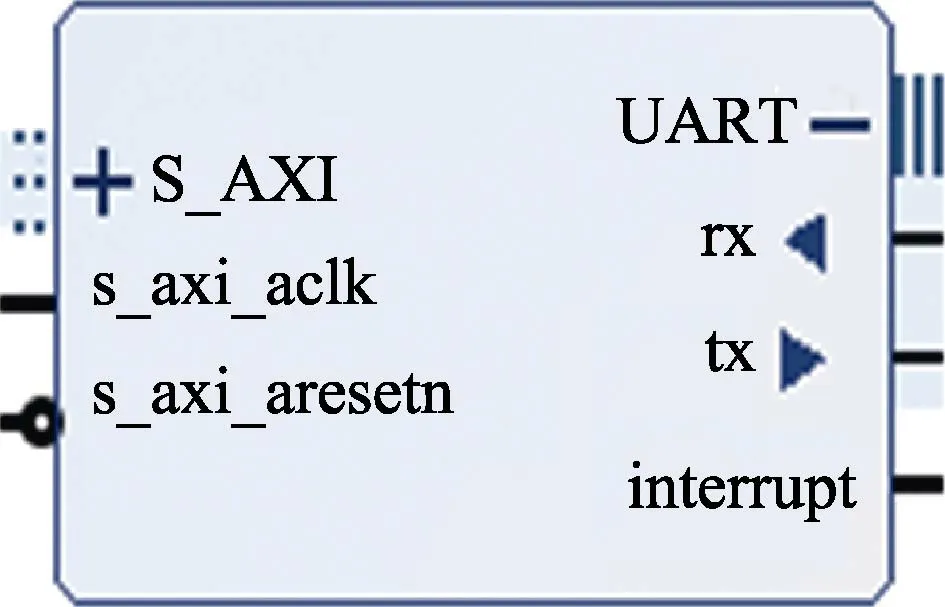

将从熵源采样得到的随机数序列通过带有中断功能的AXI Uartlite IP 核发送至PS 端,此IP 核主要接口如图6 所示,主要包含UART 的tx 和rx、AXI slave端的相关端口以及中断信号。此 IP 功能为将采用UART 协议传输的数据转换为先进可扩展接口协议(advanced extensible interface,AXI),并在接收到数据时产生中断信号。

图6 AXI Uartlite IP 核接口

1.5 系统结构

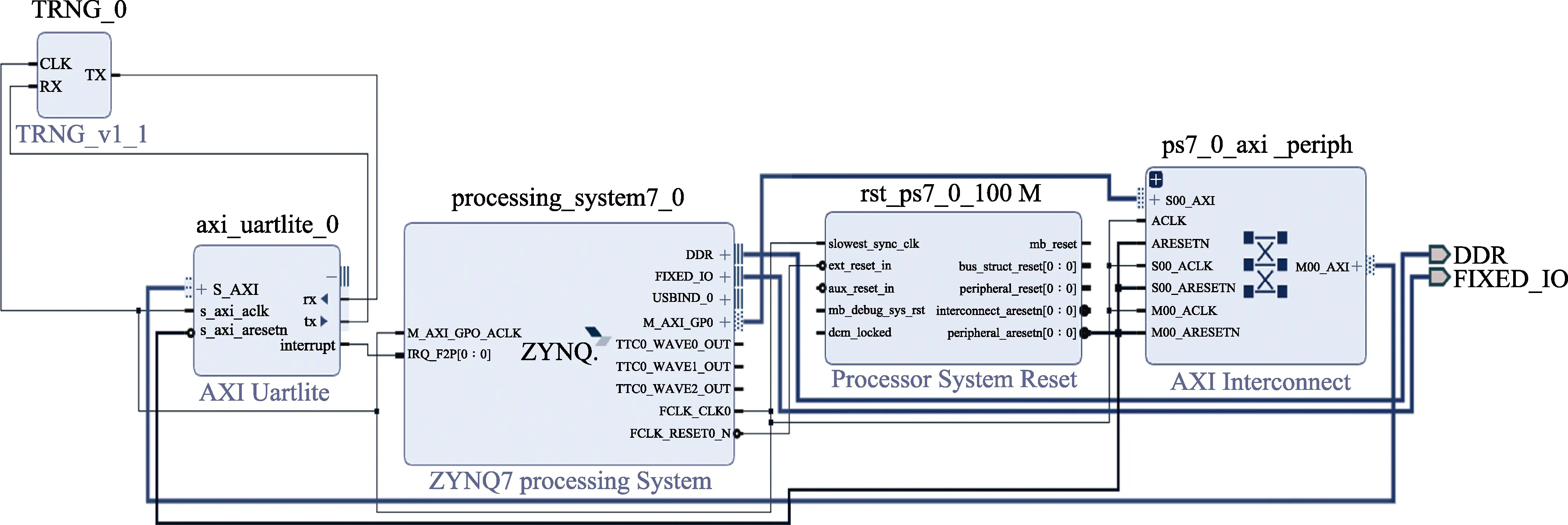

整个系统PL 与PS 端各部分连接情况如图7 所 示,真随机数发生器(true random number generator,TRNG)的tx 与AXI Uartlite IP 的rx 相连,rx 与AXI Uartlite IP 的tx 相连,AXI Uartlite IP 的interrupt 端口连接至PS 的IRQ_F2P 中断请求端口,其余模块的生成与端口的连接在创建最小系统时由Vivado 自动完成。

图7 系统块设计图

其中TRNG 是在PL 端实现的真随机数发生器,使用Verilog HDL 实现对基于环形振荡器和D 触发器的熵源进行采样,采样满8 次后,按照UART 通信协议要求将数据发出。AXI Uartlite 接收到数据后按AXI协议将数据转发至PS 的AXI 接口,并产生中断信号,通知PS 已经收到数据,触发中断处理函数执行。其余接口如DDR 是处理器DDR 内存寻址接口,FIXED_IO则是专用的内部固化的外设I/O。Processor System Reset(处理器系统复位模块)与AXI Interconnect(AXI 总线互联接口模块)及其接口连线均由Vivado 自动生成。

2 软件设计

本实验中PS 端负责完成数据转发,并对随机数序列进行算法后处理[12],本实验中采用线性反馈移位寄存器(linear feedback shift register,LFSR)作为处理算法,由1 位随机数转化出8 位随机数,从而大大提高随机数生成速率。LFSR 算法的示意图如图8 所示。

图8 LFSR 算法示意图

图8 中LFSR 长度为k,反馈多项式的多样化决定了LFSR 的多样性,通过循环移位后,将最后一级输出与输入做异或运算后反馈到最低位,输出低8 位寄存器中存储的值即可。

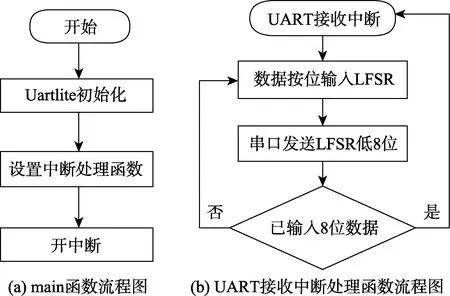

图9 程序流程图

在PS 端中的main 函数流程和中断服务子程序流程图如图9 所示,首先对与Uartlite IP 相连的AXI 总线地址进行初始化,使之能够正常接收发送数据,然 后设置 UART 的接收中断处理函数,每次接收到UART 数据都触发此处理函数,最后使能中断。UART接受中断处理函数中主要完成LFSR 处理算法并将其输出通过PS 端的串口发送至PC,主要流程为进入中断后将8 位的数据按位输入LFSR,每输入1 位就将LFSR 的低8 位发出,直到收到的8 位数据全部输入LFSR 后退出中断,等待下一次数据接收。

3 实验效果

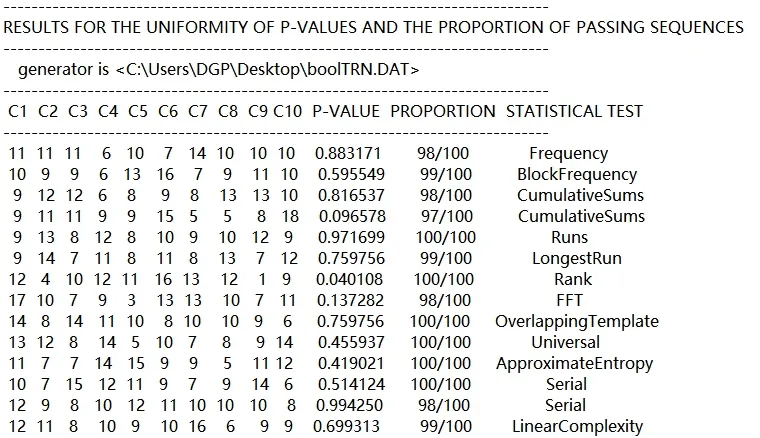

在PC 端使用串口助手设置波特率为115 200、1位停止位、8 位数据位、无奇偶校验等通信参数后,即可接收到由ZedBoard 发来的随机数序列(见图10)。当接收满100 Mbit 数据后,将其保存为txt 文件,使用Cygwin平台通过NIST提供的随机性测试软件对其进行测试,将100 Mbit 数据分为100 组进行测试,结果中P-VALUE 值大于0.01 即可认为通过了该项测试,观察测试结果文件可以发现本系统输出的随机数序列能够通过全部15 项测试,可以作为安全的随机数(见图11)。

图10 串口接收到的随机数序列

图11 NIST 标准测试结果

4 结语

本实验实现了基于ZedBoard 的真随机数发生器,使用UART 和AXI 通信协议传输数据,构建了由Zynq PL 端到PS 端到PC 的完整数据通路。实验过程涵盖了Zynq-7000 系列SoC 的基本开发流程、中断处理、真随机数发生、随机数后处理算法等知识,将嵌入式开发与硬件描述相结合,使学生了解并熟悉了此类工程的开发方法,积累了开发经验,并对随机数生成原理[13-14]有了一定的知识基础。整个过程中需要使用Verilog 硬件描述语言设计并实现电路、调用IP 核、完成PS 系统搭建、在SDK 中使用C 语言处理来自PL 端的数据并通过串口发送至PC,整个过程让学生对FPGA开发与嵌入式开发的仿真与调试过程有了深刻的体会。

同时本实验实现的Zynq-7000 系列SOC 的PL 端到PS 端再到PC 端的数据通路适用于各类工程,掌握后能方便地应用于其他项目与工程的开发中。