基于国产FPGA的千兆以太网交换机复位系统设计

2020-02-27王立莹左延智

王立莹,左延智

(1.中国电子科技集团公司第五十四研究所,河北 石家庄 050081;2.北京跟踪与通信技术研究所,北京 100094)

0 引言

经过多年的发展,我国数据通信设备制造业坚持技术引进和技术开发相结合,已经实现了网络设备的整机国内设计和整机国内集成,并广泛应用于各行业信息系统建设中[1]。但国内生产的网络设备中,核心电子元器件主要采用国外产品,高端芯片等核心要素受制于人,网络装备总体自主化程度低[2]。电子元器件是数据通信设备的基础,是保证数据通信设备可靠运行的基本单元[3]。电子元器件性能指标、质量与可靠性以及供货保障能力直接关系到数据通信设备的性能、研制生产进程以及产品的售后保障能力等[4]。我国电子元器件产业受各种因素的影响,在元器件的门类、品种、性能和质量可靠性方面与国外产品相比都有较大差距,成为制约我国通信行业发展的瓶颈之一[5]。

核心元器件采用国外产品,关键技术受制于人,致使网络设备在本质属性上存在严重的安全隐患[6]。首先,在网络空间对抗日趋激烈的背景下,西方国家有意愿有能力利用芯片内部可能存在的后门密码、数据包监测和恶意攻击等,操控网络与信息系统、破坏关键业务数据、窃取核心机密信息及干扰网络运行,甚至致瘫设备和网络,给国家和国防信息系统构成安全威胁;其次,各发达国家均把核心电子元器件作为影响国家安全的战略资源加以控制,把限制核心电子元器件的出口作为一项基本国策[7]。例如美国政府制定严格的政策和相关措施限制高新技术及产品出口;美国商务部制定商品管制清单,规定符合相关性能指标的产品严禁出口到相关国家和地区[8]。西方国家还可通过对核心元器件、标准规范和核心技术专利的垄断,形成对网络与信息系统装备供应链的安全威胁。尤其对于我国国防信息化装备,有必要且急切需要实现交换设备的自主可控。

交换机国产化的关键是国产化核心电子元器件的应用,但也应清楚地认识到国产芯片的不足,与国外芯片相比,在性能、体积、功耗、集成度、可靠性、成本及配套软件等方面都有一定的差距[9]。尤其是交换机内部集成电路的增多导致了交换机上电复位的复杂性,为了降低使用国产芯片对交换机功能、性能指标的影响,保证千兆以太网交换机的稳定运行,要充分考虑硬件性能、稳定性、可靠性及扩展性等因素,在设备上电启动和运行过程中支持对部分芯片或模块的复位[10],并提供不同的复位时序用以满足交换机内部不同芯片的启动顺序及复位时间要求[11],提高整个系统的可靠性,以弥补国产器件的不足。因此,对以太网交换机复位系统的研究就非常有必要,本文从千兆以太网交换机的逻辑组成介绍出发,讨论千兆以太网交换机复位系统的设计方法和设计过程。

1 交换机逻辑组成

千兆以太网交换机主要由以太网交换模块、CPU模块、逻辑控制FPGA模块、千兆以太网模块及时钟模块等组成,如图1所示。

图1 以太网交换机逻辑组成Fig.1 Logic composition of ethernet switch

以太网交换模块作为千兆以太网交换机的核心,主要完成业务数据路由交换功能,设计选用苏州盛科公司的万兆以太网交换芯片CTC6048,对外提供SGMII Serdes接口、数据通道接口、控制接口及管理接口等[12]。CPU模块完成交换机的控制与协议处理,是各种路由协议运行的平台,国产CPU芯片[13]采用中国科学院计算研究所的64位处理器芯片龙芯2F[14]。千兆以太网模块实现千兆以太网线路接口,用于用户业务接入。逻辑控制FPGA模块主要实现各种可编程控制和业务处理逻辑,为设备提供复位控制、时钟变换和寄存器维护管理等功能,选用上海傲格芯公司的AG10KF256[15]。时钟模块主要为相关功能单元提供时钟参考,选用成都振芯科技公司的时钟芯片。

2 硬件电路设计

在复位电路设计时,需要综合考虑各芯片对复位的要求,如复位高低电平、复位顺序及复位脉冲宽度等,且在设计中需实现以上形式组合多变的复合设计。通过合理选择器件、逻辑设计,实现电路的需求。

以太网交换机内需要复位信号的模块包括CPU模块、时钟模块、千兆以太网模块及以太网交换模块等,各模块的复位逻辑主要由FPGA完成,具体复位电路逻辑如图2所示。

图2 复位电路逻辑框图Fig.2 Logic block diagram of reset circuit

3 软件设计

3.1 上电复位时序设计

以太网交换机中大多数芯片的复位都需要在供电和参考时钟稳定后进行,在供电稳定后,首先要复位时钟芯片,然后完成时钟芯片的初始化配置,在时钟芯片输出时钟稳定后,再复位其他芯片。

时钟芯片支持多种复位方式,包括上电复位、异步RESET管脚复位和寄存器软复位,本设计采用FPGA直接控制时钟芯片的异步RESET管脚完成时钟芯片的复位,根据时钟芯片的异步复位时序要求,需要保证低电平脉冲≥50 ns。该复位信号采用“1-0-1”电平方式,先保持CLOCK_RST高电平10 ms,然后低电平脉冲10 ms,然后置高,完成一次时钟芯片的复位操作。

在时钟芯片复位后等待10 ms再开始时钟芯片的配置过程,让时钟芯片复位生效,在时钟芯片配置完成并输出时钟稳定后,再复位其他芯片,该过程主要取决于配置芯片时间和VCO的校准时间,配置芯片时间不大于5 ms,VCO的校准时间如下:

(1)

根据参考时钟频率、输出时钟频率等因素,可获得R取值1,cal_div取值2,fREFIN为25 MHz,根据式(1)计算VCO校准时间为0.352 ms。整个配置芯片时间加上VCO校准时间不大于10 ms,该过程取值10 ms。

千兆以太网芯片要求的复位时序为“0-1-0-1”电平方式,其中tW为在上电和时钟稳定后NRESET可配置的时间,不小于2 ms;tREC为恢复时间,不大于105 ms;tW(RL)为低电平脉冲时间,不小于100 ms;tWAIT为NRESET置高后可以访问SMI接口时间,不小于105 ms。参照复位时序要求,本设计中千兆以太网芯片的GE_PHY_RST复位信号先保持GE_PHY_RST低电平40 ms,然后置高电平150 ms,再低电平保持110 ms,然后置高,完成千兆以太网芯片的复位。

龙芯2F的复位时序要求在CPU_RST拉低之前,相关的时钟信号、测试信号和初始化信号都必须有效,CPU_RST低电平脉冲要求至少一个时钟周期。本设计中CPU_RST复位信号采用“1-0-1”电平方式,先保持CPU_RST高电平40 ms,然后低电平保持到以太网PHY芯片复位完成,保证CPU初始化程序运行前以太网PHY芯片的SMI接口工作正常,低电平时间取370 ms,然后置高。

CTC6048的复位信号主要包括全局复位信号RST_B、PCI接口复位信号PCIRESET_N、DDRDL复位信号DLRESET和CPU寄存器访问接口复位信号SURST_B。本设计中RST_B、PCIRESET_N、SURST_B信号采用“1-0-1”电平方式,先保持高电平40 ms,然后低电平保持370 ms,然后置高,与CPU_RST一致。DLRESET信号采用“0-1-0”电平方式,先保持低电平40 ms,然后高电平保持370 ms,然后拉低。

3.2 FPGA设计

FPGA复位模块信号主要包括CPU接口、SPI接口和复位信号等,复位模块顶层原理如图3所示。

图3 复位模块顶层原理Fig.3 Top level principle of reset module

FPGA程序主要包括时钟分频、计数器、时钟芯片初始化配置及CPU软复位寄存器等,完成时钟芯片的初始化、各芯片的上电复位及软件复位控制等功能。

FPGA通过SPI接口间接访问配置时钟芯片内部寄存器,时钟芯片配置程序流程实际是全部寄存器配置的写入流程组合,单个寄存器配置流程:① FPGA将要配置的寄存器地址写入地址寄存器;② FPGA将要写入寄存器的数据写入写数据寄存器;③ 开始写操作;④ 将并行的地址、数据串行的写入时钟芯片SPI接口。通过时钟芯片配置程序,完成需要配置的时钟芯片寄存器的写操作,实现时钟芯片的整个配置流程。

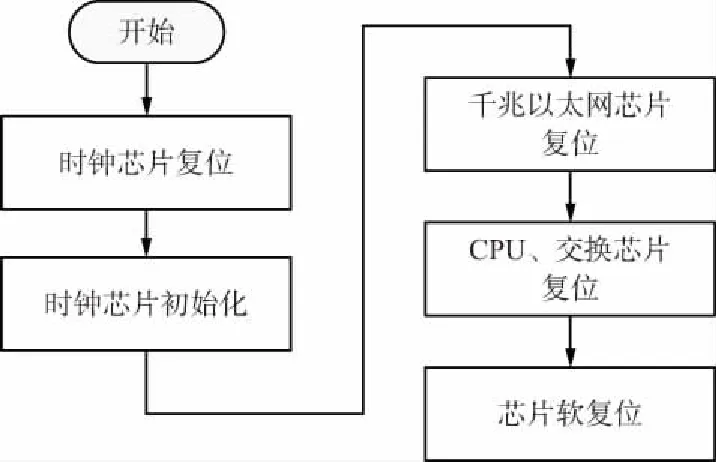

上电复位程序参照上电复位时序,通过计数控制各芯片复位信号的高低电平。在设备上电初始化过程中或设备正常工作中,为了增加设备的可靠性,增加了部分芯片的自检程序或状态监控程序。当CPU判断到特定接口或芯片发生故障,可以通过软件控制FPGA完成相应芯片的复位。CPU与FPGA间互联接口为Local Bus总线,CPU可以通过该接口访问控制FPGA内相应的复位控制寄存器,完成复位。通过将各芯片的上电复位信号和相应软复位信号进行“与”“或”组合,可以得到既保留上电复位时序又可以通过CPU控制的复位信号。复位程序流程如图4所示。

图4 复位程序流程Fig.4 Reset procedure flow

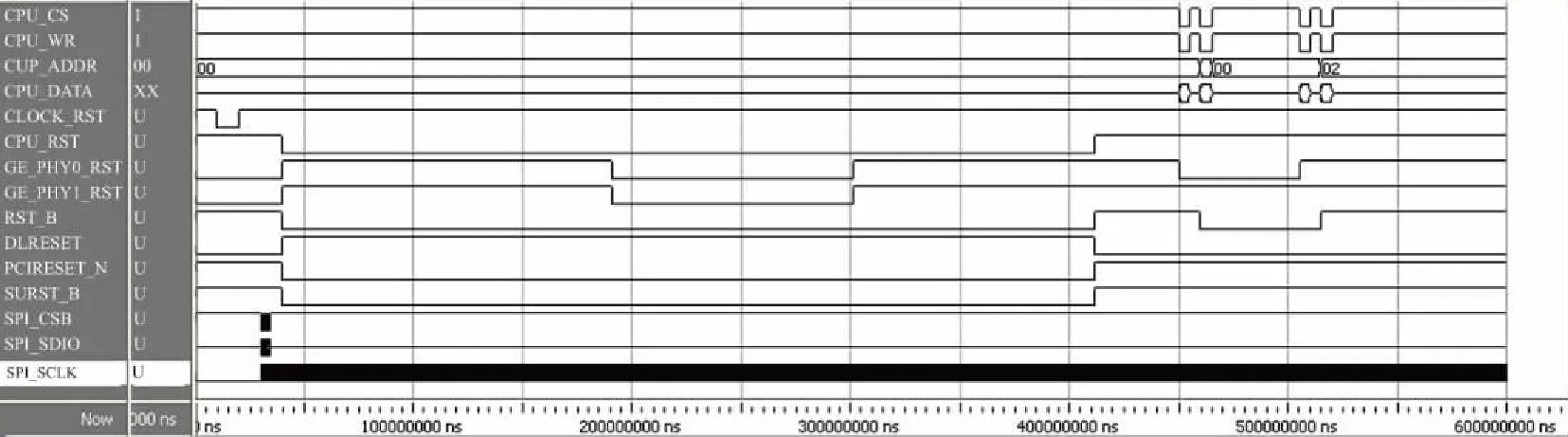

本设计采用上海傲格芯FPGA芯片AG10KF256,整个设计采用VHDL硬件描述语言来实现,在Quartus II 11.1开发软件上完成设计、综合及布局布线。通过上海傲格芯的开发软件Supra完成工程转换和编译,并使用ModelSim进行时序仿真。交换机复位时序如图5所示。在图5中,先完成了时钟芯片的复位,然后开始时钟芯片的初始化配置。在时钟芯片输出时钟稳定后,实现了CPU、交换芯片及千兆以太网芯片的上电复位过程。在CPU正常工作后,通过CPU接口访问控制FPGA内复位控制寄存器,分别控制了GE_PHY0_RST和RST_B复位,实现了交换机内芯片的软复位功能。

图5 交换机复位时序仿真Fig.5 Simulation of switch reset sequence

4 结束语

本文从千兆以太网交换机的逻辑组成出发,研究了以太网交换机复位系统的实现原理,分析了软硬件设计的实现过程,提出了以太网交换机的上电复位及软件复位方案,并最终给出了一种适用于千兆以太网交换机的复位系统。通过FPGA实现交换机的复位,具有处理速度快、方便灵活和可扩展性好的特点。该设计满足千兆以太网交换机的国产化需求,上电复位结合软件复位方案可以推广到其他交换设备中,能提高整个设备的可靠性,有着很好的应用效果。