基于FPGA硬件时间流与GPS的同步采集系统设计

2019-11-26张嘉霖王世隆魏一鸣宋树超许佳男于生宝

张嘉霖, 王世隆, 魏一鸣, 宋树超, 许佳男, 于生宝

(吉林大学 仪器科学与电气工程学院,长春 130061)

0 引 言

半航空无人机电磁探测方法是一种当前热门的地球物理探测手段,采用地面发射电磁场,空中用无人机载传感线圈进行接收[1-4],往往通过GPS模块接收GPS卫星发送的秒脉冲和串口数据获得时间地点同步信息,实现发射系统和接收系统的同步。但是根据大量工程飞行实验,发现GPS模块本身受到天气、环境等因素影响,同步信号极易短时丢失,导致实验失败。张良等[5-6]设计的电磁接收机采用GPS同步方式,但是并未提及GPS卫星失锁导致同步信号丢失的情况;吴寿勇[7]虽然提到了GPS同步信号丢失的问题,但是并未对具体解决方案进行论述。姬智艳等[8]提出了一种高精度GPS时钟同步用于瞬变电磁仪,通过STM32内部计数器以168 MHz频率产生一个±90的窗口对GPS秒脉冲信号进行判断,虽然能够对丢失的GPS同步信号进行补充,但是判断误差较大可达535 ns,并不适用于半航空无人机电磁探测。本文既考虑GPS同步的部分有效性,又兼顾其可能产生的不稳定性,为解决探测过程中同步信号短时丢失问题,提升探测效率,设计了一种基于FPGA硬件时间流与GPS的同步采集系统。该系统能够实现半航空无人机电磁探测数据同步采集,并通过相应的实验予以验证。

1 方案设计

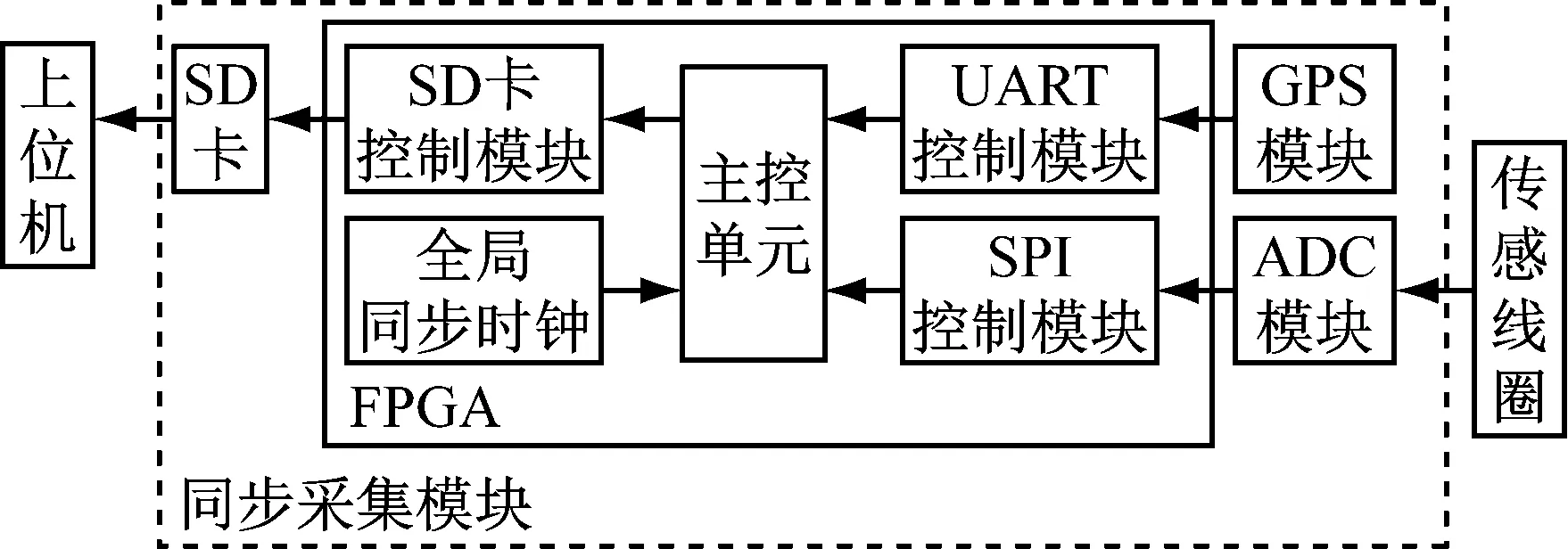

图1 电磁探测同步采集系统的功能框图

2 数据接收

2.1 GPS数据提取

GPS能为全球用户提供低成本、高精度的三维位置、速度和精确定时等导航信息,为使同步信号较好,通过配置模块Ublox-M8N采用北斗加GPS的方式进行同步定位。根据需求只需要提取串口数据GNGGA即可获得工程所需的时间以及定位等信息。此外,为了获得高精度的时间同步信息,Ublox-M8N还提供精度约为60 ns,占空比10%的秒脉冲信号(官方手册)。

为了尽快获得串口GNGGA数据,将Ublox-M8N设置串口端口波特率为115 200、1位起始位、8位数据位、1位停止位、无奇偶校验位,EP3C16Q240C8N采用状态机方式接收串口数据[12],将50 MHz时钟以27分频生成约为115 200的16倍频时钟信号,即每16个时钟接收1位数据,为保证0误码接收数据,采用中间取样方式,根据LVTTL标准的串口通信协议,首先通过延时消抖的方式对数据Tx端口(GPS模块)进行下降沿检测,此时将占用3个时钟,当检测到下降沿时,经过5个时钟开始接收起始位,之后每经过16个时钟接收1位数据,当收到停止位时,状态机跳转至起始状态,完成一次循环。

依据GNGGA数据长度,FPGA内部生成长度为100 B的寄存器,地址范围为0 ~ 99用于缓存GPS串口数据,以及1位标识位寄存器表示一帧接收完毕。采集系统上电后,首先将地址和标识位清0,然后每当串口模块接收一个字节后,进行判断,若为“$”则开始存储数据并且地址+1,若不为“$”则继续判断,当检测到“LR”时,存储数据后将标志位置1并且地址指向0,继续判断GNGGA字头标识符“$”,工作流程图如图2所示。

图2 GNGGA串口信息缓存流程图

2.2 ADC数据提取

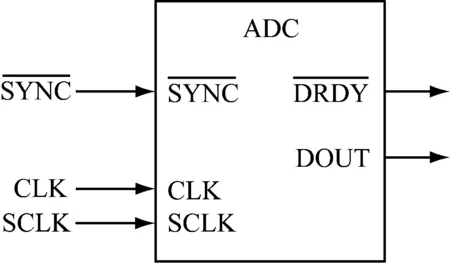

信号采集电路通过ADC(模数转换芯片)将接收线圈感应的模拟电压信号转化为数字电压信号,为使ADC能够正常工作,驱动电路原理示意图如图3所示。图中,ADC为24位高精度模数转换芯片ADS1271;OPA为轨对轨全差动运算放大器OPA1632;REF为电压基准芯片REF1004I-2.5。OPA1632利用REF1004I-2.5所产生的+2.5 V基准电压将共模电压0 V,量程±10 V的差分信号转化为共模电压+2.5 V,量程±2.5 V的差分信号以满足ADS1271的需求,ADC连接示意图如图4所示。

图3 ADC驱动原理示意图

图4 ADC连接示意图

3 同步时钟构建

3.1 数据整合

FPGA内部生成两个FIFO[13],其中FIFO1用于缓存ADC数据d1和ADC时间流数据u1;FIFO2用于缓存GPS串口数据d2以及秒脉冲时间流数据u2和串口信息字头“$”符号时间流数据u3。系统工作时,GPS串口数据不断向寄存器R1刷新,每当ADC数据缓存至设定值时,将寄存器R1的数据传输至寄存器R2中,并与u2、u3依次缓存至FIFO2中。

每缓存一组数据后,即将FIFO1和FIFO2的数据依次通过SD卡控制模块存储至Micro SD卡中,数据格式“d1,u1,d2,u2,u3”,并且保证FPGA内部FIFO处于半满状态以完成数据连续采集。

3.2 时间同步信息获得与补充

对于每一组数据“d1,u1,d2,u2,u3”,u1表示为ADC数据开始接收时刻;u2表示为数据采集时所对应GPS秒脉冲上升沿的时刻;u3表示为所接收GPS串口数据的时刻。将u3与其接收的GPS串口数据内的UTC时间对齐,根据u1、u2、u3数值大小依次排列,通过比较GPS秒脉冲上升沿时刻的时间流数据即可获得精度高达20 ns的时间同步信息。

根据实际需求,设置GPS串口数据输出频率为1 Hz,对于Ublox-M8N模块,其秒脉冲信号与串口信息互不相干,即使卫星失锁,秒脉冲信号丢失,串口信息依然按照所设定的频率输出,只是内部信息丢失,因此可以通过GPS串口信息的个数推算出所丢失秒脉冲信号的个数,再根据线性插值下式获得所丢失的秒脉冲所对应的时间流数据[14-15],

式中:l、m、n为秒脉冲信息序号,其中,m、n为有效信息,l为所求无效信息;y表示所对应的时刻值,单位为20 ns。取秒脉冲与串口数据同时有效并且距离秒脉冲信号丢失时两端最近的时间信息作为有效信息,通过线性插值计算出中间丢失的秒脉冲时间信息。

4 系统测试及结果分析

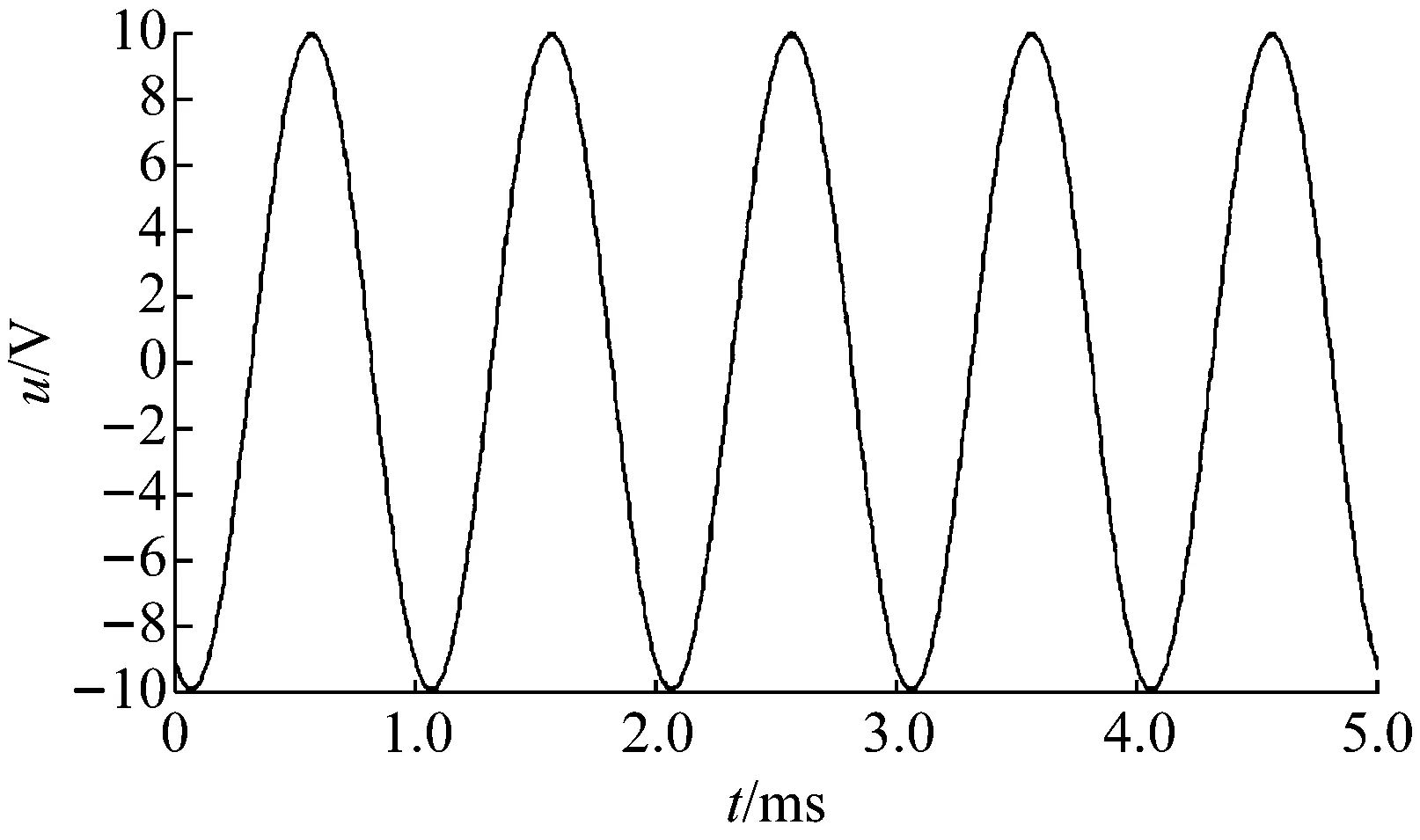

通过系统采集信号发生器Agilent 33500B所输出的频率为1 kHz,峰峰值为20 V的正弦波进行ADC数据采集测试,测试完成后通过上位机根据采样率将离散的电压数据还原成时域波形,采集测试结果如图5所示。

图5 波形数据图

由图5可知,采集系统能够实现量程为±10 V信号的连续采集。与此同时获得的硬件时间流数据以及插值数据如表1所示。

表1 时间流数据

表1中插值时间为假定序号1、10数据有效,再通过线性插值公式获得序号2~9的数据,与真实数据对比可知仅在最低位(20 ns)产生误差,表明该方法可以精确获得丢失的秒脉冲时间信息。

经过多次测量,将秒脉冲时间通过下式换算至秒脉冲上升沿间隔长度数据,

tn=un+1-un

式中:u为秒脉冲原始数据;n为序号;t为秒脉冲上升沿间隔长度数据。统计每次实验所得极差,如图6所示。图中,横坐标为测试实验序号,单次实验1 min;纵坐标为每次测试极差值。经计算得出平均值为122.8 ns、标准差为27.28 ns,表明本文设计的系统同步精度较高,约为122.8 ns,并且偏差较小,相比最大采样率105 kHz的ADS1271,误差可忽略不计,满足实际需求。

图6 多次实验结果统计图

5 结 语

本文设计的基于FPGA硬件时间流与GPS的同步采集模块,充分利用了FPGA并行及实时性高等优势,能够高精度地获得GPS模块所输出的时间地点同步信息,并且当GPS卫星失锁时,通过内部晶振产生的时间流计数器,利用线性插值将所丢失的秒脉冲数据予以补充。实验表明,该系统同步性能较高,满足实际需求,在半航空电磁探测中具有广阔的应用前景。