过钻具阵列声波测井采集电路设计与实现

2019-11-15侯君红余厚全文荣辉刘付火邹骁陈强李剑

侯君红 余厚全 文荣辉 刘付火 邹骁 陈强 李剑

摘要:针对过钻具阵列声波测井对信号采集电路高精度、大动态、低噪声、低功耗、高集成度以及各通道同步性好的要求,设计一种多通道数据采集电路。该电路采用各通道独立数字化方案以保证各通道信号采集的同步性,采用低噪音仪表放大器作为前置放大器以降低系统噪声,选用18位ADC扩大数字化动态,ADC输出采用菊花链连接以减少电路连线。实测结果表明:12通道采集电路功耗为550mW,噪声均方根值小于13μV,信号测量动态范围达93dB,单通道采集电路面积为19mm×70mm。因此,设计电路既能很好满足过钻具阵列声波测井信号采集要求,也可作为其他阵列声波测井信号采集的参考方案。

关键词:过钻具测井;阵列声波测井;数据采集;低噪声信号调理电路;噪声测试

中图分类号:TE135;TB51

文献标志码:A

文章编号:1674–5124(2019)03–0135–04

Design and implementation of acquisition circuit for trough bit array acoustic logging

HOU Junhong1, YU Houquan1, WEN Ronghui1, LIU Fuhuo2, ZOU Xiao2, CHENG Qiang2, LI Jian2

(1. Electronics & Information School, Yangtze University, Jingzhou 434023, China; 2. China Petroleum Logging Co., Ltd., Xian 710077, China)

Abstract: In order to meet the requirements for high precision, large dynamic, low noise, low power con- sumption, high integration and good synchronization in through bit array acoustic logging, a multi-channel data acquisition circuit is designed. A channel independent digitization scheme is proposed to ensure the synchronization of each channel. Low-noise instrumentation amplifier is chose as a preamplifier to reduce system noise. 18-bit ADC is used to expand digitization dynamics and the ADC output is daisy-chained to reduce the circuit connection line. The measured results show that the power consumption of the 12-channel acquisition circuit is 550 mW, the noise RMS value is less than 13 μV, the signal measurement dynamic range is 93 dB and the single-channel acquisition circuit area is 19 mm×70 mm. Therefore, the designed circuit not only satisfies the requirements for the acquisition of through bit array acoustic logging, but also can be used as a reference of other array acoustic logging.

Keywords: trough bit logging; array acoustic logging; data acquisition; low noise signal conditional circuits; noise test

0 言

為了满足大斜井和水平井的测井需求,更好地获取井周全方位、远地层的信息,不断提高测井效率,声波测井已从过去电缆全波列声波测井发展到随钻阵列声波测井[1-2],目前正向过钻具阵列声波测井发展。国外除美国斯伦贝谢公司开发了过钻具阵列声波测井仪器外[3],未见其他国家相关仪器的研发报道。国内中国石油测井公司正在进行相关研发,但未见报道。仪器开发的主要难点之一是这种测井方式对声波采集电路提出了更高的要求,主要是:1)多路信号采集要求同步误差小于0.1μs;2)仪器等效输入噪声<30μV,信号采集动态≥90dB;3)采集电路板宽度应小于20mm;4)电路功耗低,便于电池供电。目前国内随钻阵列声波仪器和美国斯伦贝谢公司开发的过钻具阵列声波测井都采用16位ADC数字化方案[4-8],无法满足远地层声波信号采集的要求。尽管在电缆阵列三维声波测井中已有采用24位ADC数字化方案的报道[9],但其芯片封装面积大、功耗高,不适合在过钻具阵列声波测井中应用。因此,在满足过钻具测井对采集电路尺寸和功耗要求的同时,提高信号采集精度和动态,就成为一个亟待解决的关键问题。

本文针对过钻具阵列声波信号采集需求,提出了一种新的数据采集电路方案,主要特点在于:采用各通道独立数字化设计保证多通道数据采集的同步性,选用小尺寸18位ADC扩大数字化动态,采用多个ADC数据菊花链连接串行输出方式减少电路板连线和尺寸,很好地满足了过钻具测井数据采集的要求。

1 采集电路方案设计

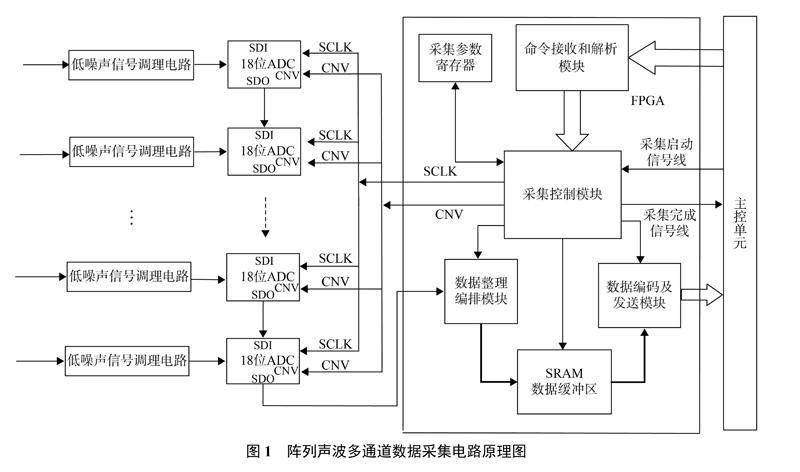

图1为本文提出的阵列声波多通道采集电路设计方案,它由两部分组成:1)多路声波信号采集电路,可接收井筒一个径向的多个传感器检测的多路声波信号,对其放大、滤波和数字化;2)声波采集控制与缓存电路,它接收来自主控单元的指令,对采集电路提供时序控制,并接收各路采集到的数据,对其进行编排和缓存,然后根据主控单元的指令将数据传送至主控单元。

对于采集电路而言,根据对采集电路各通道同步采集误差小于0.1μs的要求,采用各通道独立同时采集的数字化方案。为降低共模噪声对采集信号的影响,减少带外高频干扰和混叠噪声干扰,设计了低噪声信号调理电路,其由低噪声仪表放大电路、二阶有源低通滤波电路和驱动电路组成。为了满足大动态采集和高精度量化的要求,选用18位、速率为1MS/s的逐次比较型ADC芯片,并采用近换能器数字化方案降低干扰影响。为减少每个通道ADC的数据输出到采集控制和缓存部分的连线,避免布线过长引起的串扰和不稳定,采用多个ADC菊花链的工作模式,串行传输数据。整个多路声波信号采集电路的设计可根据具体的实际需求实现8路、12路或16路信号的同步采集。

控制与缓存电路由采集控制模块、命令接收和解析模块、SRAM缓存模块、采集参数寄存器和数据整理编排模块等组成。命令接收和解析模块用来接收主控单元的命令并解析命令的具体内容;采集控制模块则根据命令解析的结果产生相应的控制信号和工作时序,控制信号的采集、传输和存储;数据整理编排模块将ADC输出的串行數据转换为并行数据,并按通道顺序编排;SRAM数据缓存模块则是缓存一次激发接收的全部声波数据;数据编码及发送模块用来进行数据编码和数据上传,确保数据的正确传输;采集参数寄存器用来寄存信号采集的相关参数。整个控制与缓存电路采用FPGA+SRAM的结构,可方便地通过编程扩展功能。

2 采集电路具体实现

2.1 低噪声模拟信号调理电路设计

低噪声模拟信号调理电路如图2所示,主要功能是将接收换能器检测到的声波信号进行低噪声差分放大和低通滤波。为了降低系统的等效输入噪声,前置放大器选用ADI生产的专用仪表放大器AD8220,它具有高共模抑制比(>100dB)、低输入噪声(14nV/√Hz)、低功耗(静态电流<750μA)特性。放大增益由外置电阻Rg调整,通过增益选择模块改变增益电阻Rg的值可获得不同增益。二阶有源低通滤波器由低噪声轨到轨运放AD4084和相应电阻电容器件连接而成,通过改变反馈电阻Rf的阻值来实现截止频率随采样率的改变而改变。由于经过放大和滤波后的信号为双极性单端信号,根据ADC器件输入应为单极性差分信号的要求,增加了ADC驱动器(ADA4940-1)来完成这一转换。

2.2 ADC设计

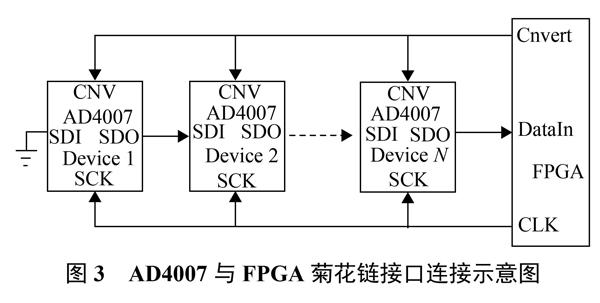

为满足幅度动态达90dB、频率范围为300Hz~30kHz的信号接收要求,ADC器件位数至少为16位,转换速率至少为60kS/s。为了降低对抗混叠滤波器的要求和保证波形描述的精度,ADC的最高采样频率应为声波信号最高频率的4~10倍。本文选用ADI公司推出的新一代低功耗、高速度、高精度、小尺寸、逐次比较型模数转换器AD4007。该芯片转换精度为18位,转换速率最高可达1MS/s,最大功耗为8mW,差分模拟输入范围可达±VREF,工作温度范围为–40~125°C,尺寸大小为4.9mm×3mm×0.85mm,具有SPI兼容型多功能串行接口,特别是该器件支持多个ADC总线的数据输出菊花链接法,可以有效减少多通道采集电路的信号走线。多个ADC与基于FPGA的控制模块连接示意图如图3所示,可根据实际需求选择ADC个数。芯片的以上特性非常适合井下阵列声波信号采集。

2.3 信号调理电路噪声理论估计

信号调理电路噪声分布示意图如图4所示。假设前置放大器、低通滤波器、ADC驱动器之间的噪声互不相关,其放大倍数分别为A1、A2和A3,则调理电路的总噪声[10]为

信号调理电路输出总噪声除以电路总增益可得到信号调理电路的等效输入噪声,其表达式为

根据各部分电路噪声模型[11-12],查询芯片的噪声频谱密度具体参数,即可估算出各级电路的等效输入噪声。已知前置放大器AD8220的输入噪声频谱密度为38.62nV/√Hz,在30kHz带宽下等效输入噪声为8.38μV;低通滤波器AD4048的输入噪声频谱密度为10.42nV/√Hz,在30kHz带宽下等效输入噪声为2.26μV;ADC驱动器ADA4940-1的输入噪声频谱密度为11.33nV/√Hz,驱动电路带宽为40kHz时的等效输入噪声为2.84μV。当前置放大电路增益A1为2.7,低通滤波器和ADC驱动器增益均为1时,根据式(2)计算出信号调理电路等效输入噪声为8.48μV。

3 测试结果与分析

按上述的设计方案,开发实现了阵列声波12通道采集电路,并对评价采集电路的性能指标进行了噪声和信号测试。

3.1 噪声测试

进行噪声测试时将差分输入短接,通过对采集到的样本点求均方差值作为噪声估计。当调理电路增益为2.7时,等效输入噪声波形如图5(a)所示,等效输入噪声值12.9μV。已知ADC的最大测量范围为–2.46~2.46V(ADC的实际参考电压为2.46V),调理电路增益为2.7时采集电路的最大输入信号峰峰值可达1.8V。计算信噪比,其表达式为[13]

通过式(3)得到其对应的最大的信噪比为93dB,表明该采集电路的噪声低,测量动态范围大。

3.2 信号测试

由信号发生器输出频率分别为4kHz和8kHz,峰峰值为1.8V的正弦信号,采集电路数字化的波形如图5(b)所示。采样率为100kS/s时,8kHz信号的采样波形有些失真,其原因是每周期采样点数(12.5个样本/每周期)相对于4kHz信号(25个样本/每周期)减少了一半。

由于实验室没有低幅值、高精度信号发生器,为了测试采集电路对小信号的数字化性能,采用普通信号发生器产生峰峰值为10mV、频率分别为4kHz和8kHz的正弦信号,然后通过电阻分压将其衰减1/10,形成峰峰值为1mV的信号送给采集电路进行数字化。数字化的波形如图5(c)所示。

信号测试结果表明,无论是对大幅度信号还是小幅度信号,多通道采集电路的数字化波形无畸变和毛刺,电路工作性能稳定,具有良好的大动态、弱信号检测性能。

4 结束语

本文根据过钻具阵列声波测井对信号采集的要求,设计实现了一种阵列声波信号采集电路。相对于国内外随钻和过钻具阵列声波仪器采用的16位ADC数据采集方案而言,本文采用了18位ADC的数字化方案,在满足电路功耗和尺寸的前提下,将信号采集动态扩大了12dB。与此同时,多通道ADC的输出数据采用菊花链连接的串行输出方式,既减少了电路板上的走线和电路板之间的连线,减小电路板尺寸,提高了抗干扰能力,同时也增加了采集通道的可扩展性。因此,该电路设计不仅对过钻具阵列声波测井有重要的实用价值,也为其他方式的阵列声波测井采集电路的设计提供了可行的参考方案。

参考文献

[1]吴晓光,季凤玲,李德才.偶极声波测井技术应用现状及研究进展[J].地球物理学进展,2016,31(1):380-389.

[2]ALFORDJ,BLYTHM,TOLLEFSENE,etal.随钻声波测井新技术[J].国外测井技术,2013,4(2):64-72.

[3]JAMESA,BENJAMINWC,TAYLORLR,etal.过钻头测井[J].国外测井技术,2013,34(3):70-75.

[4]张铮,贺洪斌,辛鹏来.随钻声波测井仪控制采集电路的优化设计与实现[J].声学技术,2016,35(2):180-187.

[5]康梓义,张伟.随钻声波测井仪井下信号采集处理电路设计[J].电子质量,2014(9):59-64,69.

[6]肖习鹏,师奕兵,张伟,等.随钻声波测井仪数据采集电路设计[J].中国测试,2012,38(1):74-77.

[7]林聪,师奕兵,张伟,等.随钻声波测井仪井下信号采集与处理系统设计[J].测井技术,2012,31(3):19-22.

[8]王莹.多极子阵列声波测井仪多通道采集系统[J].测井技术,2013,37(3):302-305.

[9]刘西恩,张伟,马东,等.三维声波测井仪近探头高精度信号采集阵列设计[J].电子质量,2016(12):25-31.

[10]王育博.三维声波测井仪近探头采集模块设计[D].成都:电子科技大学,2016.

[11] ZUMBAHLEN H. Linear circuit design handbook[EB/OL]. (2008-04-12)[2018-03-19].http:www.analog.com/en/education/ education-library/linear-circuit-design-handbook.

[12] JUNG W. Op amp applications handbook[EB/OL]. (2005-05- 22)[2018-03-19]. http: www. analog. com/en/education/educa- tion-library/op-amp-applications-handbook.

[13]賽尔吉欧.弗朗哥.基于运算放大器和模拟集成电路的电路设计[M].荣攻,译.3版.西安:西安交通大学出版社,2009,11-17.

(编辑:商丹丹)