基于千兆以太网高速数据记录器传输接口IP核设计

2019-11-05甄国涌焦新泉储成群

甄国涌,王 琦,焦新泉,储成群

(中北大学,仪器科学与动态测试教育部重点实验室,山西太原 030051)

0 引言

在工业领域中数据的采集记录不可或缺,其中记录器通过实时监测的功能来确定数据的准确性,实时监测即将A/D数据通过以太网传输至上位机,通过上位机进行实时监测以监测数据的准确性,从而确定被测物体的性能。

以太网的传输方式简单,传输速度快[1]。为了满足人类的生产生活需求,在几十年间以太网传输速率已经达到万兆甚至十几万兆[2]。目前,工业领域内百兆以太网技术已经成熟,但是其传输速度却无法满足工业需求,为了保证运行速度以及减少成本,千兆以太网成为工业主流[3-4]。针对以太网MAC层的接口设计共有2种方式,一种是将PHY层与MAC层集中在一个芯片中,直接使用芯片进行数据通信,这种方式对于百兆网及百兆速度之下的以太网较为普及,例如W5300芯片;另一种方式就是对MAC层进行程序设计,通过程序控制接口通信。本文选用第二种方式,将千兆以太网接口通信模块封装为IP核的形式,完成千兆以太网数据通信[5]。

1 总体设计

本文设计的千兆以太网数据传输以UDP/IP协议为基础,实现数据通信。图1为程序总体构架图。

图1 程序总体设计构架图

上位机通过物理芯片向接口发送COMMAND DATA,即命令数据,通过整合模块控制下位机进行“动作”。当整合模块发送使能预控制信号时,通知UDP/IP协议栈进行发送准备,当MAC控制器发送使能控制命令后,UDP/IP协议栈将报头信息经由整合模块发送至MAC控制器最终发送至上位机,当报头发送完成后立即对数据模块进行使能控制,控制数据模块发送相对应的数据。其中UDP/IP协议栈、整合模块以及MAC控制器组成了通信控制IP核。为了简化后期工作量,采用“分-总-分-总”设计思想,首先分块对每一模块进行设计,之后各自封装成IP核,作为一个小的整体,最后再将每个小整体作为大整体的一部分进行IP核的封装。

2 UDP/IP协议栈可配置IP核设计

2.1 UDP协议栈内容

UDP/IP协议栈主要作用是对数据进行封包处理[6],在UDP/IP协议栈中,为了实现可配置方案,将UDP/IP协议内容进行分类:一种是需用户在程序自行配置,例如IP地址、MAC地址等,另一种类型是内部计算配置,如IP校验和等[7]。通过对这2种类型进行不同方式的配置,实现UDP/IP协议栈模块可配置功能。使用“generic”语句对此模块中可配置参数进行统一标注,方便用户根据需求进行相关配置,实现IP核可配置;针对内部计算配置,可以分为2种类型,一类是通过命令判断其配置参数进行参数输入,例如数据报总长度的配置,另一类是通过FPGA进行校验计算后,进行配置,例如IP校验和的配置;对于数据报长度的配置,需要在FPGA内部进行,上位机发送命令后,FPGA通过命令语句判断回令类型,同时确定回令长度,将其发送至此模块,进行数据报长度配置;校验和的配置需要对相关内容进行计算之后回传UDP/IP协议栈,如表1所示,为协议栈配置类型及方式。

表1 协议栈配置类型方式

2.2 UDP/IP协议栈IP核结构设计

UDP/IP模块主要作为数据与MAC层的中间联系层,在数据发送时对其进行打包。因此它接收命令使能进行UDP/IP内容发送,同时给数据模块发送使能,通知数据模块发送相应的信息。图2为UDP/IP协议栈可配置IP核结构图,其中图2(a)为此模块的节点图。信号Reconfiguration,Read_udp_en以及Data_length[15:0]由上位机发送命令后,FPGA对命令进行解析,输入至此模块,启动协议栈模块,Reconfiguration信号为配置信号,上电首先将用户配置数据写入;Configuration_flag信号为配置完成标志信号,Read_udp_finish信号为封包内容发送完成标志,同时也是数据模块使能信号。

(a)UDP/IP协议栈可配置IP核节点图

(b)UDP/IP协议栈可配置IP核内部结构图图2 UDP/IP协议栈可配置IP核结构图

图2(b)为此IP核内部结构图,控制模块主要用来控制参数的写入,Dual_ram采用双口RAM存放协议内容[8],IP校验和模块计算校验和后,将结果通过控制模块写入RAM中相应位置。其中校验和模快涉及到IP协议内容的计算,检测IP协议内容的正确性,提高数据传输可靠性。校验和计算主要分为3个步骤,首先将16位数据依次相加,之后对所得结果进行进位以及取反,其计算公式为

X0[16∶0]=X1[15∶0]+X2[15∶0]+X3[15∶0]+…

+XN[15∶0]

(1)

A[15∶0]=X0[15∶0]+X0[16]

(2)

B[15∶0]=0xffff-A[15∶0]

(3)

式中:A,B,X均为协议数据。

使用如图2所示方案对校验和进行计算,首先通过控制模块对数据进行处理,为了保证加法器输出数据不丢失,使用有符号加法进行计算,控制器将输入数据顺序组合为16位数据进行输入同时在最高位加入符号位,即输入X1,…,XN为17位数据,将第一次加法结果通过高位分离后,再次进行加法运算,得到A[1],最后通过减法器输出所得校验和结果B[15∶0][9]。

2.3 UDP/IP协议栈设计流程

图3为UDP/IP协议栈可配置IP核程序流程图,上电后判断Reconfiguration信号即配置使能是否为‘1’,若为‘1’则通过双口RAM中的A口进行基本参数写入,直到配置完成,将Configuration_flag置为‘1’,之后对Read_udp_en读使能进行判断,若有效则根据输入的Data_length信号,启动IP校验和模块进行校验和计算,并通过双口RAM中的B口进行数据长度以及校验和的参数写入,同时通过Dual_ram中的A口进行协议内容读取,将其输出至整合模块,数据读取完成后将Read_udp_finish信号置为‘1’,此信号同时作为数据模块的输入使能,控制数据的输入。在进行校验和参数配置时,首先对检验和使能进行判断,在IP校验和模块完成校验计算后,发送标志Check_flag至控制模块,控制模块在接收到标志有效时,才将数据通过Dual_ram的B口写入至RAM中的相应位置。

2.4 UDP/IP协议栈仿真结果

对此模块进行仿真分析,图4为此模块仿真结果图。图4(a)为配置部分仿真分析图,其配置操作在配置使能reconfiguration有效时,通过RAM的A口进行基本信息配置,当输入data_length信号时,通过B口进行长度及校验和的配置与计算。图4(b)为读模块数据仿真时序,在read_udp_en有效时,对RAM中的数据进行读操作,将配置信息顺序读出。

图3 UDP/IP协议栈可配置IP核程序流程图

3 整合模块IP核设计

整合模块在本设计中主要是作为UDP/IP协议栈IP核以及MAC控制器IP核的对接模块以及发布起始命令的一个中间对接模块,因此其主要作用是将上位机命令进行解析之后,进行命令发布。图5为此整合模块的节点示意图。整合模块通过实时“监控”的方式判断命令语句,根据命令使能MAC控制器;oe信号为选择信号,选择当前输出数据为协议报头或者是有效数据。Data_command信号主要作用在IP核外部数据模块上,目的是通知数据模块根据此命令指令准备相应的回令数据,保证数据发送正确。Data_en信号为数据模块使能信号,由信号Configuration_flag以及Read_udp_finish信号共同决定。

4 MAC控制器IP核设计

4.1 媒体独立接口的选择

以太网接口包括MII、GMII、RGMII等,主要用作MAC层与PHY层之间的通信接口[10-11],其中MII用于10M/100M以太网的数据通信,GMII与RGMII均可使用于千兆以太网的数据传输,但RGMII是GMII的简化版,使用RGMII作为接口时,可以节省资源。图6为3种媒体独立接口连接示意图。

(a)配置信息仿真图

(b)读模块仿真图图4 UDP/IP协议栈IP核仿真结果图

图5 整合模块IP核节点示意图

4.2 MAC控制器IP核结构

如表2所示,对3种接口进行比较,RGMII接口使用较少的数据传输线,节约了硬件电路资源,同时此接口采用双沿采样的形式对数据进行采样,对时钟资源进行了有效利用,因此在硬件电路设计中采用RGMII接口作为MAC与PHY的连接接口是一种较好的选择。

在程序设计中,XILINX公司针对千兆以太网MAC层接口芯片提供了对应的IP软核,本模块的设计主要是以此IP核为主,加入控制模块及IP核配置,最终将其封装为接口IP核,方便与其他模块对接。

(a)MII接口连接图

(b)GMII接口连接图

(c)RGMII接口连接图图6 3种独立媒体接口连接示意图

图7(a)为MAC控制器IP核节点示意图,图7(b)为此IP模块内部结构示意图。此模块包括配置模块、输入控制模块以及Tri Mode Ethernet MAC IP软核。电路板上电复位操作完成后,配置模块将配置数据写入接口IP核中,根据用户需求对其进行配置,read_rgmii_en为MAC接口IP核使能信号,当其有效时,启动MAC接口IP核,在MAC接口准备好后立即将信号read_udp_en置为有效,控制UDP/IP协议栈进行数据输出,最终通过接口IP核转换为4位数据发送至物理芯片。

表2 3种接口信号传输基本信息

(a)MAC控制器IP核节点示意图

(b)MAC控制器IP核内部结构示意图图7 MAC控制器IP核结构图

4.3 MAC控制器仿真结果

图8为MAC控制器模块仿真图。在read_udp_en有效时,同时对data_in[7∶0]赋值,将其赋值为自加数,rgmii_tx_ctl为数据发送控制位,当其为高时,rgmii_txd[3∶0]数据输出有效,其控制时钟为rgmii_txc,rgmii_txd[3∶0]在输出有效数据前会自动加入以太网前导码,根据RGMII接口特点,数据采样发生于时钟沿,因此一个时钟会进行2次数据采样,并且以太网数据传输采用小端模式。

5 仿真与结果

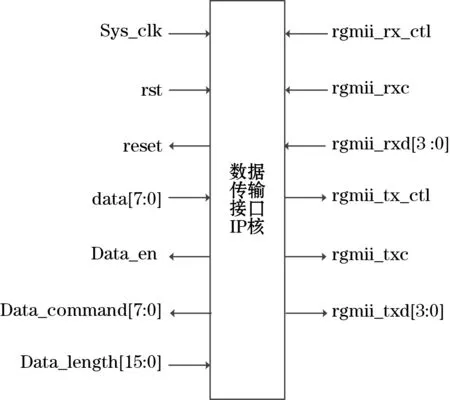

将上述3个IP核模块作为3个分模块,进行对接以及最终封装。以太网数据传输接口IP核如图9所示,其内部主要通过信号线将三大模块进行连接,同时加入时钟及复位模块,系统时钟为50 MHz时钟,但千兆以太网通信时钟为125 MHz,因此,需要对系统时钟进行倍频处理,PLL模块即为时钟模块;复位模块主要是用来对硬件芯片进行复位配置,所用物理芯片为88E1518,物理芯片使用时必须进行一段时间的复位,完成芯片自配置。

图8 MAC接口控制器IP核仿真图

(a)IP核内部结构示意图

(b)IP核节点示意图

对上述IP核进行最终硬件测试,通过上位机进行命令发送,同时下位机接收到命令后,发送自加数,最终结果通过wireshark以及udp通信软件进行验证,得到如图10所示的结果图。

(a)wireshark抓包结果图

(b)udp通讯软件结果图图10 接口IP核通信结果图

本文采用“分-总-分-总”的设计思想,将千兆以太网数据传输MAC层封装为IP核,并加入可配置UDP/IP协议栈,经测试,其速度可以达到950 bit/s,将其进行封装可以简化千兆以太网数据传输过程,在工程领域中可以直接使用,不再需要进行繁琐的程序处理,在实际工作中起着重要作用。