基于FPGA的高频低电平系统的研制与调试

2019-10-25王贤武马瑾颖

王贤武 马瑾颖

(1.西北师范大学 物理与电子工程学院,甘肃 兰州 730070;2.中国科学院近代物理研究所,甘肃 兰州 730000)

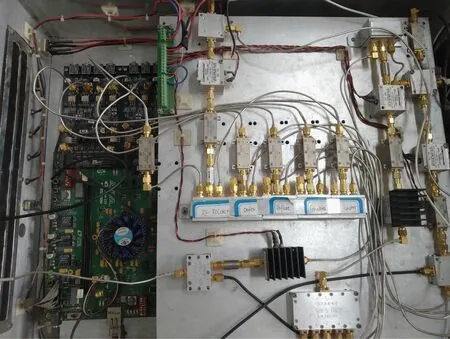

加速器驱动的次临界系统(ADS),是有效减少核电废料放射性的途径之一[1]。中国科学院近代物理研究所承担的ADS直线加速器的高频系统工作频率是162.5 MHz[2-4],低电平系统(LLRF)的目的是使超导腔体稳定工作在谐振状态,控制腔体腔压与场强。相比较于传统的模拟低电平系统,减少了模拟器件经过级联之后产生的误差与时延造成对系统控制性能的影响,将信号直接经过ADC数字离散化,转变为数字量,易于系统的调试与监控,提升束流的加速效率。本高频低电平系统主要由模拟和数字2个部分组成,分别完成对信号的上下变频与数据的处理工作。该高频低电平系统如图1所示,系统共分为上下两层,上层为射频前端,有4路输出高频信号与1路高频输出信号,下层为FPGA开发板、AD9858直接数字频率合成器与AD9510锁相环。系统的主要模拟器件是射频前端,因为ADC的采样速率有限,需要将高频信号降频,由速率为122.88 MS/s的ADC对腔体信号进行四倍频采样。之后信号送入FPGA,通过IQ解调、CORDIC鉴相等算法后将得到的腔体幅度和相位信息与参考信号和设定值比较,通过专门的PI控制器进行反馈控制,完成对超导腔腔压的幅度、相位的控制与调节。同时建立了高频腔体的PI控制传递函数模型并进行仿真。高频低电平系统在常温状态下工作,相位稳定度为±0.6°,幅度稳定度为±0.8%,成功控制腔体闭环调谐,达到了设计要求。

图1 高频低电平系统实物图

1 模拟前端

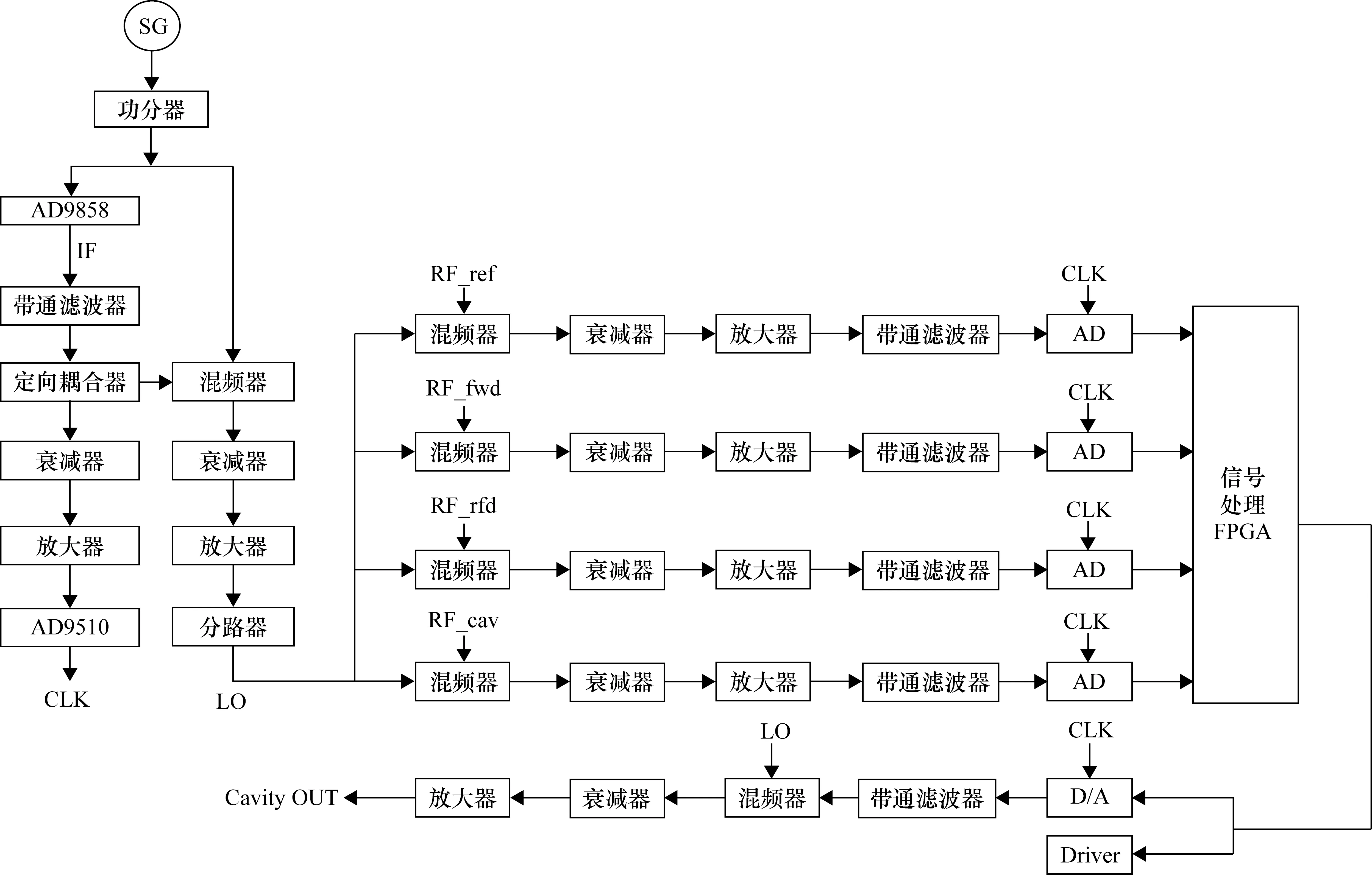

高频低电平系统的模拟前端如图2所示,数字DDS芯片AD9858产生系统所需的30.72 MHz的中频参考信号,将其与162.5 MHz的高频射频信号混频,经过衰减器、滤波器等生成131.78 MHz的本振参考信号,该信号通过5路分路器与其他4路射频信号混频,得到30.72 MHz的中频信号,从而将高频信号转化为中频信号,满足ADC与DAC的采样速率要求,其中模数转换与数模转换均为14-bit,转换速率分别为150 MS/s与165 MS/s。Mini-circuit放大器选用DC15 V供电,最大输出为25 dBm,为了使其能工作在线性区,输入最大设定为-4 dBm,Mini-circuit混频器在工作在输出波形不失真的前提下,本振信号大于17 dBm。系统时钟由AD9510锁相环将中频参考信号锁相之后获得,时钟频率为122.88 MHz。

2 高频低电平FPGA核心算法

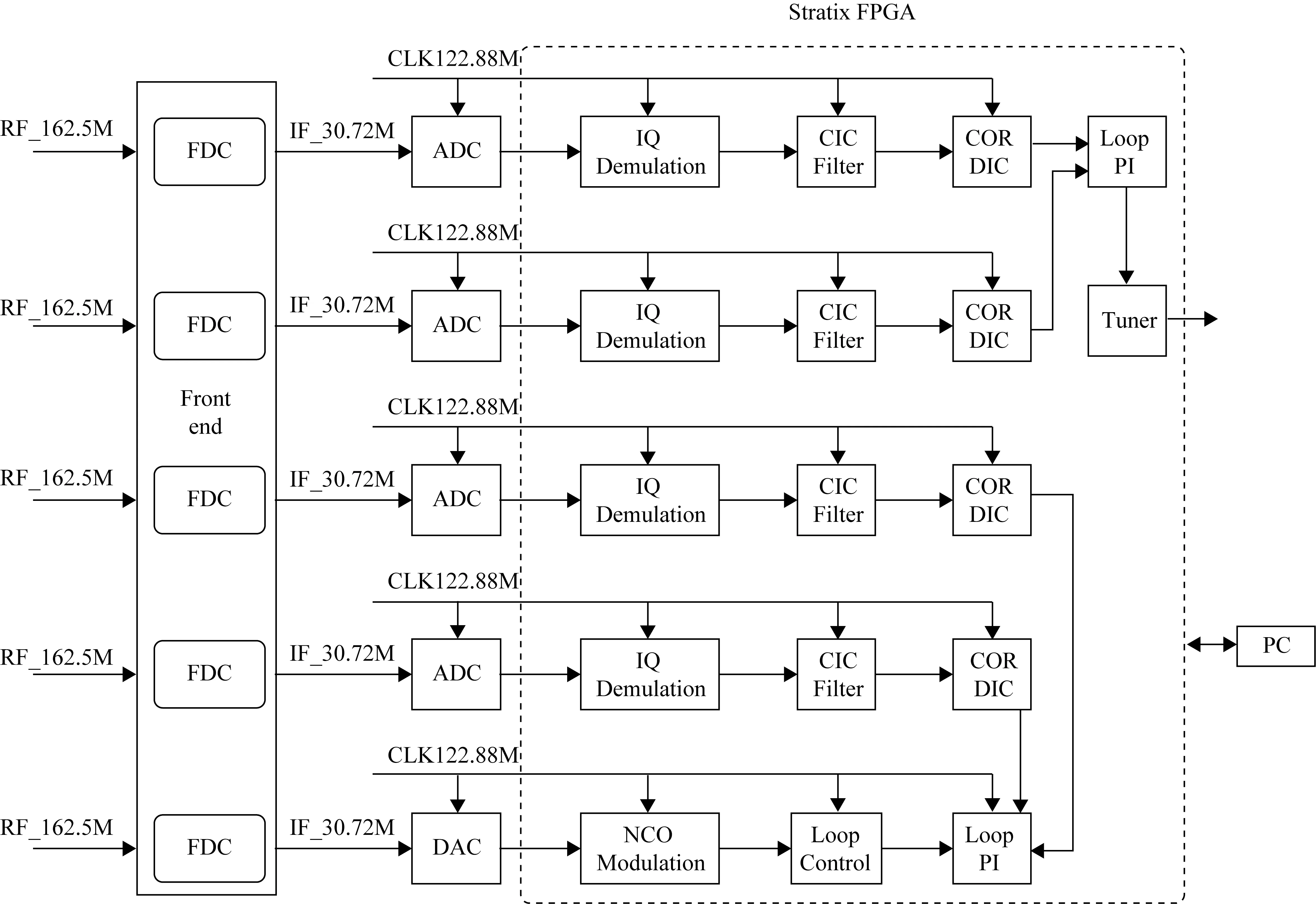

高频低电平系统的数字信号处理主要由FPGA完成,系统选用Altera的高速StratixIII EP3SL150F1152FPGA,系统需对腔体的入射信号、反射信号、腔压信号与参考信号进行四倍频采样,之后分别对这4路采样信号进行IQ解调、滤波、CORDIC旋转鉴相和比例积分控制等处理。将解调之后的入射信号和反射信号鉴相,求出相差,根据失谐角的大小,通过比例积分控制器产生腔体调谐电机所需要控制信号,对腔体失谐进行步进电机调谐控制。对腔压信号进行IQ解调,对解调之后的腔体电压信号的幅值与相位信息分别与参考值和设定值进行比较,经过PI控制,产生腔体所需要的相位与幅值调制信号,该信号经过调制、上变频之后产生腔体的高频输出信号。FPGA信号处理过程如图3所示。

图2 高频低电平系统射频前端

图3 FPGA信号处理过程

2.1 IQ正交解调

IQ正交解调也称IQ正交基带变换[6]。I和Q分别是腔体取样信号在实域与虚域的两个相差2/π的分量,在将高频信号下变频到中频之后,ADC将其进行采样:

(1)

式中,fs为ADC采样频率;fIF为中频信号频率;n为任意整数。根据奈奎斯特采样定理,如果以不低于信号最高频率2倍的采样速率对带限信号进行采样,那么根据所得到的离散采样值就能准确地确定原信号[7]。再考虑到ADC采样性能限制,令n=0对中频信号进行四倍频采样。采样之后的离散信号为

s(n)=Asin(2πfIFnT+φ)

(2)

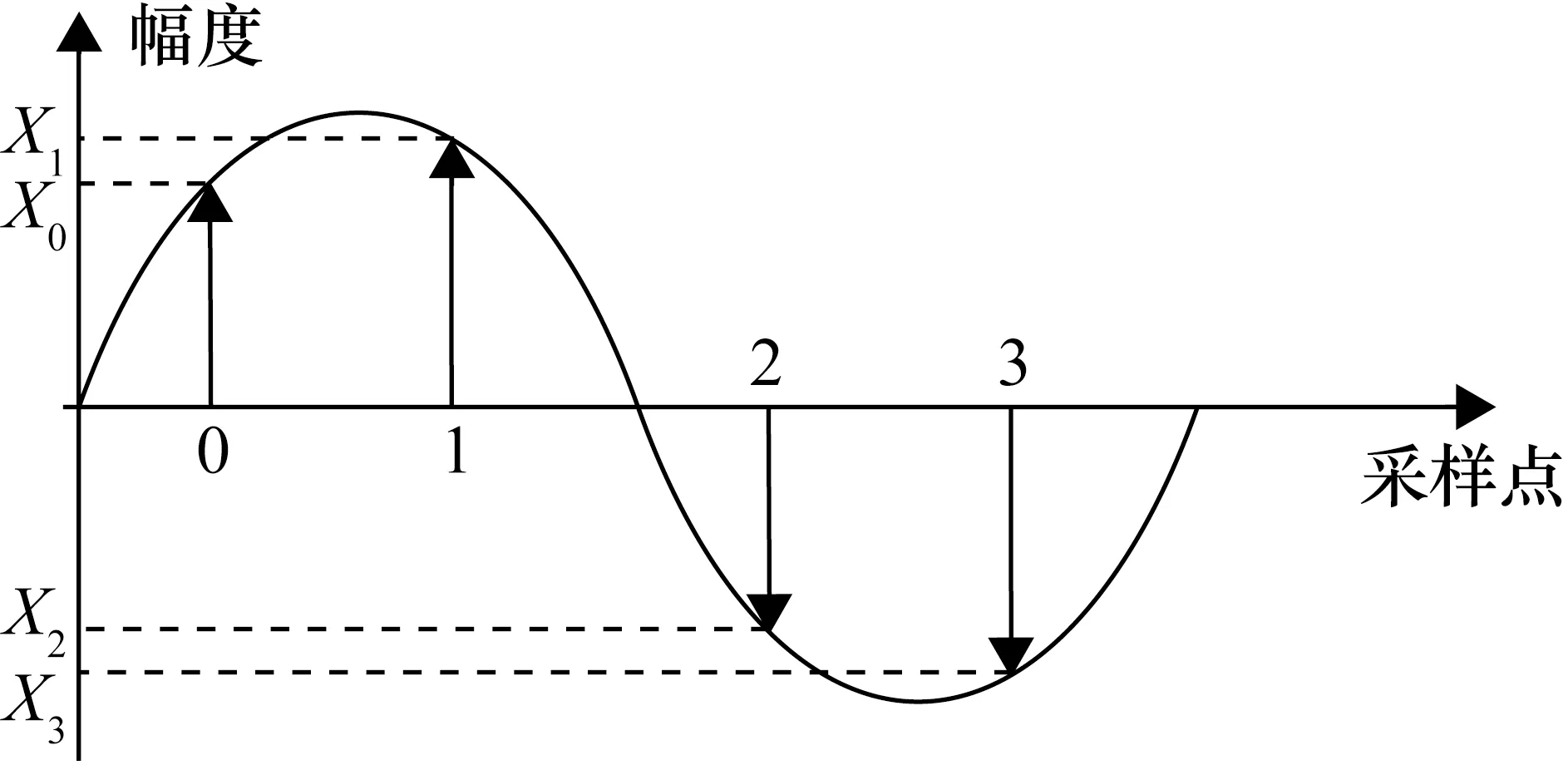

中频信号的IQ四倍频正交采样序列如图4所示。

图4 中频信号的IQ四倍频正交采样

获得离散的正交采样序列之后,可以求出I、Q的值分别为

(3)

(4)

其中,I、Q值与腔体取样信号的对应关系如下:

(5)

(6)

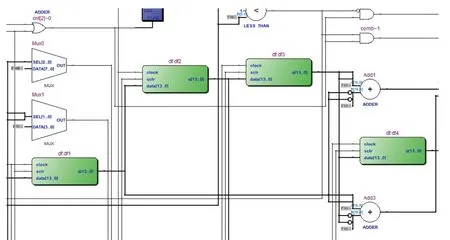

式中,A与φ分别为腔体取样信号的实时幅值与相位信息。因为ADC采样信号的周期为4,因此可以在FPGA中使用4个D触发器数据信号进行锁存。如图5所示,首个D触发器df1输入端与ADC离散信号输出端级联,之后的D触发器df1的输入端与上一个D触发器的df2输出端级联,以此类推,从而在4个时钟周期的延时之后完成4组数据的循环迭代,只需要利用少数的FPGA逻辑资源便可以完成离散信号的IQ正交解调。

2.2 CORDIC鉴相

在低电平系统中,使用坐标旋转数字计算方法(CORDIC)来获得超导腔体相位与幅值的实时数据。如果直接用FPGA硬件逻辑电路进行乘法除法运算来得出高频腔体的幅度与相位的实时数据,会消耗过多的FPGA逻辑电路资源,同时也会降低系统信号的运算处理速度。因此选用非循环流水线结构的CORDIC算法,通过基数角度多次迭代旋转,最终达到误差允许范围,逼近所需的角度,该算法的每一次迭代都通过移位和求和运算来完成[8]。其中每次旋转所遵循的旋转公式为

图5 IQ正交解调模块RTL视图

(7)

式中,i为迭代次数;θ为每一次迭代的角度大小。i的值每一次增加都是改变θ的累加值,在达到所需精度要求之后迭代完成,最终的角度和便是所求相位角:

p(i+1)=p(i)+diθ(i)

(8)

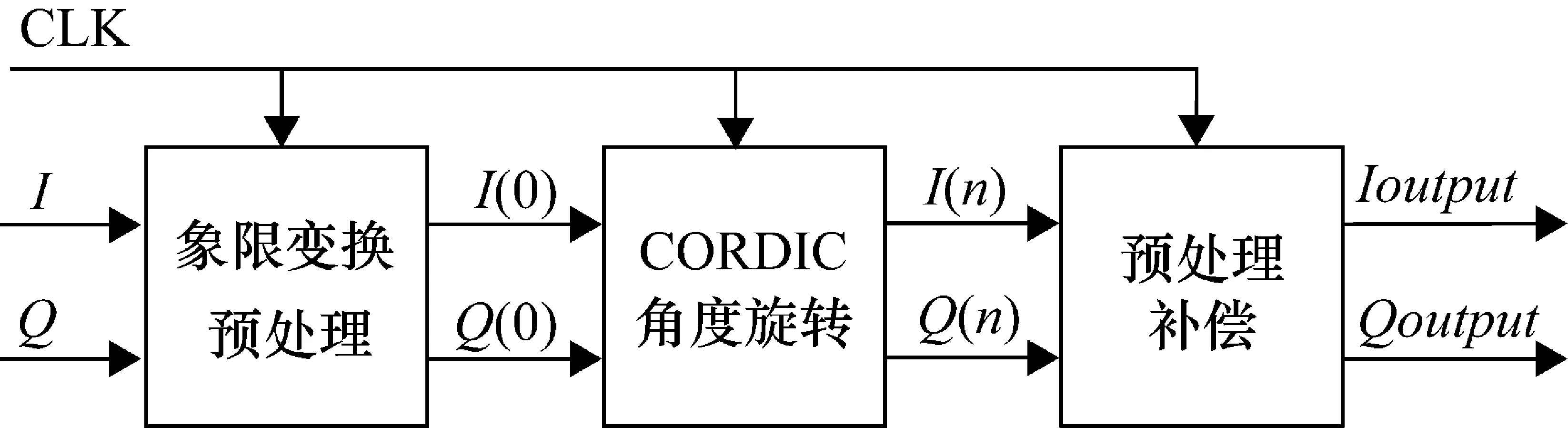

式中,di=±1,用于判断每一次迭代旋转的方向。CORDIC通过FPGA可极大提升运算速度与效率。该算法主要分为预处理、角度旋转、预处理补偿3个模块,如图6所示。

图6 CORDIC数字鉴相模块

为了提升鉴相的精度,减少迭代次数过多而造成的误差,中频信号首先经过预处理模块,将其变化到π/4象限内,之后对变换过的I/Q之进行21位角度旋转鉴相,之后对预处理工作进行幅度补偿与相位的还原。经过16个时钟周期的迭代即可完成一次相位与幅度迭代。

3 反馈控制器的设计与仿真

3.1 腔体模型建立与分析

系统采用反馈控制,需要将腔体的腔压取样信号与参考值和设定值对比,对高频腔体进行PID控制。高频电磁谐振腔的幅频响应、相频响应特性与RLC谐振电路类似[9]。设高频腔体的腔压为V,等效电流为I,其等效RLC电路模型如图7所示。

图7中,L为腔体的等效电感;C为腔体的等效电容;R为高频腔体阻抗;r为传输线特性阻抗。设腔体固有频率为ω0,有载品质因数为QL,那么高频腔体的LCR模型的微分方程为

(9)

设腔体固有频率为ω0,有载品质因数为QL,RL=R+r为系统的有载阻抗。那么微分方程可表示为

(10)

该电路的等效阻抗为

(11)

对式(10)进行拉普拉斯变换变换到频域中,腔体的传递函数为

(12)

设外部激励信号为I(s),系统响应为

V(s)=ZL(s+iω)·I(s)

(13)

此时的传递函数为

(14)

因为I信号与Q信号一直处于正交状态,Δω=0,设ω1/2=ω0/2QL为腔体的半带宽,IQ信号的传递函数为

(15)

由式(15)可知,传递函数简化为了一阶函数,腔体模型等同于一阶低通滤波器,可以由PID控制器进行比例积分控制。经典的PI控制器传递函数为

(16)

因此在加入PI控制器之后,需要考虑控制器的时延与数字信号处理部分的硬件时延,所以在传递函数模型中还要加入整个系统时延e-τs,那么腔体的传递函数为

(17)

为了获得更好的控制效果,缩短调节时间,令ki=ω1/2,此时式中分子分母抵消一项,传递函数变为

(18)

此时传递函数的零点被抵消,系统在临界稳定时,在测试铜腔条件下需要满足kp<π/2τω≈13,可知在使控制器更为简单的前提下,系统传递函数无零点,此时kp增益的极限在13左右。

3.2 验证与仿真

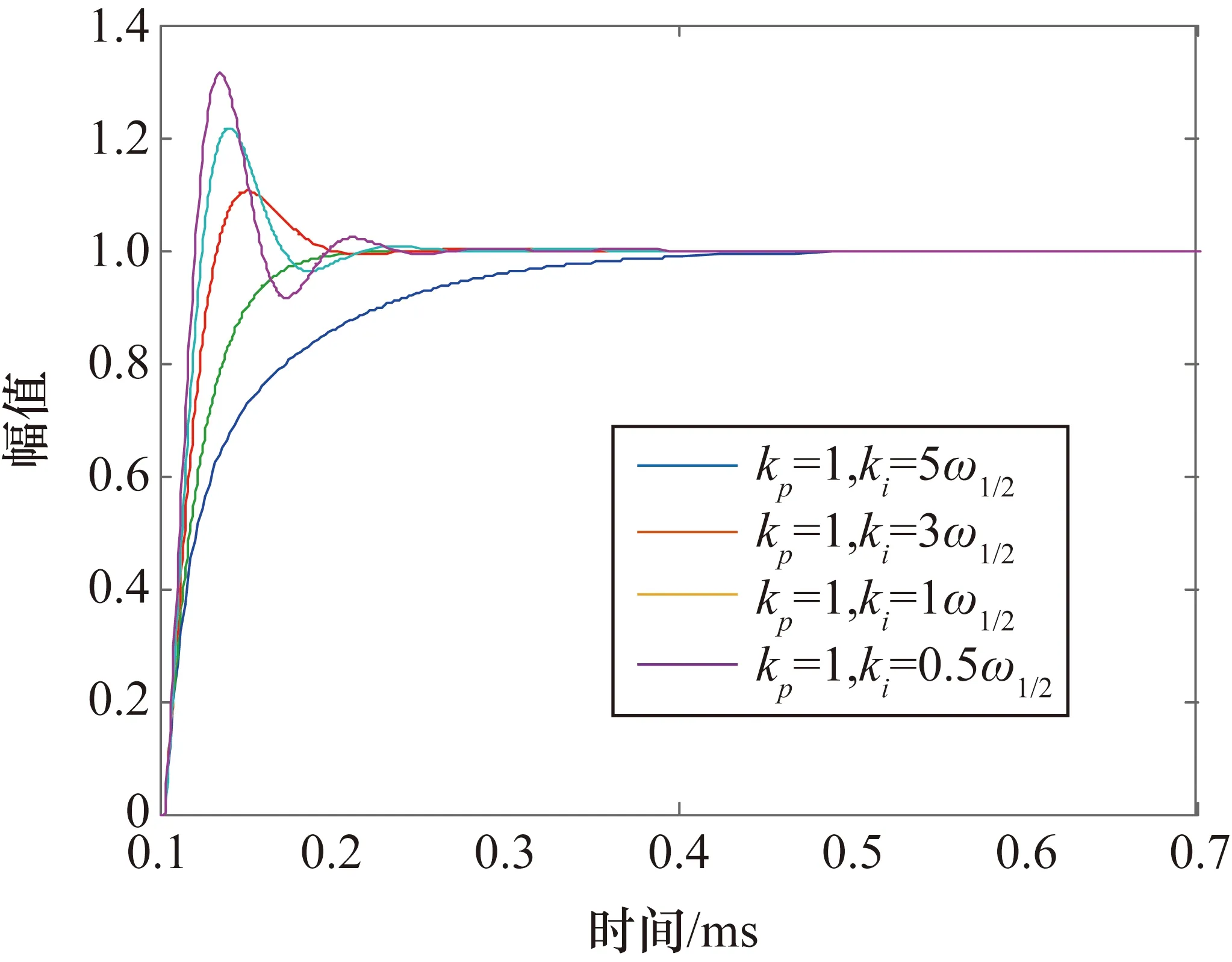

在Matlab中,分别控制系统的kp与ki两个参数。通过系统的阶跃响应曲线随参数的变化验证之前对参数的推断,并且考虑了系统延时,补偿了在实际工作中其对调谐的影响,对PI控制器中PI参数的选取范围做出大致判断,为之后的调谐提供依据。仿真效果如图8、图9所示。

图8 ki系统阶跃响应

图8中kp=1,在ki>ω1/2时,曲线波动幅度较大,系统不稳定且处在欠阻尼状态;ki<ω1/2时,系统需要很长时间才能达到稳定,处于过阻尼状态;ki=ω1/2时,在保证系统上升时间的前提下,没有产生较大过冲,调整时间较短,系统较为稳定。

图9中ki=ω1/2,在kp=3左右,系统的阶跃响应曲线较为理想;在kp≥10时,系统阶跃响应的曲线波动会比较大,长时间处于欠阻尼状态。可以在适当范围内继续调整kp的值,以减少系统的上升时间,提高系统稳定性。在加入延时之后,根据仿真结果可以推断出PI控制器的参数调整范围大致在ki=ω1/2,kp=3~4.5,同时需要在今后的工作中根据腔体的具体情况,如现场的噪声、硬件的非线性失真与不同系统的延时进行调整。

4 系统稳定性测试与结论

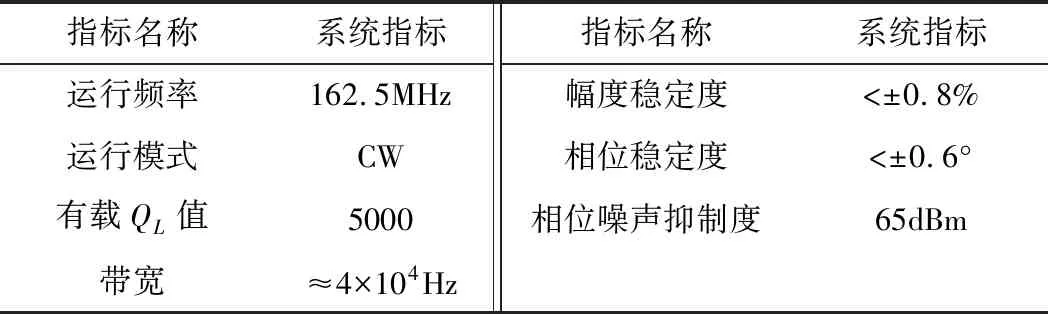

系统选用常温铜腔体对系统进行测试。系统参数如表1所示。

表1 系统参数

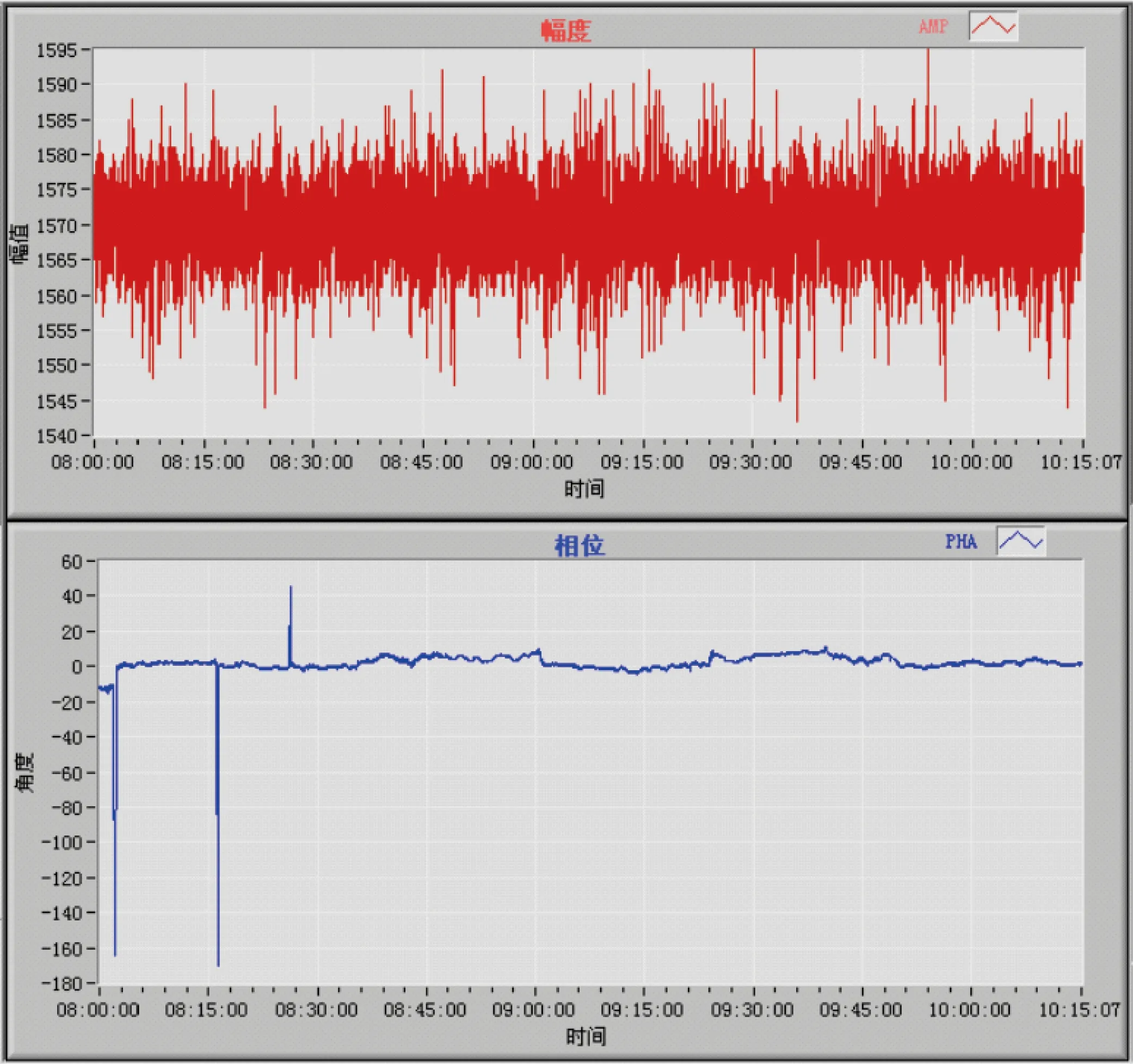

连续2 h 15 min稳定性测试中,高频腔体的幅度设定值为1570,相位设定值为0。在开环状态下,启动调谐电机,初始情况失谐量较大,进行电极粗调谐,在将相位与幅度锁定在设定值附近,开启腔体幅度与相位环路的自动调谐,使腔体保持谐振状态。记录闭环状态中的频率误差,如图10所示, 分别为高频腔体的幅度误差与相位误差。在测试过程中,腔体的幅值一直稳定在设定值范围内,在8:02、8:16和8:25分左右,腔体因氦压波动造成闪断,系统自动开环,需要手动加载腔压,将幅值与相位调整到闭环参考值内系统重新闭环。之后低电平系统可以快速将其相位拉回到设定值范围内,恢复谐振状态,使腔体在之后一直工作在谐振状态。

图10 幅度相位稳定度

经过2 h的测试,在闭环过程中,LLRF系统能保持幅度和相位稳定,幅度稳定为±0.8%,相位稳定度为±0.6°。系统对高频信号下变频为30.72 MHz的中频信号进行采样,之后用FPGA作为数字信号处理模块对信号进行实时分析与调整,并建立了相应的高频腔体传递函数模型,提高了超导腔体调谐的精度与稳定度,达到了预期的设计要求。今后将继续对系统的FPGA算法、系统参数和射频前端硬件进行优化,在不同的腔体中进行调试,以应对高Q值腔体所引起的带宽减少,测试得到最优的系统参数,减少系统时钟抖动对系统的影响,提升调谐的控制精度与调谐器反应速度。