基于FPGA 的弱电网下并网逆变器控制器研究

2019-10-19赵鑫陈国初张子骞朱志权

赵鑫,陈国初,张子骞,朱志权

(1.上海电机学院电气学院,上海201306;2.格拉茨技术大学电力系统研究所,奥地利格拉茨;3.上海电气风电集团,上海200241)

0 引言

近年来,由于化石能源等不可再生资源的短缺,风能、太阳能等可再生能源得到了越来越广泛的应用。但这些可再生能源分布广泛,无法集中利用发电,因此对分布式发电技术的研究就显得愈发重要。

目前,由于越来越多的电力电子器件应用于电网当中,较多的非线性负载带来了电网谐波污染的问题。分布式能源之间距离远、地址位置偏,因此在电能传输的过程中,传输线路的距离增长,变压装置较多,使得在并网逆变器以及电网之间的阻抗较大。此时,电网呈现弱电网特性[1]。

在并网逆变器控制器中,锁相环(PLL)是目前使用最普遍的相位同步方法,它能够捕获实时的相位信息,在电压畸变以及三相不平衡条件下,能够准确、快速地锁定电压相位,因此其性能对于整个控制系统至关重要。锁相环(PLL)的结构可以分为3 种类型:基于过零点检测的锁相环,结构简单,且无法准确跟踪电压相位;基于静止坐标系的锁相环以及基于同步旋转坐标系的锁相环不能在电网不平衡时具备良好的性能。如何在弱电网条件下保证锁相环的良好性能十分必要。文献[7]分析了锁相环在输出导纳矩阵中的影响,表明锁相环可能带来低阶谐波震荡,说明了锁相环在逆变器并网过程中会带来较大的影响;文献[8]采用在三相同步锁相环(SRF-PLL)添加移动平均滤波器实现了获取精确的相位信息的功能,但是这种方式不适用于弱电网条件下,逆变器控制器在电网故障条件下的控制准确度不高;文献[13]采用了一种双二阶广义积分器的锁相环(Dual Second- Order Generalized Integrator-PLL,DSOGI-PLL)算法,实现在电网不平衡、含有谐波或电压畸变情况下的准确锁相,但这种锁相环建模比较复杂。

本文提出使用采用三相同步锁相环对逆变器的控制器进行设计,并在FPGA 中进行建模,使得控制器精度较大提高,能够实现弱电网比较容易受到扰动的情况下,对电网电压的精准锁相,提高了并网逆变器控制器的准确性以及快速性,完成CHIL 仿真实验验证了设计的正确性及可行性。

1 并网逆变器控制器研究

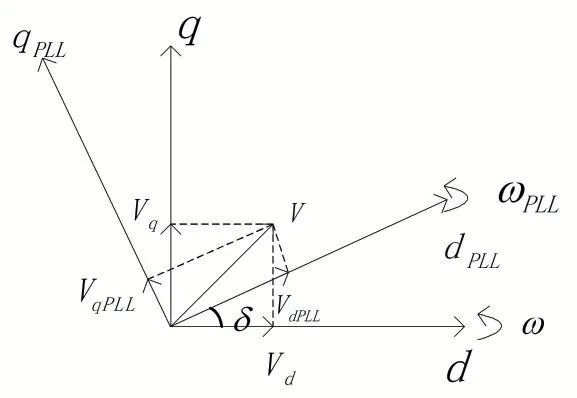

如图1 所示为PLL 下的dq 变换向量图,PLL 影响下的dq 变换使系统产生δ 的相移,电网系统的相角为θg,PLL 的相角为θPLL,而δ=θg-θPLL,可见影响逆变器稳定性的有电网和PLL 两个因素,而电网相角θg为固定值,所以我们应该对θPLL进行研究。

图1 PLL下的dq变换向量图

逆变器与无限大母线相连,取三相电流i 与三相电压U 进行dq 变换,Uq进行锁相环控制,经PI 控制器、积分取余之后得到电网与逆变器的相角差θ,将相角差θ 反馈给三相电压电流进行Park 变换与逆Park 变换,Park 变换得到的id、iq经PI 积分器之后进行解耦,得到进行反dq 变换得到新的三相abc 电压,实现了逆变器控制器对电网电压的锁相控制。如图2 所示为三相同步锁相环(SRF-PLL)的控制原理框图。

图2 并网逆变器及控制拓扑结构图

其中,派克变换部分的数学表达式为:

SRF-PLL 是最常见的一种锁相环,其原理为三相电压(电流)经过Park 变换之后,将q 轴变量经PI 之后经积分环节产生相角Δθ,将其反馈给dq 变换,形成闭环结构。图3 为并网逆变器控制原理框图。

2 基于FPGA的逆变器控制器实现

如图4 所示为FPGA 中逆变器控制器设计框图,Uabc、Iabc为从dSPACE 接收的三相电网电压以及由逆变器产生的电流,经ADC 数据采集卡接收电压电流数据,由于dSPACE 发送的数据为0-5V,在ADC 采集数据之后需要进行数值的变换,经数值上浮之后变换为电压为-400-400V,电流变换为-25-25V。数值变换后的电压电流经dq 变换,三相电压变换后得到Uq=0,将Uq经PI 控制器之后积分得到电网电压相角,与2 π 进行比较之后得到相角差ωt(0-2 π)并反馈给三相电压与三相电流进行dq 变换,实现锁相控制。

将三相电流dq 变换之后得到的Id、Iq经PI 控制器,Udc为直流母线电压,对Udc进行数值变换,进行限幅,经PI 控制器得到直轴电流给定值Idref,实现了直流母线与控制器之间的双向控制。将三相电流经dq 变换之后的Id、Iq与Id、Iq经PI 控制器得到的UPI-d-out、UPI-q-out进行解耦控制。

GFF 为电压前馈模块,将解耦后的Ud、Uq与三相电压进行dq 变换之后得到的Ud、Uq进行电压前馈,实现电压前馈控制,并对电压环控制所得到的新的Ud、Uq进行限幅。将得到的新的Ud、Uq进行逆dq 变换,得到新的Uabc与Udc生成带死区的PWM 波,并反馈给dSPACE。

图3 并网逆变器控制原理框图

图4 FPGA中逆变器控制器设计框图

3 基于CHIL的并网逆变器控制的实现

如图5 所示为控制器硬件在环(CHIL)的整体实验框架,FPGA 中主要完成逆变器控制器的模型搭建,设置整个模型运行在10KHz 下。dSPACE 中主要完成逆变器模型的搭建,其中逆变器模型是基于Simulink 搭建的,设置此模型运行在20KHz 下。

dSPACE 经D/A 传输三相电压以及三相电流给FPGA 的A/D,FPGA 接收到dSPACE 的电压电流信号之后,进行dq、PLL、PI、逆dq 等,经FPGA 的输出引脚输出三相PWM 至dSPACE 的I/O 接口,经过FPGA 的输出引脚时需要进行数值转换、数字大小变换等,使得三相PWM 信号能够完整地传递到dSPACE。

图5 CHIL实验整体框架图

dSPACE 接收FPGA9607 发出的PWM 波,然后转换成占空比对逆变器模型进行控制,然后采集电网电压U 及电流I 通过D/A 转换传送给FPGA9607,由于dSPACE 的D/A 输出接口具有输出范围限制,因此在采集电网电压U 及电流I 之后需要对其波形进行抬高及缩小幅值处理,使其幅值在D/A 口输出范围内。

通过Simulink 搭建了逆变器模型、电网模型、逆变器控制器模型,由于dSPACE 可以与Simulink 实现互通,因此将Simulink 直接导入dSPACE controldesk 中即可,其中逆变器模型通过由FPGA9607 输入的PWM 波进行控制。设置电网中的电阻阻抗较小,可以模拟弱电网情况下的逆变器并网环境。

4 实验结果

如图6 为CHIL 实验搭建平台,包括dSPACE 构建的仿真器,NI9607 构建的控制器。在现实情况中电网一直处于运行状态,而逆变器处于准备并网状态,因此在实验时dSPACE 空跑,FPGA 中逆变器控制器模型处于RESET 状态。之后逆变器并网,逆变器控制器开始工作,控制器接收到dSPACE 传递的三相电压、电流,打开PLL 的RESET,使dq 变换抓住电压相位,打开PI的RESET,对PI 进行软启动,进行三相电流的dq、反dq 变换,逆变器控制器对逆变器的桥臂开关进行控制得到pwm 波形,反馈给dSPACE,对逆变器进行控制。

图6 CHIL实验实物图

如图7、图8、图9 所示为CHIL 实验模拟电网平衡与电网不平衡条件下的实验结果图,黄色为dSPACE发送的Ua 波形,绿色为输出一相SPWM 波形,蓝色为dSPACE 经FPGA 给定之后输出的Ia 波形,可见两个正弦波形的相移几乎为零,达到了利用FPGA 快速精确控制的目的。

图7 模拟电网正常情况下实验结果图(1)

图8 模拟电网正常情况下实验结果图(2)

图9 模拟电网不平衡条件下的实验结果图

5 结语

从实验结果可以看出,本文设计的基于NI9607 的FPGA 核心板设计的逆变器控制器能够很好地对弱电网情况下并网逆变器进行控制,在电网正常条件下,可以实现较好的锁相控制;在电网发生低电压穿越时,设计的逆变器控制器能够实现稳定的控制,并能够较快速地恢复运行。因此设计的逆变器控制器能够在弱电网条件下,在电网的正常以及故障条件下实现快速、稳定、精确地控制。