基于FPGA 和DDR3 的图像采集系统设计及实现

2019-10-09杨朋飞

杨朋飞,聂 亮

(西安工业大学 光电工程学院,西安710021)

图像信息在人类生产生活所能获取到的信息中占比很大,能实时、非接触式地获取高保真性的图像信息对国土安全、民用电子领域具有深远的影响[1-3]。 现今,随着基础器件工艺提升和高集成度芯片内部架构更新迭代,具有并行处理能力的单片现场可编程门阵列FPGA 芯片可兼具其他处理器很多重要功能。 目前已有的图像采集系统基本能实现目标显像,但也存在图像数据存取速度低、系统耗费资源大、体积较大、系统内部逻辑或控制算法复杂度高、设计系统外部接口通用性较低等不足方面[4-7]。为使系统小型化和图像数据高速存取,方便灵活地实现对目标实时显像,本文设计了一种基于FPGA和DDR 存储的相机图像采集系统, 旨在提供一种高速、大容量存储的实时图像采集方案,为后续有关工作提供理论和技术基础。

1 工作原理和系统结构

类似“人眼”观测视场范围之内景物,图像采集系统同样需要借助相机这一器件来完成目标物清晰、准确地成像在光电成像探测器像敏面,图像信息转换为电信息这种过程。 为将电信息所承载的图像信息准确地解析呈现出来,处理单元的设计极其重要。 系统采用通信总线类似IIC,具有SCCB 接口的相机模组,其成像探测器为OmniVision 公司研发的CMOS OV7670 图像传感器[8]。 文中以单片Xilinx Spartan6 XC6SLX16 型FPGA 为核心,充分利用ISE 开发环境提供的内部时钟核(clock)、ROM 核和DDR 核等丰富资源,实现相机寄存器配置、相机输出数据格式转换、DDR 读写控制以及VGA 显示等模块逻辑设计。 针对系统640×480 图像分辨率,30帧/s 的视频流,其数据量为

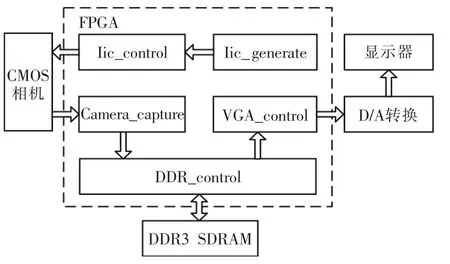

采用Micron 公司DDR3 SDRAM 芯片MT41J 128M16JT 对采集到的图像数据进行存储[9],DDR3工作效率是DDR2 的两倍[10],其容量为2 Gb,读写速度可达800 Mb/s。 在实际设计过程中将DDR3 读写速度保持在625 Mb/s, 以期与25 MHz 系统外部时钟产生倍频关系。 系统进行RGB565 彩色显示时,需经D/A 转换电路将FPGA 输出的数字图像信号转换为模拟图像信号, 进而经由VGA 接口将目标显示在终端显示器。 图1 为系统整体结构框架。

图1 系统整体原理架构图Fig.1 Structure diagram of system overall principle

2 FPGA 中各单元逻辑设计

2.1 Iic_control 模块设计及仿真测试

Iic_control 单元实现标准IIC 时序输出,用于对CMOS 相机进行配置。OV7670 模组与FPGA 以兼容IIC 总线进行信息交互,极大地降低开发周期和开发成本。 标准IIC 具有时钟线SCL 和数据线SDA,时序采用传输速率为100 k bit/s 的标准模式。文中对相机进行配置过程中, 考虑到FPGA 内部逻辑代码精简和整个系统功耗等问题, 仅使用到IIC协议的写操作命令, 即主机 (Master)FPGA 和从机(Slave)CMOS 相机进行通信。写操作包括下列过程:①Master 发起START 启动信号;②Master 发送具有IIC 接口的器件地址addr(7 bit)和写操作0(1 bit),等待ACK 信号;③Slave 发送ACK 信号;④Master发送寄存器地址addr(8 bit),等待ACK 信号;⑤Slave发送ACK 信号;⑥Master 发送数据data(8 bit),即要写入寄存器中的数据,等待ACK 信号;⑦Slave 发送ACK 信号; ⑧第6 步和第7 步可以重复多次,即顺序写多个寄存器;⑨Master 发起STOP 停止信号。经Modelsim 软件对Iic_control 模块进行仿真,如图2 所示。测试结果表明,IIC 协议逻辑正确,能正常稳定工作。 Iic_control 模块中的SDA 数据线传输的相机寄存器地址和数据是由Iic_generate 模块产生。 不仅如此,Iic_control 模块也输出相机配置使能信号(tiic_en,高电平有效)、相机配置完成标志位(tiic_init_done,高电平有效)、相机复位信号(image_sensor_reset_n,低电平有效)和相机低功耗使能信号(image_sensor_pwdn,高电平有效)。 CMOS OV7670 相机202 个寄存器地址和数据存放在ROM中,通过调用ISE 软件IP 核可具体实现。 相机寄存器进行配置之前,需对相机进行初始化。 图3 为Iic_generate 模块输出相机初始化信号的状态图。

图2 Iic_control 模块信号仿真图Fig.2 Signals simulation diagram of Iic_control module

图3 相机初始化状态转移图Fig.3 State transition diagram of camera initializes

2.2 Camera_capture 模块设计和数据转换

Camera_capture 模块实现将CMOS 相机模组输出的8 bit 数据转换为64 bit 数据。 在OV7670 输出格式为RGB565 的情况下,一个像素为2 Byte。 表1为Camera_capture 模块部分信号说明。 针对模块输入8 bit 数据,将其转化为64 bit 输出数据,实现方法如下:

在camera_vsync 信号为低电平,camera_href 为高电平的状态下,检测计数器counter 的当前值。 若counter<7(counter 从0 开始计数),则将获取到的相机数据存储在64 位寄存器camera_data_reg 中;若counter=7,即获取到第8 个字节数据时,则将采集到的相机数据存储在64 位寄存器ddr_data_camera中,并在同步时钟作用下,将ddr_data_camera 数据非阻塞输入DDR_control 模块。 采用Verilog 语言进行描述:

表1 Camera_capture 模块部分信号Tab.1 Partial signals of camera_capture module

2.3 DDR_control 模块设计

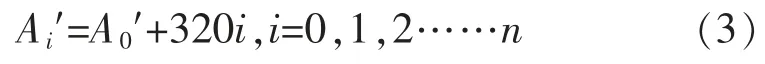

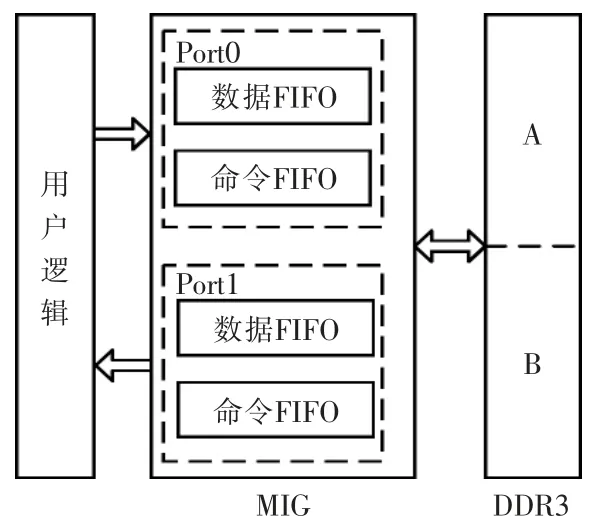

DDR_control 模块用于实现对DDR3 的读写操作。 经过Camera_capture 模块输出的相机数据存储在DDR3 SDRAM 芯片MT41J128M16JT 中,DDR3 SDRAM 内部分块(A 和B)存储相机数据,如图4 所示。 利用DDR 核配置2 个64 bit 的双向端口Port0和Port1,DDR 核中的仲裁器来判断处理当前状态是Part0 还是Part1 操作。 本设计系统中,FPGA 与DDR3 进行信息交互所需接口信号是通过调用DDR 核产生,降低开发难度,增加设计系统稳定性。Port0 对DDR 进行写操作,Port1 对DDR 进行读操作,DDR_control 模块直接例化MIG 生成的时钟单元和DDR 核。DDR 进行写操作时,用户逻辑先将数据写入数据FIFO,送入DDR 核的Port0,再将命令写入命令FIFO;DDR 进行读操作时,用户逻辑先将命令写入命令FIFO, 再将数据从Port1 读出。 DDR读操作时,其地址必须和写操作地址一致。 在写操作过程中,

式中:A0为Port0 写DDR 的初始地址;Ak为第k 次Port0 写DDR 的地址。 在读操作过程中,

式中:A0′为Port1 读DDR 的初始地址;Ai′为第i 次Port1 读DDR 的地址。

图4 DDR3 读写控制流程Fig.4 Control flow chart of DDR3 read-write

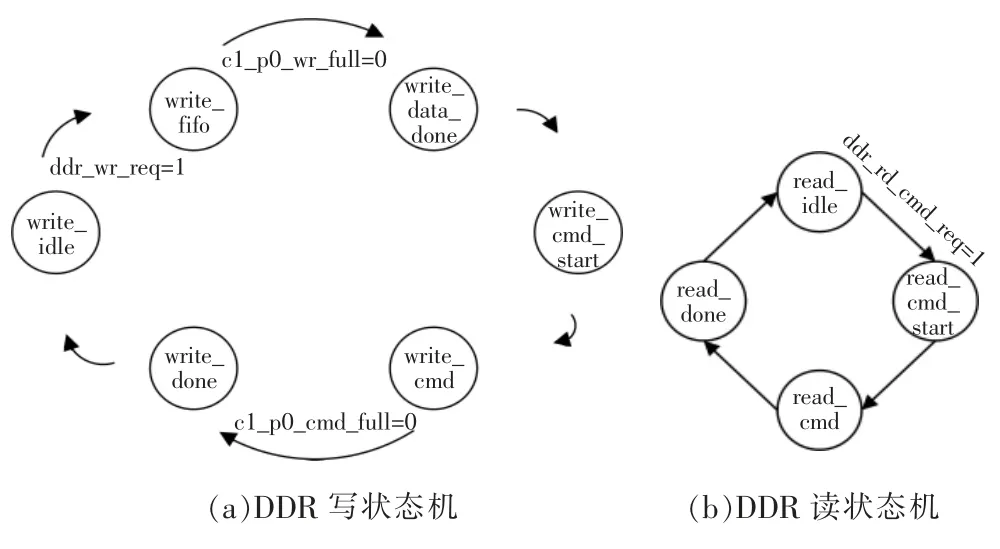

本设计系统中,Port0 的写命令为010,Port1 的读命令为001。 DDR 读写操作状态机如图5 所示。

图5 DDR3 读写操作状态机Fig.5 Operation state machines of DDR3 read-write

2.4 VGA_control 模块设计及仿真测试

VGA_control 模块实现VGA 行列信号产生,相机采集图像数据及DDR 读操作相关信号输出。VGA_control 模块在读使能条件下, 将DDR_control模块输出的相机存储数据按标准VGA 协议输出至外部显示器。输出图像采用RGB565 模型,即一个像素16 位,红色(R)占5 位,绿色(G)占6 位,蓝色(B)占5 位。DDR_control 模块输入的64 bit 相机数据需转换为4 个像素输出,其转换方法如下:

在VGA 输出的行列信号有效状态下, 将读取的64 bit 相机数据[63:59]位输出至红色信号通道;[58:53]位输出至绿色信号通道;[52:48]位输出至蓝色信号通道, 一个像素输出完成。 依次类推,将[47:43]位输出至红色信号通道,[42:37]输出至绿色信号通道,[36:32]输出至蓝色信号通道,完成第二个像素输出。 依次循环,完成第三个、第四个像素输出。 在VGA 为640×480(60 Hz)显示模式下,定义相关参数见表2。

表2 VGA 为640×480(60 Hz)显示模式相关参数Tab.2 Display mode related parameters of VGA within 640×480(60 Hz)

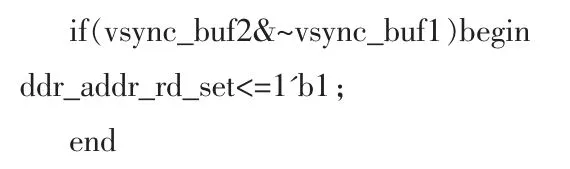

在VGA_control 模块中, 通过检测列同步脉冲下降沿来产生DDR 地址复位信号,代码实现如下:

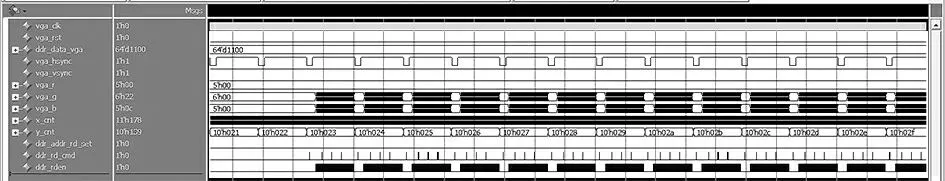

针对VGA_control 设计模块,利用Modelsim 对其进行仿真验证,如图6 所示。 在模块测试过程中,VGA 读取DDR 数据为十进制1100,与DDR 输出数据相吻合。 同时,VGA_control 模块中时钟频率为25 MHz,所设计的计数器计数准确,输出信号逻辑正确、稳定。

图6 VGA_control 模块信号仿真图Fig.6 Signals simulation diagram of VGA_control module

3 系统测试

将设计程序固化在Spartan6 FPGA 中,搭建系统。测试过程中,程序运行稳定,像质清晰,图像实时动态性良好。利用ChipScope 在线抓取信号,如图7 所示,分析结果表明,在DDR3 读写使能满足的条件下,当相机写入DDR3 SDRAM 存储器的64 bit 数据为BCF3BCF3BCF3BCF3 时,从DDR3 SDRAM 存储器读出的64 bit 数据为BCF3BCF3BCF3BCF3,DDR3读写数据正确。 系统时钟精确,FPGA 外部接口信号设计准确。 图8 为采集系统运行效果,在低照度条件下,系统能有效稳定地实现高质量的实时图像采集。

图7 ChipScope 在线抓取DDR3 数据图Fig.7 DDR3 data diagram of ChipScope online grab

图8 图像实时采集系统测试图Fig.8 Test diagram of image real-time acquisition system

4 结语

本文基于FPGA 和DDR3 设计的CMOS 相机图像采集系统, 利用Verilog 语言实现各模块逻辑功能,系统能有效地实现30 帧/s 的图像实时显示。 同时,系统能针对不同分辨率的CMOS 相机进行灵活地调整,简单快捷,可移植性强。 系统外部输入时钟25 MHz,具有标准的接口协议,工作稳定,结构简单,成本较低,可应用于对实时性成像和系统体积要求较高的领域。