基于FPGA 的高频动态编码信号采集存储系统设计

2019-10-09殷俊红

张 鹏,谢 锐,殷俊红

(中北大学 电子测试技术国家重点实验室 仪器科学与动态测试教育部重点实验室,太原030051)

随着电子产业的飞速发展, 数据的传输速度、存储容量均在不断提高。 传统的数据采集存储系统在速率和容量上已经不能满足用户需求,对高频信号采集存储设备的研发提出了新要求。 目前市场上虽然销售许多采样率高、 存储量也大的存储产品,但是他们多数针对性强, 是为专门应用领域研发,实时性和通用性差,成本也高,而且系统功耗和体积较大[1-3]。 所以针对高频信号的高速率、大容量、低功耗、小体积等要求,研制新型的高速采集存储装置迫切需求。

1 系统总体设计方案

考虑高速信号采样策略、抗干扰设计分析以及综合系统功能指标需求,本文设计系统选用集成度高、低功耗、处理速度快以及现场可升级的FPGA 作为主控逻辑单元,再结合系统分辨率、采样频率以及精度等对主要芯片选型,并设计高速A/D 转换电路和高速eMMC 存储电路,从而完成数据的采集存储。 如图1 所示为系统整体结构框图。

图1 系统结构框图Fig.1 System structure diagram

系统工作流程: 系统上电后处于待触发状态,当接收到外部触发信号后, 系统进入采集状态,为满足A/D 转换输入信号的幅值要求,待测信号首先经过衰减电路, 再经差分电路后转换为高速LVDS信号并送至A/D 转换芯片,A/D 转换后输出的数字信号经FPGA 处理后写入内部FIFO 缓存, 为使采集到的数据不易掉电丢失,一次采集结束后再将缓存数据全部转存至eMMC, 此时完成一次完整的采集存储。 再用USB3.0 将回收装置与计算机连接,利用读数软件将数据信号读取到LabVIEW 上位机进行显示,并完成进一步的数据分析和处理。

2 系统硬件设计

2.1 衰减电路

由于待测引信编码信号的最大幅值为6 V,最小为0 V,信号的中心频率为30 MHz,最高频率可达50 MHz。 而A/D 转换电路只接收输入为-0.3 V~2 V 的信号,故需对源输入信号做衰减处理,结合高频电路中电容等效特性,在衰减电路设计中我们采用示波器探头衰减原理[1],衰减电路原理如图2所示。

由图2 可知,IN 为被测信号输入端,OUT 为衰减后信号输出端, 可通过调节电阻R1和R2的分压来实现对输入信号的衰减。 由于篇幅有限对电路的分压比分析不再赘述。 经过仿真分析,本文设计中R=9 MΩ,C=8 pF,R2=1 MΩ,C2=72 pF。

图2 衰减电路模型Fig.2 Attenuation circuit model

2.2 信号差分化

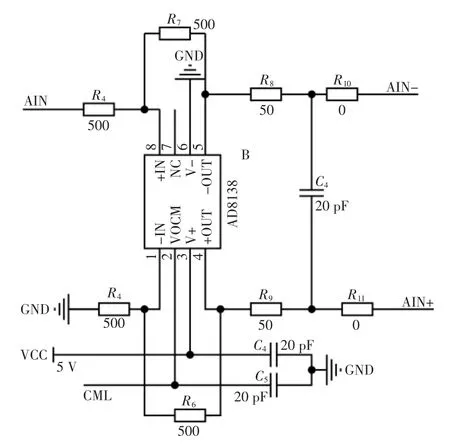

由上述可知衰减后的信号仍为单端模拟信号,所以必须对其差分化后才能送至后级A/D 转换器。对比变压器耦合配置和利用集成信号调理芯片实现信号差分化的方式,考虑到噪声引入,A/D 转换的可靠性与准确性以及信号采集的完整性,本文选用集成调理芯片AD8138 实现输入信号的差分化,其内部结构独特, 具有反馈特性, 而且采用专门的XFCB 双极性制造工艺,谐波失真度非常低[4-5]。如图3 所示为AD8138 差分化原理图。

图3 信号差分化原理图Fig.3 Schematic diagram of signal differential differentiation

由图可知噪声增益为

若输入信号无阻抗,则R4=R5=R6=R7,图中R10和R11是为了增益补偿。

2.3 高速A/D 采集电路设计

在采集存储电路中,A/D 转换电路是关键部分,芯片选型尤为重要,本文选的AD9484 是一款8位的单通道高速ADC 芯片[7],其最高转换速率可达500 Msps, 而且功耗超低, 动态特性较高, 输出为LVDS 数字差分信号。 考虑到系统低功耗要求以及低成本问题,AD9484 的输入时钟由FPGA 通过内部锁相环PLL 产生送至FPGA 的LVDS I/O 接口输出提供。如图4 所示为AD9484 的时序图,如图5 所示为AD9484 的外围配置原理图。

图4 AD9484 的时序图Fig.4 Sequence diagram of the AD9484

图5 AD9484 原理图Fig.5 Principle diagram of the AD9484

由图可知,完成一次模数转换需要16 个时钟周期。 DCO±是2 个数据时钟输出引脚,上升沿有效,其作用是将输出数据同步传输至FPGA 做进一步处理。

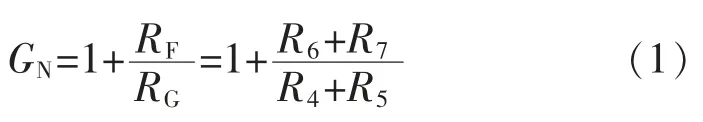

2.4 eMMC 存储电路设计

存储介质是采集存储装置的另一关键部分,目前存储介质种类很多,对比考虑器件成本、品质,读写速度以及容量等因素[6,8,12],本文选择美国镁光公司的eMMC5.0 芯片作为本系统存储介质, 型号为MTFC4GACAJCN1, 最高写入/读取速度为14/160 MB/s。为提高数据的读写速度,本文采用2 片eMMC级联, 将数据位扩展至16 位。 如图6 所示为单片eMMC 的原理图。

图6 eMMC 原理图Fig.6 Principle diagram of the eMMC

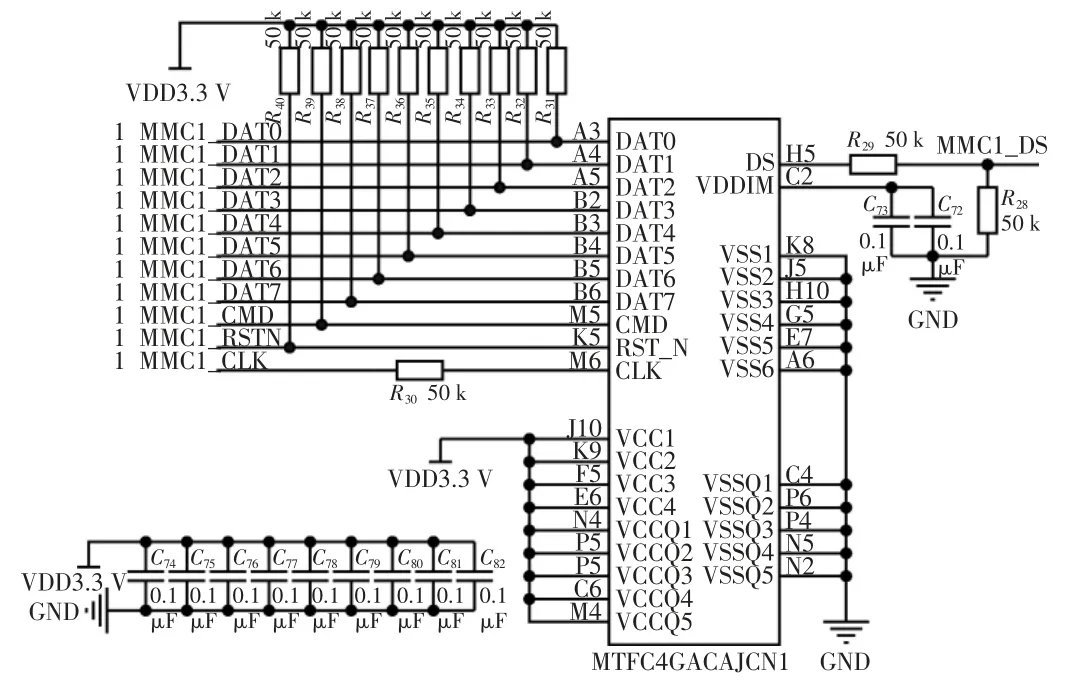

3 主控电路设计

本系统选用广泛应用于设备控制领域的FPGA作为主控芯片,其内部逻辑资源丰富,编程灵活多样,易操作,且内部采用并行执行结构[11],在处理不同事件时不会出现资源竞争。 依据系统对最大时钟频率,用户自定义I/O 数量,逻辑资源,功耗以及成本等多种因素,选择赛琳斯公司的Spartan—6 系列的FPGA 为主控芯片,具体型号为XC6SLX25-CSG324。考虑到调试和数据掉电不丢失问题,系统采用JTAG和MAster Serial/SPI 2 种配置方式,配置芯片为XCF04SVO20C[9-10]。系统整体的功能实现是在硬件电路模块的基础上,通过VHDL 硬件描述语言和FPGA内部集成的IP 核来实现的,逻辑框图如图7 所示。

图7 系统逻辑框图Fig.7 System logic block diagram

由图可知,FPGA 接收来自外部LVDS 数据信号,时钟输入信号,电源开关以及外部触发信号,然后在FPGA 控制下,数据先缓存在内部FIFO,完成采集后将数据再读取到eMMC 中存储。

4 系统测试与验证

图8 所示为系统测试流程。

图8 系统测试流程Fig.8 System test flow chart

图9所示为示波器显示源高频动态编码信号,图10 为系统标定后采集到的实测高频动态编码信号。

图9 示波器源高频动态编码信号Fig.9 Oscilloscope source high frequency dynamic coding signal

对比可知,两波形基本一致,经计算,相邻窄波距离为1 μs,基本还原了原始信号。

5 结语

本文设计的高速采集存储系统,针对高频信号特征,对其进行幅值衰减,信号差分化以减小误差,提高抗扰能力。 再对关键采集、存储和控制芯片综合选型并完成电路设计。 使用FPGA 实现高速时序逻辑控制,数据的缓存,保证了数据的完整性。 经实测实验验证,本系统采样率高达500 Msps,且能稳定采集,信号完整性良好,满足设计要求,可用于高频动态编码信号的测试。

图10 本文系统实测高频动态编码信号Fig.10 High frequency dynamic coding signal measured by the system in this paper