基于SOPC的氨氮含量检测系统的设计

2019-09-19

(1.浙江正泰中自控制工程有限公司,浙江 杭州 310027; 2.南昌大学 信息工程学院,江西 南昌 330031;3.南昌大学 机电工程学院,江西 南昌 330031)

氨气敏电极法测氨氮不需要将水样进行复杂的处理,并且不受色度、浊度及悬浮物的影响,测量还具有线性范围宽、操作简单等优点。氨气敏电极法测氨氮首先将水样 pH值升高,让水中的大多数的氨氮转换为氨气的形式存在,当氨气穿过电极的渗透膜进入氨气敏电极时,就可根据产生的电压与氨气浓度的关系得出水中的氨氮含量。

这种方法利用电化学原理将被测参数转换为电压值,通过建立标准拟合曲线来间接测量所需要的参数,符合嵌入式系统在污水处理方面的应用发展趋势[2-4]。

本设计将根据Altera公司Nios II软核概念,在FPGA上建立基于SOPC技术的Nios II双核系统,两个CPU分别作为电极电压信号的数据采集处理器与氨氮含量的数据计算、显示处理器。对电压信号的采集主要是利用具有A/D转换功能的芯片来控制,然后将采集到的数据存入到共享存储器;对氨氮含量的计算、显示主要是利用最小二乘法计算标准曲线拟合参数,并利用拟合方程,由采集到的数据就能计算出氨氮浓度,并可通过LCD对结果进行显示。通过Nios II里的硬件互斥核(Mutex Core)组件去控制两处理器与共享存储器的交互,避免彼此之间产生干涉,从而给两处理器间的信息交互创造了操作安全、行为可靠的环境。如此就达到了在一片FPGA内完成迅速、精准且不产生二次污染的氨气敏电极法测氨氮的目的。

1 系统的总体方案设计

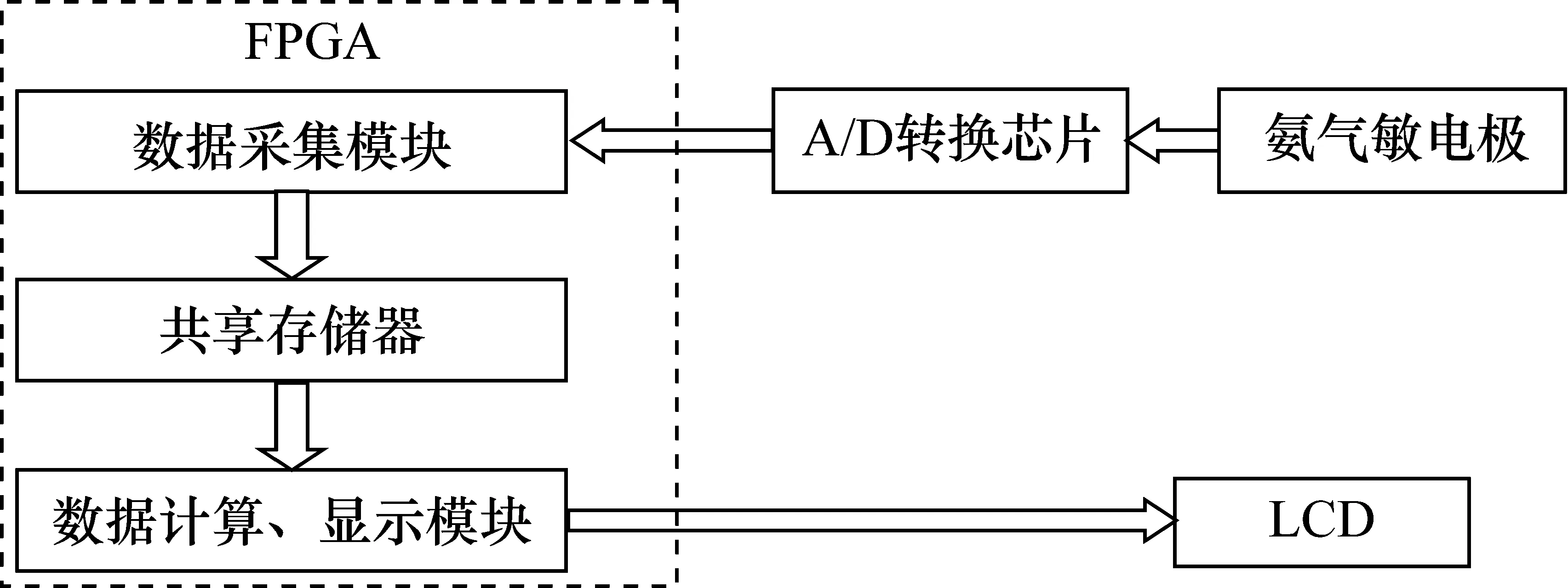

系统模块的设计可从采集模块与计算和显示模块这两方面进行构建。其中,对于数据采集模块,氨气敏电极测量时所产生的电压模拟信号由A/D转换芯片实施放大滤波操作后,转变成数字信号直接输入到FPGA中。对于数据计算、显示模块,需先确定标准氨氮曲线,通过最小二乘法对标准曲线进行拟合,再将数据带入到拟合方程中,就可得到待测液中氨氮的含量, 最后利用液晶显示屏实现数值的显示。 系统总体框图如图1所示。

图1 系统总体框图

如图1所示,Nios II系统的两个模块利用共享单元对数据进行交互,而对共享单元访问的协调将通过Qsys工具组件里的硬件互斥核组件去控制。方案设计中,FPGA选择 Altera公司的Cyclone IV系列中的EP4CE115芯片,其内部拥有114480个逻辑单元、266个乘法器、4个PLL,且片上存储器资源高达3.9 MB。

2 系统硬件设计

2.1 数据采集模块硬件设计

(1)

(2)

水样经过处理后在 pH大于11时开始按式(2)进行反应,水中氨氮以氨气形式存在, 氨气进入氨气敏电极后按式(1)进行反应,由于电极内部氢离子发生变化而产生电极电压,该电压值大小与水中氨氮含量存在一定关系,从而可以计算出氨氮的值[5-6]。

在氨氮含量的测量中,电极产生的电信号通常较小,故需使用高精度的A/D转换器,对信号进行放大滤波并数字化处理。实际设计中选择美国的ANALOG DEVICE公司所制造的具有较高精度的24位串行A/D转换器 AD7710。其运用的是Sigma-Delta转换技术来使转换器在满足24位精度的条件下仍然不丢失码。对于输入到调节器的前端的信号,增益大小可以通过程序编译的方式进行设定。调节器的输出需经由芯片自带的数字滤波功能进行信号处理。 AD7710与FPGA的硬件电路连接图如图2所示。

图2 AD7710硬件电路连接图

电极产生的模拟信号由AIN1输入到AD7710,经过AD7710处理后得到的数字信号通过SDATA口传入FPGA中。图2中,TFS是帧同步传输端,RFS是帧同步接收端,DRDY是逻辑输出端。而SDATA在RFS端接入低电平信号时才打开,对数据进行写操作时则要求TFS端接入低电平信号,DRDY处于下降沿就意味着输出端有新的数据可供传输,待输出端的数据传输完毕后,该端口就变成高电平。

2.2 数据显示模块硬件设计

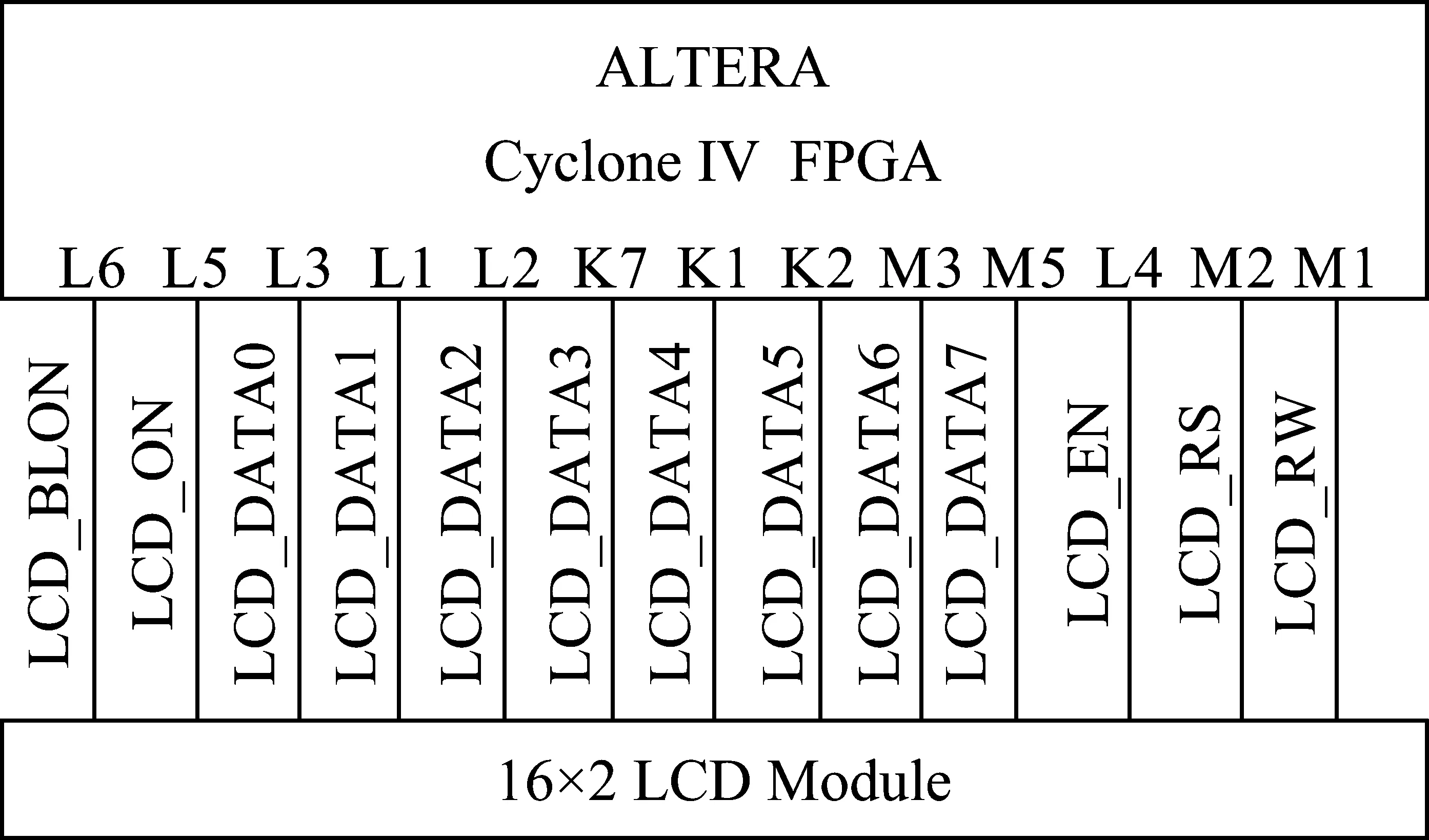

因为数据显示模块中所需显示的部分比较简单,故选择LCD1602与HD44780进行模块设计,FPGA与系统数据显示模块的连接示意图如图3所示。

图3 FPGA与LCD显示模块连接示意图

HD44780可由Qsys工具里的 Character LCD IP核进行控制,通过切换LCD_RW、LCD_RS、LCD_EN等端口处电平的高低,就能完成对氨氮值的数据显示。

2.3 基于Qsys搭建硬件平台

系统的硬件部分的构建需通过Quartus II开发软件里的 Qsys系统集成工具,在开发套件给出的外设中,根据实际系统要求使用合适的CPU、存储器与相应的外设。运用Quartus II可自动生成对应器件的配置文件,将这些文件下载进 FPGA,就可为软件部分的设计提供无缝衔接的硬件架构。Qsys作为SOPC Builder的下一代产品,是Altera公司在Quartus II 11.0版中新发布的系统集成工具。与SOPC Builder工具相比,它在性能和工作效率方面有了很大提高,而且在设计的重用性方面也有所增强,加快了开发的进程。

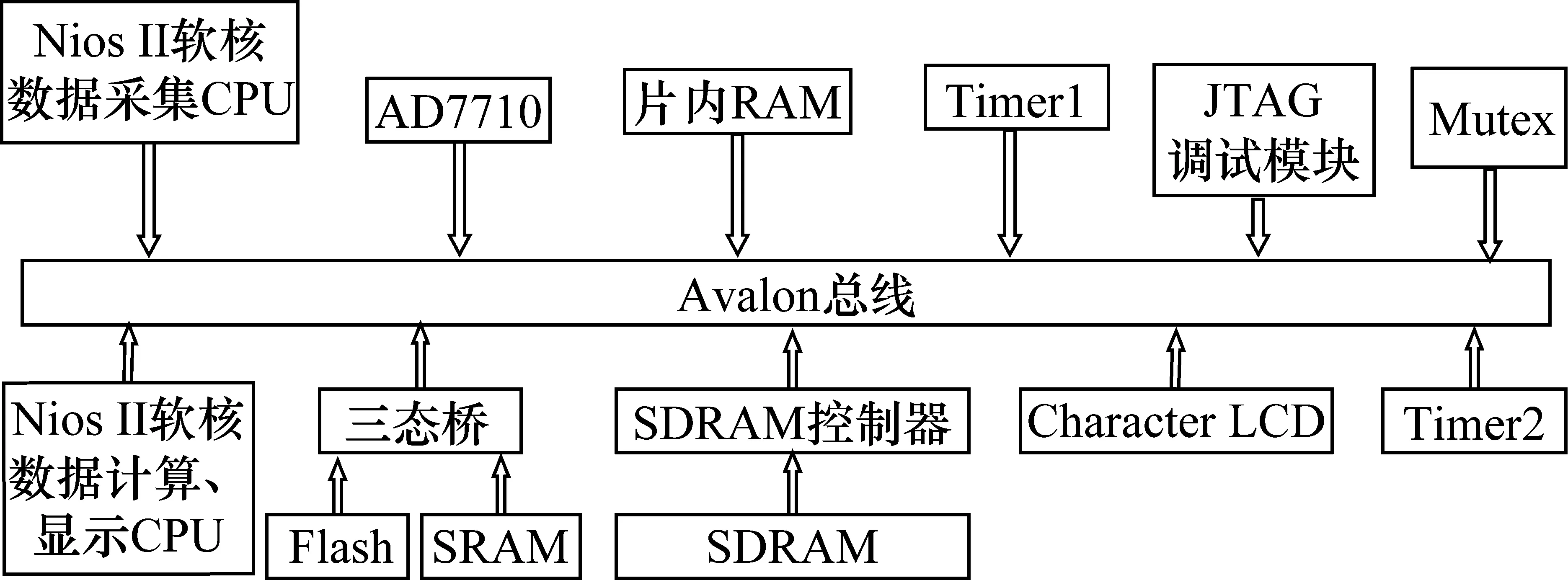

在系统配置的过程中,需先对在系统中作为工作时钟的 Avalon总线时钟进行选择,配置本系统的时钟为100 MHz。系统的时钟频率还可用于外围设备生成时钟分频器或波特率发生器等,加入锁相环(PLL),就能够得到其他器件所需的时钟,另外也可对时钟相位进行适当的调整。选用两个Nios II软核处理器,分别当作采集模块的CPU与计算、显示模块的CPU。 两模块CPU的共享存储器通过选择片上RAM进行构建,同时通过Mutex core控制CPU与共享存储器数据的存取。因为开发套件里未给出能与AD7710相合的IP核,因此需通过Verilog HDL语言去编译、描述用户自定义的IP核。通过配置Character LCD对HD44780进行配置。系统的定时功能的设置需通过定时器组件(Timer)实现。在FPGA上,下载程序与测试功能操作都由串口JTAG/UART组件实现。另外,还应增添SDRAM控制器与三态桥,作为接入SDRAM与片外Flash、SRAM的端口。 同时给其他外设增添合适的I/O口。

实现上述设置操作后,接着就可对系统的外部设备配置相对应的地址信息以及中断、重置信号,单击“Generate”就能生成Qsys系统,于顶层Verilog文件内对顶层系统实施例化处理, 同时进行编程与测试,就可实现系统的硬件配置。 Qsys系统配置示意图如图4所示。

图4 Qsys系统配置示意图

3 系统软件设计

系统的软件部分的设计与开发主要包括数据采集模块与数据计算、显示模块两个部分,另外还包括利用硬件互斥核来控制双处理器与共享外设交互的软件程序的设计。各模块的软件部分设计均在新版本的Nios II嵌入式处理器系统软件开发工具Nios II SBT上完成。

3.1 数据采集模块软件设计

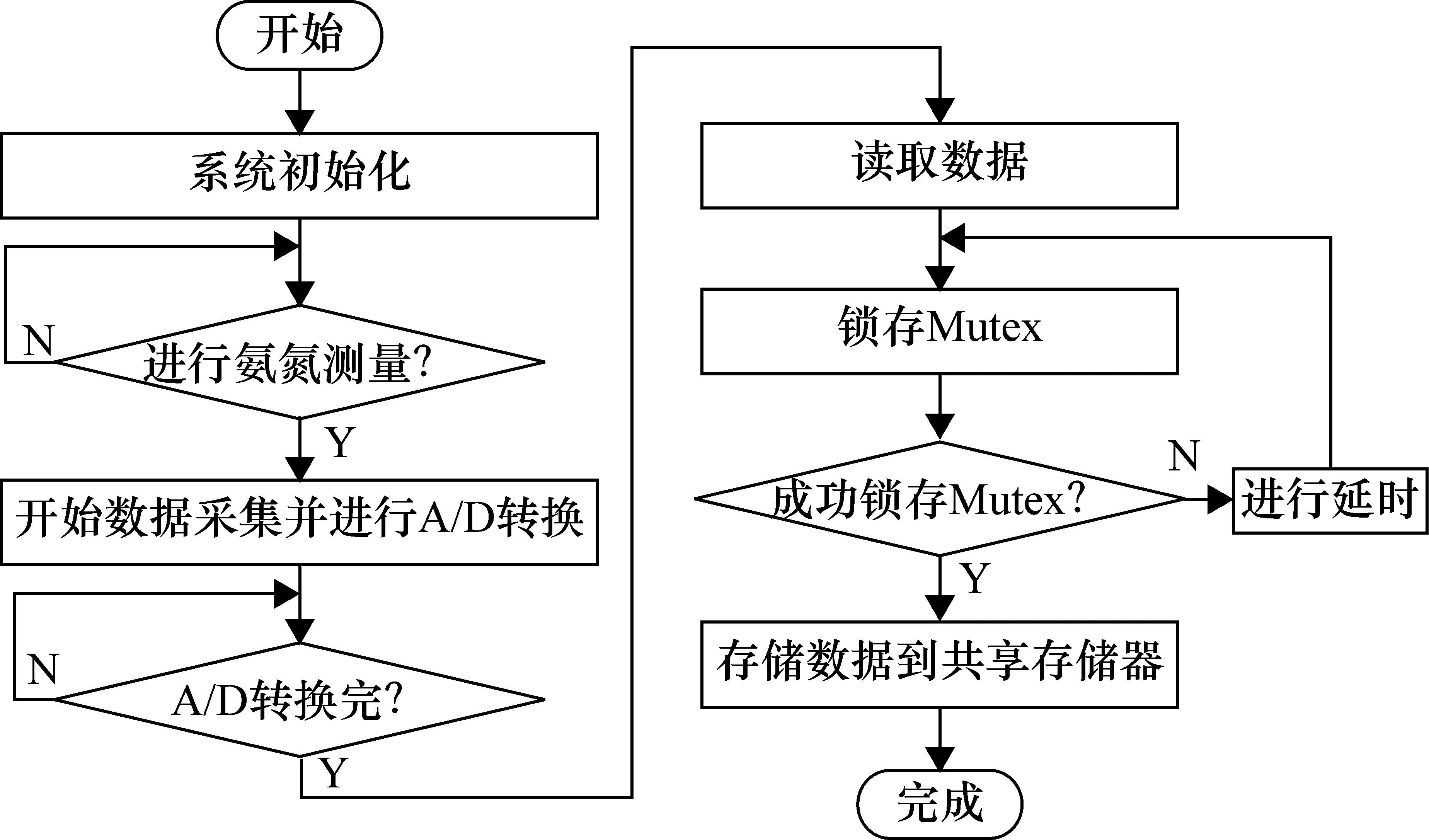

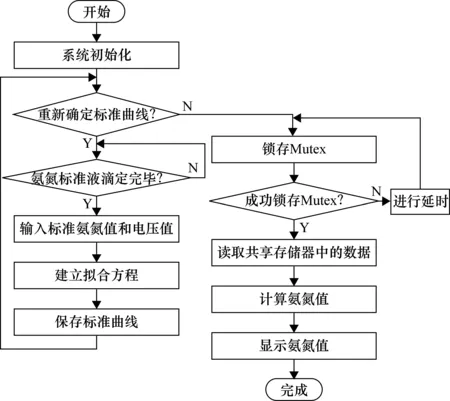

对数据采集模块部分的程序编译是为了实现将氨气敏电极传感器采集到的模拟电信号,在完成A/D转换操作后,再将转换得到的数字信号进行存储的目的。 通过使用自定义的IP核去实现对AD7710的操控。而需设计的关于软件方面的内容为系统对所需的数据实施测量与储存的程序。在系统内,片上存储器被当成采集处理器与计算、显示处理器的共享存储单元,是两处理器相互进行数据交互的通道。不过在两处理器一同对片上共享 RAM进行数据存取时,系统就会有崩溃的可能,需利用 Mutex core去控制数据的存取,故应对利用 Mutex core控制两处理器对共享RAM进行访问的软件程序进行编写[7-9]。 软件流程图如图5所示。

图5 数据采集模块软件流程图

通过Mutex core来控制两处理器与共享存储器进行数据的交互,需先声明代表硬件Mutex设备结构体alt_mutex_dev,接着用altera_avalon_mutex_trylock( )函数尝试对 Mutex进行加锁,操作完成后就开始进行与存储器间的数据交互,交互结束后再用altera_avalon_mutex_unlock( )函数对Mutex进行解锁[10-11]。部分程序如下。

#include

……

alt_mutex_dev*mutex=altera_avalon_mutex_open(“/dev/mutex”);//获取一个指向Mutex设备结构体的指针

INT8U flag;

flag=altera_avalon_mutex_trylock(mutex,1);

//试图对Mutex加锁

if(!flag)

{……//对共享资源访问altera_avalon_mutex_unlock(mutex);//对Mutex解锁}

else {delay(5000);flag=altera_avalon_mutex_trylock(mutex,1);}

3.2 数据计算、显示模块软件设计

在对数据计算、显示模块的构建之前,应当先确立需通过标准试剂滴定来建立的标准氨氮拟合曲线,再利用拟合曲线将测得的数据带入计算,最后把计算得到的氨氮值显示在液晶显示屏上。

在装有氨气敏电极传感器的容器中加入氨氮标准液,把标准液 pH调至11以上,使用氨气敏电极进行测量,记录电压值和对应的氨氮值并输入系统。 使用最小二乘法拟合方程:

y=ax+b

(3)

式中,y为氨氮含量;x为电压值;a与b分别为拟合参数,由下列方程组求出:

(4)

利用最小二乘法对曲线进行的拟合与带入计算方面的内容应在Nios II IDE(集成开发环境)内来完成, Altera公司已于 Qsys内给出了 Character LCD作为 Nios II与液晶屏的 Avalon接口, 并在 Nios II IDE内给出了完整的开发平台。

软件设计的流程图如图6所示。

图6 数据计算、显示模块软件流程图

4 系统测试

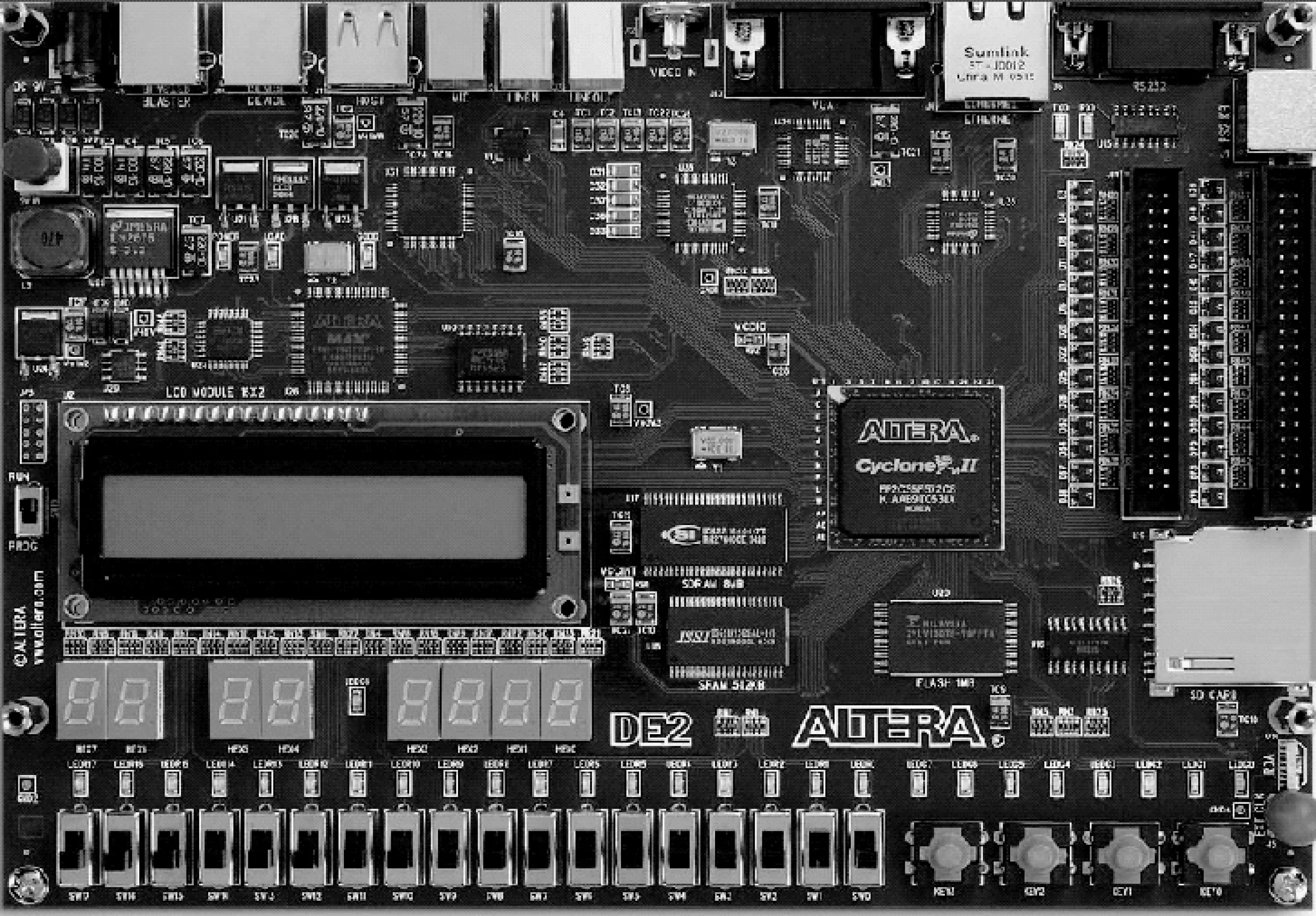

对系统可靠性进行的相关测试,可选择在实验室中利用DE2-115开发板展开相关性能测试。在DE2-115中,包含了一片Cyclone IV系列的EP4CE115芯片,且集成了HD44780和LCD1602,为系统测试提供了充分条件。 DE2-115开发板如图7所示。

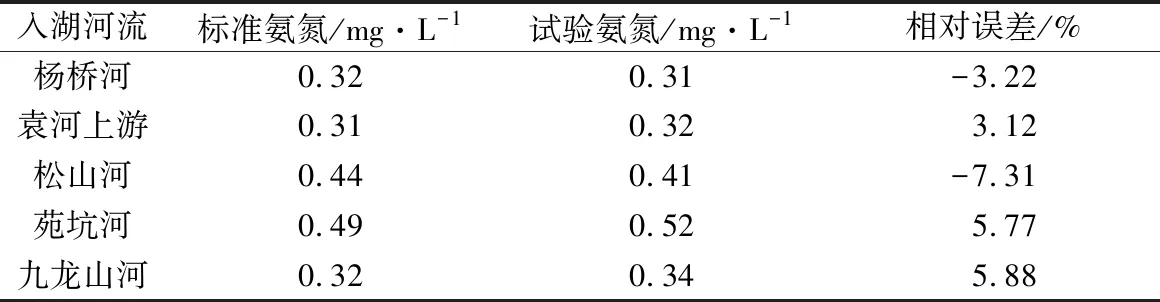

将程序下载到开发板之后,利用江西省新余市仙女湖入湖河流平水期的水样进行试验[12],采用纳氏比色法测得的氨氮值和系统测得的氨氮值数据对比结果如表1所示。

图7 DE2-115开发板

入湖河流标准氨氮/mg·L-1试验氨氮/mg·L-1相对误差/%杨桥河0.320.31-3.22袁河上游0.310.323.12松山河0.440.41-7.31苑坑河0.490.525.77九龙山河0.320.345.88

经过计算分析可知,此方案还存在一定程度的测量误差,但总体上能呈现出较好的测量效果,基本上能实现设计所预期测量标准。

5 结束语

本文通过FPGA实现了利用氨气敏电极法对水体氨氮进行测量的双处理器系统设计。选择当前较流行的FPGA可编程逻辑器件作为处理器,可以使系统运行速度较快的同时保证可靠性,同时拥有良好的扩展性。 电化学法测氨氮过程简单且无二次污染,适应水质监测仪器发展潮流,符合嵌入式系统在污水处理中的发展要求。在FPGA上建立的Nios II双核系统,仅用一片芯片完成了数据采集、存储、计算和显示的工作,充分利用了 FPGA片上资源,降低了开发成本与功耗,缩减了设计周期与风险,提升了系统性能。