基于FPGA的CAN总线控制器设计

2019-09-13纪振平

纪振平,王 航

(沈阳理工大学 自动化与电气工程学院,沈阳 110159)

现场总线是由电气及自动化领域发展而来的一种数据总线,其主要目的是为了解决工业领域的仪器仪表、控制器、执行部件等设备间的数字通信以及这些控制器和控制系统之间的信息传递的问题。在众多现场总线中德国 Bosch 公司推出的CAN(Controller Area Network)总线以其实时性强、可靠性高、功能完善、成本合理等突出优点,被越来越广泛地应用于自动化领域中[1]。

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物,是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点[2]。在电子计算机断层扫描的成像过程中,由于系统中有大量的模拟、数字信号需要处理,传统单片机的引脚数量远远不够,能处理的电平信号种类单一且片上外设部分功能冗余。所以通常采用FPGA作为电子计算机断层扫描设备的硬件功能控制器。

传统FPGA_CAN总线通信节点模式为 FPGA+SJA1000+PCA82C250。在该模式下的CAN通信节点中,FPGA输出的信号经电平转化为5V标准驱动SJA1000,SJA1000则根据输入信号的时序关系从总线AD获取或发送数据。从FPGA获取的数据经过处理后,组成标准格式的数据帧通过驱动器PCA82C250发送到传输线CANH和CANL上的CAN总线通信模式[3]。本文所设计的CAN总线控制器是基于FPGA设计一个集成在其内部的CAN总线控制器,相较于传统的FPGA-CAN通信节点,具有减少了硬件电路设计,节约成本,使用更加灵活,专用性与集成度更高等特点。

1 CAN总线协议层简介

1.1 CAN通信协议帧格式

CAN总线协议的报文种类分为五种,分别是数据帧、遥控帧、错误帧、过载帧、帧间隔,其中最为核心的是数据帧。数据帧由 7 个位场构成,包括帧起始、仲裁场、控制场、数据场、CRC 场、应答场、帧结尾[4]。

1.2 CAN总线位时序

CAN总线协议的报文由各个数据位组成,CAN总线协议把每一个数据位的时序拆解成四部分。每个数据位均包括同步段(SS段),传播时间段(PTS段),相位缓冲1段(PBS1段),相位缓冲2段(PBS2段)。CAN协议中定义了时间份额Tq,其长度是系统工作时钟tSCL的倍数[4]。在1个数据位中,同步段为1个时间份额,传播段可设置为1~8个时间份额,相位缓冲段1可设为1~8个时间份额,信息处理时间小于或等于2个时间份额,相位缓冲段2为相位缓冲段1和信息处理时间的最大值。1个位时间总的可以包括 8~25个时间份额[5]。

2 CAN总线控制器设计

为增强CAN总线节点的通信性能,并减少对FPGA片上资源的占用。本文从优化控制器结构和采用时序逻辑进行功能模块设计两方面入手,建立了性能优于以往的CAN总线控制器模块。

在设计过程中,采用EDA设计的经典设计思路,即自顶向底设计,自底向顶实现。其设计过程如图1所示。

图1 CAN控制器的设计过程

2.1 控制器的新型结构设计

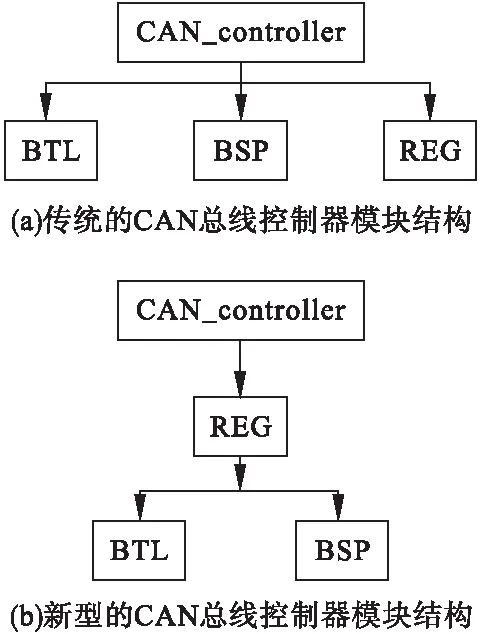

在传统CAN总线控制器的设计中,各个功能模块间不存在例化关系,而是共同例化于顶层模块。在这种结构下,寄存器处理模块(REG)对位流处理器模块(BSP)和位时序控制模块(BTL)的配置参数需要先传递到顶层模块,再由顶层模块传递至子模块;而由位流处理器模块接收到的信息也由相反的顺序送回到寄存器处理模块。因此,对于片上资源的占用和时序的延迟都有一定的影响。

本文采用了新型的控制器结构,用于取代传统设计结构。在该结构下,寄存器处理模块(REG)可直接对位流处理器模块(BSP)和位时序控制模块(BTL)进行参数配置和收发信息的交互,减少片上资源的占用和时序的延迟。两种结构的对比如图2所示。

2.2 采用时序逻辑的功能模块设计

时序逻辑电路是数字逻辑电路的重要组成部分,主要由存储电路和组合逻辑电路两部分组成。

图2 CAN总线控制器的设计结构的对比

时序逻辑电路在任何一个时刻的输出状态由当时的输入信号和电路原来的状态共同决定,而其的状态主要是由存储电路来记忆和表示的。同时时序逻辑电路在结构以及功能上的特殊性,相较其他种类的数字逻辑电路而言,往往具有难度大、电路复杂并且应用范围广的特点[6]。

在传统的CAN总线控制器设计中,大量的位时序切换信号设计使用了组合逻辑设计。在新型的CAN总线控制器设计中,则改为使用时序逻辑设计。将传统CAN总线控制器位时序切换信号所采用的组合逻辑放入寄存器内,并添加时钟信号变为时序逻辑。使得整个控制器都在同一时钟的控制下,降低了组合逻辑中存在竞争冒险的可能性,提高了CAN总线节点的稳定性。信号采用组合逻辑设计的程序如下。

assing hard_sync=(rx_idle | rx_inter)&(~rx)& sampled_bit &(~hard_sync_blocked)

信号采用时序逻辑设计的程序如下所示。

assign @(posedge sys_clk_i,negedge rst_n_i)begin

if(!rst_n_i)

hard_sync <=1’b0;

else if((rx_idle | rx_inter)&(~rx)& sampled_bit &(~hard_sync_blocked)

hard_sync <=1’b1;

else

hard_sync <=1’b0;

end

2.2.1 REG模块设计

REG模块作为寄存器处理模块,负责对CAN_controller寄存器的配置信息进行存储,包括各个待接收发送数据的寄存器,验收代码寄存器,验收屏蔽寄存器,总线定时器。

REG模块在对一个寄存器赋值的过程中,通过8位输入端口write_in,写入16位二进制数,分别代表8位地址与8位数据。在地址输入时,将ale信号拉高,完成后拉低ale信号,从而对地址锁存。而后拉低wr信号输入数据,既可对地址所对应的寄存器赋值。

REG模块在读取一个寄存器的过程中,通过8位输入端口write_in,输入表示地址的8位二进制数。在地址输入时,将ale信号拉高,完成后拉低ale信号,从而对地址锁存。而后拉低rd信号,即可通过8位输出端口readback得到寄存器内数据。

2.2.2 BTL模块设计

BTL模块作为CAN总线控制器的位时序控制模块,负责检测CAN总线状态和处理与总线有关的位时序,并根据波特率寄存器中的设置值向位流处理器(BSP)提供采样点与采样值,提供发送标志位。该模块在总线上进行检测,当出现帧起始信号进行硬同步,并在接收数据的过程中,每一个下降沿都进行重同步检测,以REG模块提供的可编程时间段PBS1段和PBS2段补偿传播延迟时间,以保证节点的数据连续性。

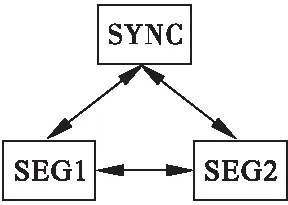

BTL模块包含基于位时序逻辑设计的状态机,在CAN时序逻辑中,同步段SS,传播时间段PTS、第一相位相位缓冲段PBS1、第二相位缓冲段PBS2等四段共同构成一个数据位。

位时序状态机是有限状态机(FSM),共包含三个状态,分别是:包含SS段的SYNC状态;包含PTS段与PBS1段的SEG1状态;包含PBS2段的SEG2状态。

当发生接收时,输入信号rx应在状态机中的完整经过一整个状态,才能被判定为接收到一个完整数据位。

三个状态间转换的关系如图3所示。

图3 BTL模块内位时序状态机

在接收过程中,采样点位于发生在SEG1状态与SEG2状态之间;在发送过程中,发送点位于SEG2状态与SYNC状态之间。

2.2.3 BSP模块设计

BSP模块作为CAN总线控制器的位流处理器模块,主要负责CAN总线节点的数据流发送接收,它还在CAN总线上执行错误检测、总线应答、位填充、CRC校验和验收滤波等功能。

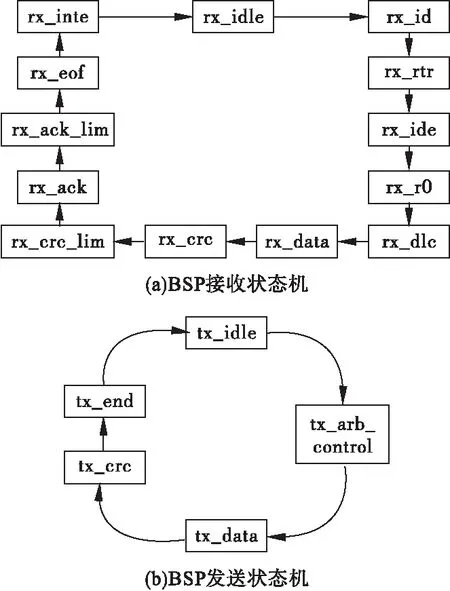

BSP模块包含基于CAN总线数据流逻辑设计的接收状态机和发送状态机,二者皆为有限状态机(FSM)。通过对总线状态的判断和上层命令的识别,分别执行对CAN总线数据流的接收与发送。接收与发送期间的状态机流程如图4所示。

图4 接收与发送期间的状态机流程

在接收状态中,共包含rx_inte(帧间隔)、rx_idle(总线空闲)、rx_id(帧ID段)、rx_rtr(帧rtr位)、rx_ide(帧IDE位)、rx_r0(帧r0位)、rx_dlc(帧DLC段)、rx_data(帧数据场)、rx_crc(帧CRC段)、rx_crc_lim(帧CRC界定符)、rx_ack(帧应答)、rx_ack_lim(帧应答界定符)、rx_eof(帧结尾)等13个状态。

在发送状态中,共包含tx_idle(发送总线空闲)、tx_arb_control(发送帧控制场)、tx_data(发送帧数据)、tx_crc(发送帧CRC)、tx_end(发送帧结尾)等5个状态。

BSP模块中包含作为筛选器的ACR,AMR模块。在CAN总线控制器处于接收状态时,会将接收到的数据流中仲裁段(ID号)的高8位,与CAN总线控制器中验收代码寄存器(ACR),验收屏蔽寄存器(AMR)的设定值进行计算。若ACR[7∶0]与ID号的高八位进行“与”运算的结果,再和AMR[7∶0]进行”或”运算的最终值为8’b1111_1111,则该条信息可以被节点所接收。

BSP模块中还包括用于检查CAN总线发生位错误,填充错误,格式错误,CRC错误与应答错误等五种错误的错误处理模块(ERR),若出现错误数量大于127个时,CAN总线将断开与总线的连接,并将标志位置为“1”提示使用人员。

3 测试结果与比较

3.1 CAN总线控制器的功能验证

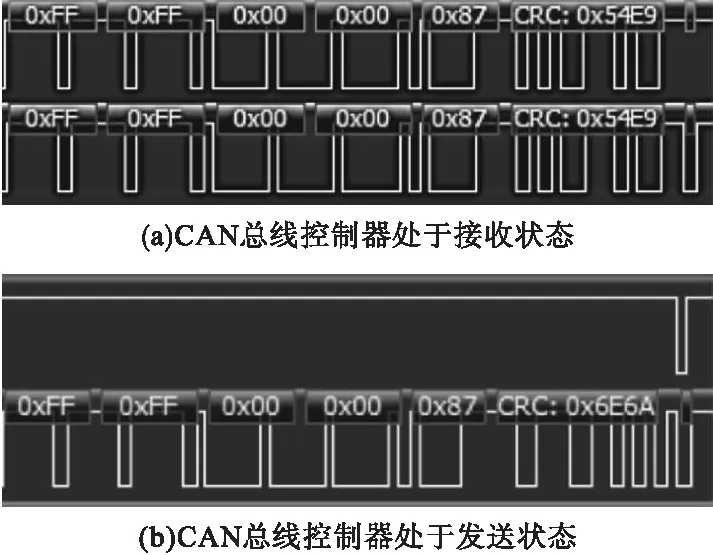

选取ID号为0x250的CAN标准帧做发送测试,该段信息长度为8byte,波特率为1M。当控制器通过TX引脚向总线发送信息时,同在总线上的RX引脚能捕捉到每一个由TX引脚发出的信号,在CRC界定符发送完毕时,RX引脚捕捉到一个不由TX引脚发出的显性电平,表示总线上已有节点对该段信息进行了接收。

选取ID号为0x110的CAN标准帧做接收测试,该测试段的信息长度和波特率均与发送测试信息段相同。当控制器通过RX引脚接收到总线数据时,在CRC界定符接收完毕时,若验证CRC无误,且接收过程中未发生错误,则TX引脚将向总线发送一个显性电平,表示本节点已正确接收。利用逻辑分析仪对CAN总线逻辑电平的监测结果如图5所示。

图5 CAN总线控制器处于接收与发送的状态

3.2 性能比较

3.2.1 FPGA的占用资源比较

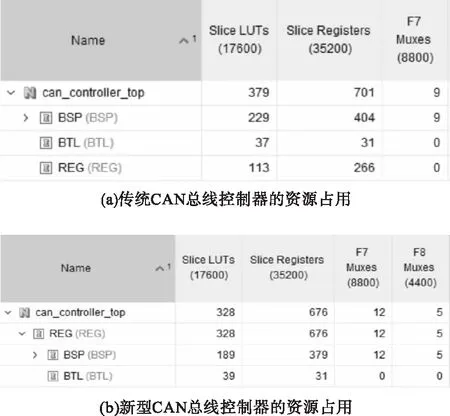

在生成供FPGA使用的比特流文件后,对比传统CAN总线控制器与新型CAN总线控制器对FPGA的资源占用情况如图6所示。

图6 FPGA内部资源占用的比较

由图6可见,即使采用时序逻辑设计增加了部分寄存器资源的占用,但新型CAN总线控制器的总体资源占用仍要小于传统的CAN总线控制器。

3.2.2 CAN总线节点的通信性能比较

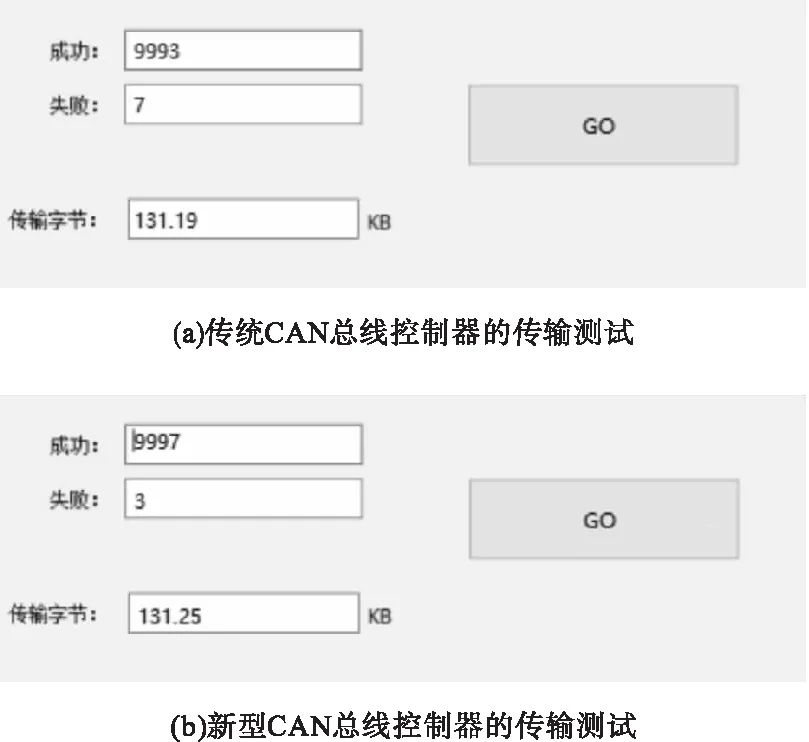

本文通过将两个烧入了CAN总线控制器比特流文件的FPGA与CAN总线分析仪挂载于同一波特率为1M的闭环CAN总线进行测试。在实验过程中A机向总线发送由随机数据构成的数据包,B机接收数据包并解包校验,待通过校验后,B机重新将数据包发回CAN总线。并通过上位机软件与CAN总线分析仪对当前CAN总线上的数据包进行监控。

双机通信测试结果如图7所示,在测试过程中分别对传统CAN总线控制器与新型CAN总线控制器传输了10000个CAN数据包,其中传统CAN总线控制器正确传输9993个数据包,错误传输7个数据包;新型CAN总线控制器正确传输9997个数据包,错误传输3个数据包。由测试结果可见,新型CAN总线控制器的稳定性要优于传统CAN总线控制器。

图7 CAN总线控制器双机通信传输测试

4 结 论

本文对基于FPGA的CAN总线控制器,通过采用时序逻辑设计与新型结构进行优化。经过测试结果表明,该设计可以实现CAN总线节点的通信功能,并降低了FPGA内部资源的占用。综合通信效果,占用资源和使用成本等多方面进行比较,使用本设计进行数字电路的设计要优于使用CAN总线控制器的集成电路进行的设计。