全数字锁相环中数控振荡器增益估计算法研究

2019-09-10李菁俞菲

李菁 俞菲

摘 要:本文提出了一种针对频率综合的全数字锁相环数控振荡器增益的自适应估计算法.该算法可以在短时间内精确估计和跟踪全数字锁相环中数控振荡器的增益值.仿真结果表明,该算法可显著的提高全数字锁相环的相位噪声性能.

关键词:全数字锁相环;数控振荡器;增益估计

中图分类号:TN837 文献标识码:A 文章编号:1673-260X(2019)10-0052-05

1 锁相环概况

锁相环(PLL,Phase Locked Loops)是一个相位反馈控制系统,其输出信号能够自动跟踪输入信号相位,形成闭环控制.由于其独特的优良性能,在通信、雷达、测量和自动化控制等领域得到极为广泛的应用.随着大规模、超高速的数字集成电路的发展,为数字锁相环的研究與应用提供了广阔的空间. 全数字锁相环已经在调制解调、频率合成、载波同步、图像处理等方面得到了广泛的应用.所谓全数字锁相环(ADPLL,All Digital Phase Locked Loops)是指锁相环中的各个模块都是以数字器件来实现,这些数字模块在实现时可以引入优化的算法和结构.因此,与模拟锁相环相比,数字锁相环集成化程度更高,具有更低的功耗,可调节性更强. 全数字锁相环不仅吸收了数字电路可靠性高、体积小、价格低等优点,还解决了模拟锁相环的直流零点漂移、器件饱和及易受电源和环境温度变化等缺点.此外,数字锁相环还具有对离散样值的实时处理能力,已成为锁相技术发展的方向.

全数字锁相环目前已被应用于各类通信和雷达射频无线发射机中,其核心部件数控振荡器(Digital controlled Oscillator,DCO)相比传统的电荷泵(Charge Pump)锁相环的压控振荡器(Voltage controlled Oscillator,VCO)有更高的精度.当锁相环作为频率发生器模式下,全数字锁相环里的DCO会产生稳定的高频信号;当锁相环作为无线收发机的调制解调器模式下,全数字锁相环的DCO将会产生稳定的调频信号.同时,采用DCO的系统可用可编程逻辑器件来实现,也有利于提高系统的集成度和可靠性.

然而,DCO的增益仍然是一个相对来说不确定度较大的量.随着工艺,温度,电压的等外界环境的变化,DCO输出端随输入端变化的频率值是不确定的.DCO的这个特性会使整个全数字锁相环的环路带宽,阻尼系数,相位噪声等关键参数随着外界环境的变化而变化,也会较大的影响环路的稳定性和噪声特性.如果不使用DCO增益估计算法,PLL系统则要求DCO的增益随温度变化的特性接近于线性,否则将会给整个系统造成较大的功耗.而较高的线性度要求则会给DCO的电路设计带来很大的困难,增加设计难度和复杂度.

针对以上问题,本文提出了一种全数字锁相环中数控振荡器增益的自适应估计和跟踪算法.该算法基于LMS(Least Mean Square)迭代算法,利用数控振荡器的输入端加入训练序列,可以实时的估计出DCO的增益值.系统可针对DCO实时增益值来调节环路带宽和优化系统参数,因此该算法可先显著的提高数字锁相环的相位噪声性能.

2 全数字锁相环的基本结构和工作原理

如前文所述,基于全数字锁相环的优点,越来越多的通信雷达系统都使用全数字锁相环结构.图1是一个常见的小数分频全数字锁相环的系统架构图.该锁相环主要由时间时数转换器(TDC,Time to Digital Converter)、数字环路滤波器(DLF,Digital Loop Filter),数控振荡器(DCO,Digital Controlled Oscillator)及多模分频器(MMD,Multi-Mode -Divider)四部分组成.在如图1所示的锁相环结构当中,DLF输出的误差控制信号是离散的数字信号,而非模拟电压.因此,DCO受控输出的电压也是离散的而非连续的数字信号.除了DCO以外,其他锁相环组成部件也全部采用数字电路实现.

当锁相环工作在频率综合(非调制)模式下,锁相环将产生非调制的高频信号.而此高频信号正是由数控振荡器DCO产生的,其瞬时输出频率的平均值由频率控制字(FCW,Frequency Control Word)精确控制.而DCO的步长信息,也就是DCO可被调节的最小输出频率值,也可被称为DCO增益,K_DCO,正是本文算法所要估计的变量.公式(1)显示了,当锁相环在锁定状态下,输出频率f_lock,与DCO的操作频率fC,频率控制字y(k),以及DCO增益KDCO之间的关系

flock(k)=fC+y(k)*KDCO (1)

DCO输出的高频信号被多模分频器MMD 提供的数值来进行划分,划分后的输出信号仍然是一个时钟信号,将被送往时数转换器TDC与参考时钟(Reference Clock)来进行比较.由于输出频率相与参考频率之间的比值通常不是整数,因此提供给MMD的数值也会被分为整数部分和小数部分.整数部分将被直接送给MMD,而小数部分则经过一个Σ-Δ调制器之后再送给MMD.

TDC在锁相环中起到了数字鉴相器的作用,通过比较MMD的输出信号和参考时钟信号之间的时间差,并将其归一化为一个反映相位差的数字信号.此参考时钟为26MHz,由本地振荡器提供.TDC输出信号将被进一步输入到数字环路滤波器DLF.

DLF通过控制滤波器的增益来调整数字锁相环的带宽大小,在环路中对输入噪声起到抑制作用.且对锁相环的校准速度(即锁相环的收敛速度)和输出信号的精度起到调节作用.为了提高DCO的精度,DLF的输出将会分为整数部分和小数部分.整数部分经过采样之后直接作为DCO的输入,而小数部分将通过Σ-Δ噪声抑制器后再输入DCO.此Σ-Δ噪声抑制器也是一种Σ-Δ调制器,其主要原理是产生高频输出的整数序列,而此序列的平均值恰好等于低频的小数部分的值.Σ-Δ噪声整形技术通过速度换取精度,降低了对DCO设计电路的要求,是实现高精度DCO的一种有效方式.环路的输入信号通常为时间连续的信号,而锁相环的输出信号,也就是数控振荡器的输出信号为周期性的高频脉冲序列,其周期可调,并且受到数字滤波器的输出信号的控制.

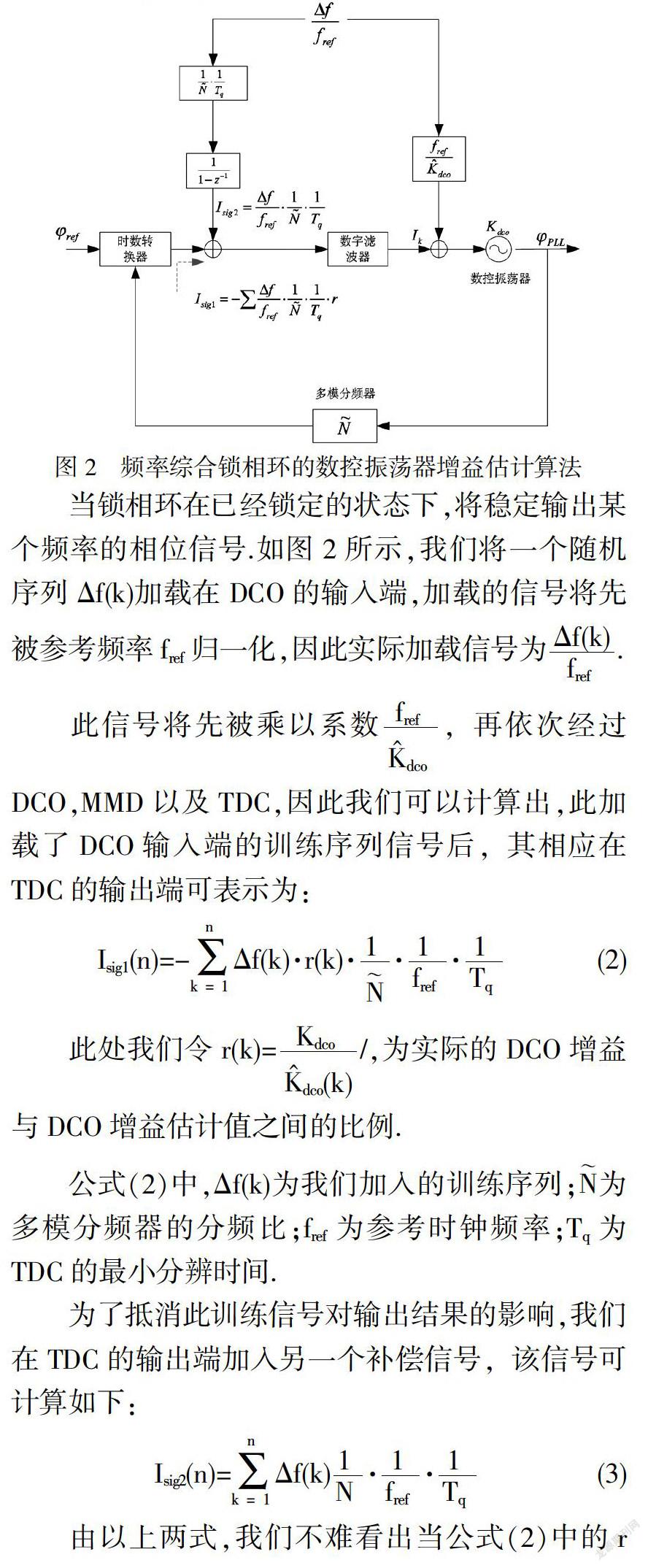

3 DCO增益估计算法

本文提出了一种基于训练序列的数控振荡器增益估计与跟踪算法.

由此我们不难计算出,由于DCO误差而引起的时数转换器输出的相位误差为

由于DCO的增益是随时间实时变化的,这里我们目标就是希望我们的跟踪算法能够实时的跟踪和估计出DCO的增益值,以便可以实时的调节环路滤波器的增益,以使得整个环路滤波器的增益值都能达到最优化,从而提高锁相环的噪声性能.

把上述推导带入LMS自适应滤波算法[2]

4 DCO增益估计算法的Z域模型分析

图3为PLL系统的Z域模型,我们将从Z域来对算法进行分析.如图3所示,通过对上述算法的分析,可以看出此算法通过在DCO的输入端和TDC的输出端各加入两个信号,前一信号为训练序列,后一信号为补偿信号.该加入的信号将对PLL的输出信号产生影响.

5 仿真结果

作者将此算法在全数字锁相环Matlab仿真模型中进行了模拟,同时在仿真模型中加入了模拟噪声源.该仿真模型对如图1所示的锁相环结构中的所有模块进行了建模,并考虑了系统内各模块采样率的转换.系统参数设置如下:DCO实际增益值Kdco为70KHz/LSB;锁相环输出目标频率flock为3.7964 GHz;锁相环参考时钟频率为26MHz;TDC增益Tq为2ps;MMD分频比均值为146.05.参考时钟噪底:-140dBc/Hz.TDC模拟噪声设置为:噪声下限-138 dBc/Hz;1KHz频偏处噪声-128dBc/Hz.DCO模拟噪声设置为:20MHz频偏处噪声-153dBc/Hz,10kHz频偏处噪声-80dBc/Hz.

图4显示了算法自适应跟踪DCO增益的過程.在仿真中,我们设定PLL在已锁定模式下工作,此时因外界干扰或物理条件的变化,仿真模拟DCO增益出现了约30%左右的偏差,系统利用本文设计的DCO增益估计算法来进行纠偏,测试算法的纠偏能力.

在使用本文设计的算法后,如图4所示,其横坐标表示了采样点,而纵坐标表示了DCO的增益值,该算法大约在3000个采样点后收敛到绿色虚线框内(2%错误,即我们的可接受范围).因采样率为26MHz,由此可推算出大约3000*1/26e6=115微秒后,算法将DCO增益控制在与实际值相差在2%的范围内.

如图4所示,该算法采用了收敛步长可调的方案.在算法的一开始,采用较大的步长μ0,以实现更快的收敛;在估计值接近目标后,使用一个小的步长μ1;当结果在较小幅度发生变化时,将使用更小的μ2来提高估计结果的准确性.此方案兼顾了收敛的速度和估计值的准确率.由仿真结果可见,算法达到了预期的目标.

图5显示了DCO随温度漂移变化的特性.其横坐标为DCO的频率控制字y,而纵坐标表示了DCO输出的频率值f.一旦系统设定了输出的锁定频率flock,那么如公式(1)所示,在DCO特性曲线上,当随温度从T1变化到T2、T3...,DCO的频率控制字y也将从y1变为y2,y3......,以保持PLL输出频率依然为锁定频率flock.可见,随着温度的变化,也将会带来DCO的输出控制点,也就是公式(1)中的fc的变化,因此DCO增益也将从k1变化为k2,k3.......所以,在锁相环工作模式下,我们仍然需要检测算法对DCO增益变化的跟踪能力.

图6显示了DCO增益估计和跟踪过程.如图6所示,其横坐标表示了采样点,而纵坐标表示了DCO的增益值.在系统仿真的一开始,我们假设DCO增益估计值与实际值存在30%左右的偏差,系统利用本文设计的DCO增益估计算法来进行跟踪估计.如图示,该算法大约在3000个采样点(3000*1/26e6=115微秒)后收敛到绿色虚线框内(2%错误,即我们的可接受范围).然后,系统开始模拟温度的持续变化而造成的DCO增益的持续变化.如图6示,系统在大约11000个采样点开始,直到30000个采样点附近,DCO增益发生阶梯式变化(图中的黑线阶梯线为DCO的实际增益值),而我们的跟踪算法可以持续跟踪并估计出DCO的增益值(图中蓝色曲线所示),且始终在2%错误框内,即我们的可接受范围内.相关错误率在大约0.7%左右,而标准方差在1.8%左右.

图7显示了当PLL在锁定状态下,未启用以及启用了本文所提出的算法的PLL的输出频谱 (此仿真中,我们设置的分辨率带宽为30kHz).如图7显示,左图为未使用DCO增益估计算法时,RMS相位误差约为0.99°,RMS EVM约为1.73%;右图为使用了DCO增益估计算法后的频谱,RMS相位误差约为0.68°,RMS EVM约为1.19%.结果表明,该算法在准确估计DCO增益的后,优化了PLL的相位噪声性能.

6 结论

本文提出了一种针对全数字锁相环中数控振荡器增益的自适应估计和跟踪算法.该算法基于LMS(最小均方)迭代算法,在DCO的输入端加入了一个训练序列,并在TDC的输出端对此信号进行了抵消和补偿.我们利用该训练序列可以实时并有效的估计出DCO的增益值.同时,为了既提高算法的收敛速率和精确度,我们使用了可变步长的机制.仿真结果表明,我们可以在极短的时间里将DCO的增益值控制到与实际值十分相近的范围内,还可以有效的跟踪和估计DCO的增益值.该算法经过验证可显著的提高数字锁相环的相位噪声性能.

参考文献:

〔1〕P. Gould, J. Lin, O. Boric-Lubecke, C. Zelley, Y.-J. Chen, and R.-H. Yan, “3V GSM base station RF receivers using 0.25μm BiCMOS,” IEEE Trans. Microwave Theory & Tech., vol. 50, no. 1, pp. 369-376, January 2002.

〔2〕R.B. Staszewski, J. Wallberg, C-M Hung, G. Feygin, M. Entezari and D. Leipold, “LMS-Based Calibration of an RF Digitally Controlled Oscillator for Mobile Phones,” IEEE Trans. Circuits and System –II Express Brief, pp. 225-229, March 2006.

〔3〕Nicola Da Dalt, “Theory and Implementation of Digital Bang-Bang Frequency Synthesizers for High SpeedSerial Data Communications,” PH.D dissertation, Rheinisch-Westfalischen Technischen Hochschule Aachen, Feb 2007.

〔4〕R. B. Staszewski, D. Leipold, and P. T. Balsara, “Just-in-time gain estimation of an RF digitally controlled oscillator for digital direct frequency modulation,” IEEE Trans. Circuits Syst. II, Analog Digital Signal Process, vol. 50, no. 11, pp. 887–892, Nov. 2003.

〔5〕C. Joubert, J.F.Bercher, T.Divel,P.Baudin, “Contributions to the analysis and design of an ADPLL,” PH.D dissertation, Rheinisch-Westfalischen Technischen Hochschule Aachen, Feb 2007. ICECS '06,IEEE International Conference on Electronics, Circuits and Systems, pp.322 – 325,Dec 2006.

〔6〕吴渤翰,盖伟新.一种在全数字锁相环中进行振荡器增益估计的新算法[J].北京大学学报(自然科学版),2014(4).

〔7〕趙信,潘天锲,王飙.一款高精度数控振荡器设计与实现[J].计算机工程与科学,2018,40(2).