基于NanEye 2D微型图像传感器的数据采集IP核设计

2019-09-09石汶奇干钰静黄光明

石汶奇,干钰静,黄光明

华中师范大学 物理科学与技术学院,湖北 武汉 430079

引言

近 年 来, 随 着CMOS(Complementary Metal Oxide Semiconductor)图像传感器技术的发展,越来越多廉价且图像效果优良的CMOS 传感器芯片诞生。新兴的CMOS 传感器逐渐取代一些传统CCD(Charge Coupled Device)图像传感器被广泛应用于医疗、安保等各个行业和领域[1-3]。

德 国Awaiba 公 司 设 计 的1 mm×1 mm×1.7 mm,250×250 像素的小封装、低功耗、异步通信的CMOS 微型图像传感器NanEye 2D,体积微小且具有优良的EMC 特性[4-5]。该摄像头在安保、医疗、科学研究和生物测定等有特殊要求的领域具有很大的开发和应用前景[2-3,5]。但是NanEye 2D 特有的4 线接口、异步通信模式以及其自身内部串行数据输出时钟存在±20%的抖动[6],这使得我们对NanEye 2D 传感器数据的采集变得比较困难。再加上目前国内外并没有NanEye 2D 摄像头数据采集方面相关的公开的应用研究和应用文献,使得NanEye 2D 摄像头的开发和应用变得更加困难。

为了解决这一技术难题,本文对NanEye 2D 摄像头的4 线接口、异步通信模式以及内部时钟±20%的抖动等进行了分析,在Altera 公司的FPGA 平台上设计并实现了一个针对NanEye 2D 摄像头数据采集的定制IP 核。该设计对于进一步开发NanEye 2D 图像传感器具有一定的借鉴意义。

1 NanEye 2D传感器及原理分析

1.1 NanEye 2D微型图像传感器

NanEye 2D 全数字摄像头是2016 年欧洲Sensor Expo & Conference 的创新银奖作品[7]。NanEye 2D 传感器是一个提供真正的片上系统的摄像头。该传感器内的片上系统具有10 位ADC(Analog-to-Digital Converter)转换功能,自定时顺序读出功能以及串行位数据LVDS(Low-Voltage Differential Signaling)传输功能[7]。NanEye 2D 摄像头能够以42~55 Fps 的帧速率通过4 线的接口传输250×250 分辨率的图像。帧速率大于40 Fps 使得该摄像头的图像能够流畅地同步到绝大多数显示接口上。此外,Awaiba 特有的4线数据接口技术允许NanEye 2D 摄像头的传输线在远端没有任何辅助部件的情况下可以达到3 m 的长度。由于这种接口的低能量损耗,摄像头不需要复杂的屏蔽来满足EMC(Electro Magnetic Compatibility)规范接口耗散[8]。该摄像头可应用于安保、医疗、科学应用和生物测定等领域。

1.2 NanEye2D图像传感器工作时序分析

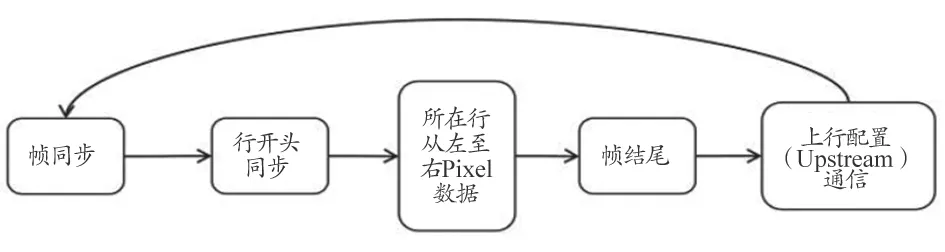

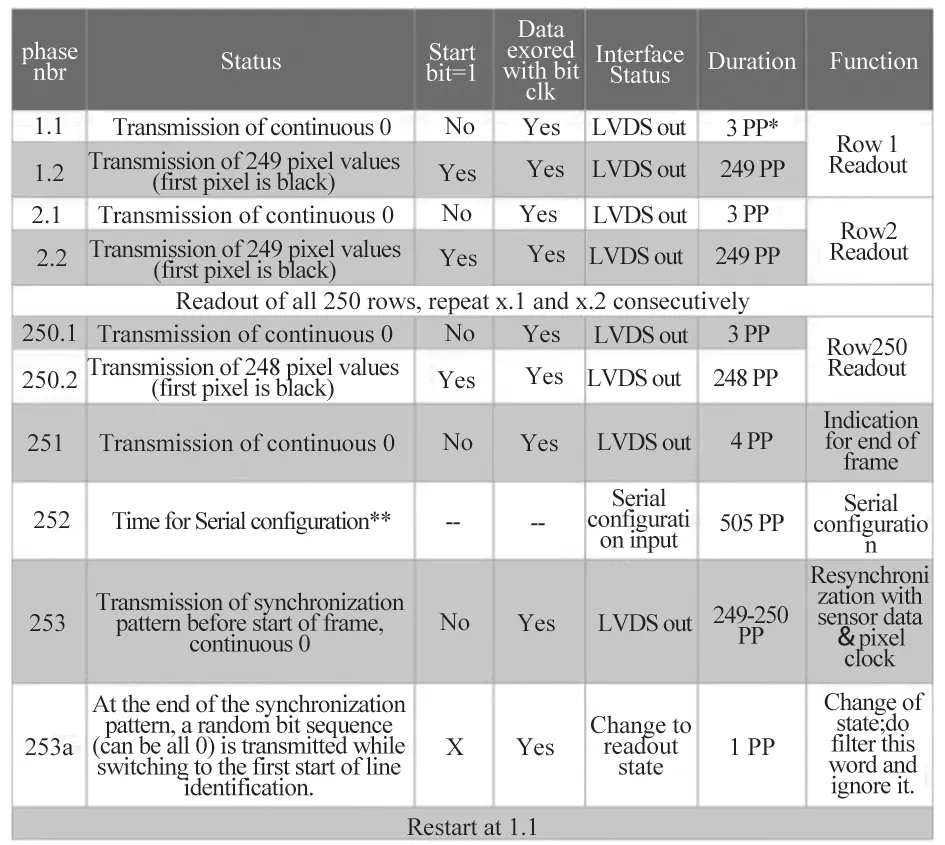

如图1 和图2 所示,NanEye 2D 图像传感器具体的工作时序为:从第一行开始,每一行都有一段3 PP(1 PP 为12 bit 数据)的行开头,接着是每一行的pixel 数据,如此反复,直到完成传输所有pixel 值。当完成250 行pixel 数据的传输后,系统进入phase nbr 251 帧结尾阶段,连续传输4 PP 的0;之后进入phase nbr 252 阶段(即NanEye 2D摄像头寄存器上行配置阶段),外部可以通过差分数据线对摄像头的有关寄存器进行配置。配置结束后,进入phase nbr 253 数据时钟同步阶段和phase nbr 253a 状态跳转阶段并开始新的一帧图像数据传输[6,8]。在每个角落都有两个具有电气特性的黑像素和两个电气上饱和的像素,用于检查接收数据的一致性[6,8]。

图1 内部自定时工作流程示意图

图2 数据流协议

1.3 NanEye2D图像传感器数据格式分析

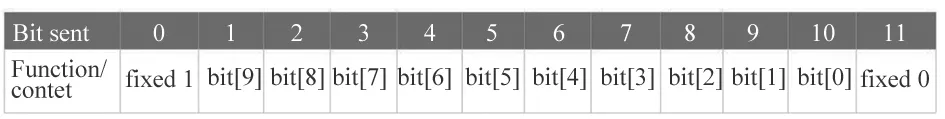

摄像头的数据格式为12 bit,其中数据头部是固定的“1”,尾部是固定的“0”,中间10 bit 为有效的pixel 数据[6,8]。pixel 数据格式如图3 所示。

图3 pixel数据格式

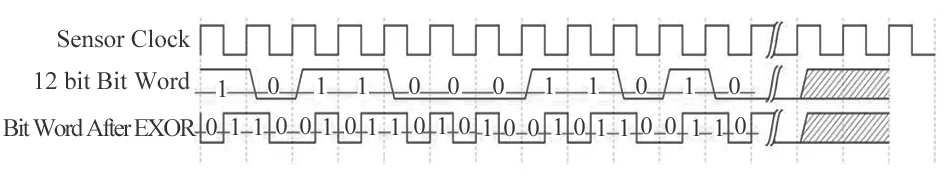

如图4 所示,摄像头的数据在向外传输时会经过内部时钟的异或,将1 bit 的数据变成两位的数据,即进行了曼彻斯特编码,其中“01”表示“1”,“10”表示“0”。例如:有效pixel 数据“0110001101”,包含数据起始位和结尾位为“101100011010”,经过异或后为“0110010110101001011 00110”[6,8]。

图4 数据异或编码(曼彻斯特编码)

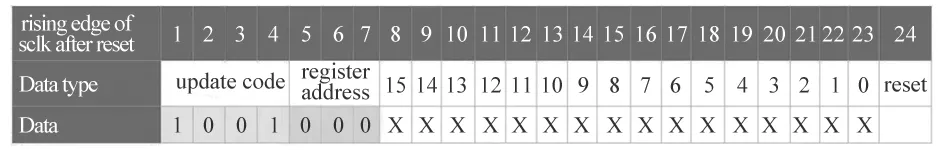

摄像头进行上行配置阶段的数据格式如图5 所示,寄存器配置的数据为16 bit 的格式。对摄像头寄存器进行写操作的顺序如下:首先,向寄存器发送4 bit 的 update code(“1001”),接着发送3 bit 的register address(“000”),最后发送16 bit 的寄存器配置数据。当不对寄存器操作时,寄存器默认值为“1010011000000010”[6,8]。了解NanEye 2D 图像传感器的数据传输方式后,通过过采样监测数据流,对数据进行曼彻斯特解码后找到对应的帧同步、行同步、上行配置阶段等就可以对有效的pixel 数据进行提取,从而获取原始的帧图像数据。

图5 上行寄存器配置数据格式

2 NanEye 2D数据采集IP核设计

2.1 IP核总体介绍

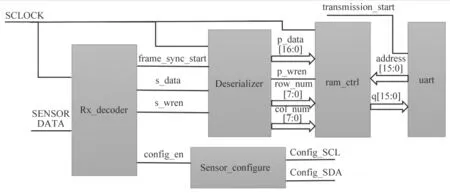

整个IP 核模块内部主要由Rx_decoder(串行数据接收和解码模块)、Deserializer(串行数据转并行数据模块)、Sensor_confi gure(上行配置模块)、ram_ctrl(存储控制模块)和uart(UART 传输接口模块)五个部分组成(图6)。

图6 NanEye 2D摄像头数据采集IP核数据流框图

在该设计中,数据采集主要由两部分完成。其中一个部分是Rx_decoder 模块,该部分负责摄像头的串行信号的接收,过采样解码恢复获取原始的串行有效数据;另一部分是Deserializer 模块,该模块实现对Rx_decoder 部分获得的原始串行数据的行开头、帧结尾的识别、pixel 有效10位串行数据的提取,串行数据转换为并行数据输出和当前帧的行列数计数。

ram_ctrl 模块负责将解串后的并行数据存储到RAM对应的地址中。通过外部按键产生传输开始信号,触发UART 的数据传输。IP 核通过uart 将一帧完整的数据上传到上位机,供后面进一步处理和分析。Sensor_confi gure 模块则负责在数据上行配置阶段通过I2C 通信协议对NanEye 2D 传感器的寄存器参数进行配置。本设计中的测试,NanEye 2D 寄存器的参数均为默认值。

2.2 Rx_decoder模块的实现

Rx_decoder 模块是数据采集IP 核部分最重要的模块,本模块负责对摄像头传感器输出的曼彻斯特编码的数据流进行接收和解码。此外,Rx_decoder 模块还通过一直观察输入信号,检测和产生帧开始信号“frame_sync_start”和上行配置开始信号“confi g_en”(该信号供Sensor_confi gure上行配置模块使用)。

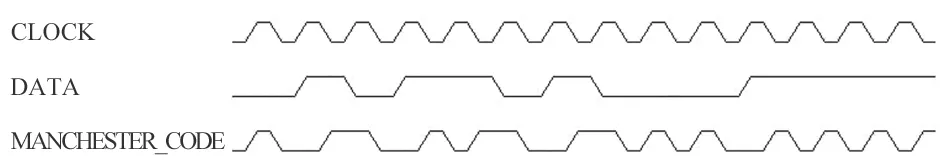

曼彻斯特编码表示串行数据(DATA)与其串行时钟(CLOCK)的逻辑组合(图7)。一个时钟周期信号至少改变一次其高低电平状态,这使得接收器在不需要发送器同时发送时钟信号和数据信号的情况下,能够正确对齐数据流。被接收器解码的数据流可以看作只有两个可能的高或低持续时间的脉冲序列,一种是T_short=0.5 T_Bit(这里也称为“半位周期”)和T_long = T_Bit(这里也称为“全位周期”)。

图7 曼彻斯特编码的数据流

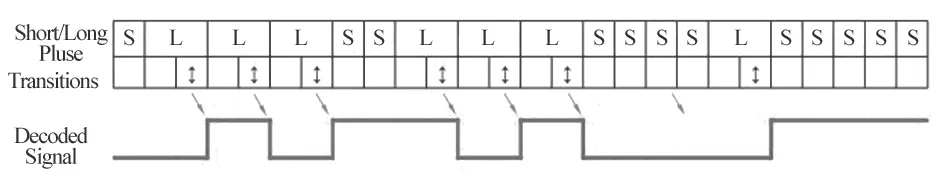

为了解码摄像头输出的曼彻斯特编码后的信号,接收机需要不断测量两次电平转换之间的时间。在这种测量的基础上,解码器必须区分最后的电平转换是由短脉冲(S)引起的还是长脉冲(L)引起的。短脉冲总是意味着原始数据流没有改变电平状态,而长脉冲意味着在原始比特流内发生了电平转换。将上面例子中的曼彻斯特编码的数据流(图7)应用到接收器应该最终产生图8 中所示的脉冲序列。每个长脉冲都会导致解码输出信号改变其状态。如果数据信号的最初状态是已知的,原始数据的比特流就可以如图8 所示重构。在这个例子中,NanEye 图像传感器发送的每行的行开始,原始数据的初始状态信号都是“0”。

图8 曼彻斯特解码的数据流

由此可知,正确判定还原信号脉冲时间的长度是正确解码恢复原始数据的必要条件。但是由于传感器内部设计的不足,该时钟会根据变化的温度或电源电压等条件产生漂移,即其内部异或时钟Sensor Clock 存在±20%的抖动,该时钟发生器的频率并不完全已知。Rx_decoder 必须通过使用它自己的采样时种SCLOCK,将传感器的输出信号作为异步信号进行采样。由于这个原因,选择适当的采样频率是很重要的。合适的采样频率保证了通过分析计数器总是可以区分长脉冲值和短脉冲值,但是又不能对FPGA 芯片要求太高[9-11]。为了解决这个问题,我们调用了Altera FPGA 的双边沿采样IP 核模块,通过FPGA PLL IP 核模块将50 MHz 时钟倍频到200 MHz 来实现400 MHz 的采样效果[12-13]。另一方面为了能够适应摄像头的时钟抖动,我们设计了一个脉冲宽度计数模块。将上一帧数据的脉冲宽度统计值用于下一帧数据的长脉冲和短脉冲的判定阈值,从而实现判定门限值的动态调节。

这样设计的Rx_decoder 模块能够正确稳定地对NanEye 2D 摄像头数据进行采样和解码恢复,同时产生位有效信号。

2.3 Deserializer串行数据转并行数据模块

Deserializer 模块用于将Rx_decoder 部分输出的串行数据转换成10 位并行的数据,并输出存储到ram_ctrl 部分。Deserializer 模块将数据串转并的主要组成部分是一个12 位移位寄存器。该模块通过该移位寄存器实现对Rx_decoder解码输出的比特序列的串并转换。每当串行位数据有效信号s_wren=“1”时,移位寄存器的数据向高位移一位。同时,移位计数器的值会“+1”。当移位寄存器中的数据被识别为有效的pixel 数据值(“1xxxxxxxxxx0”)时,有效的10 位pixel 数据将被提取出来,同时产生输出使能信号,存入到ram_ctrl 模块的片上RAM 中[14]。当收到的完整的像素点值,但其起始位不为“1”或是结束位不为“0”时,表示该像素点值出错,错误标志位error 被激活。

该模块的另一个功能是使用解码的比特流,在正确的时间点激活信号行同步和行结尾信号,通过计算列和行的数量,来检测由NanEye 传感器输出数据的行和帧边界。

结合上面的模块,通过状态机等逻辑我们可以对图像有效数据进行正确提取。值得一提的是,传感器实际上每行只发送249 个像素。最后一行(第250 行)只包含248个像素。状态机在设计时已经考虑到该问题。当错误标志位信号error 被激活时,上述有关信号都被重置并且重新开始解串,这样保证了每帧的第一行始终被正确接收。

3 实验测试

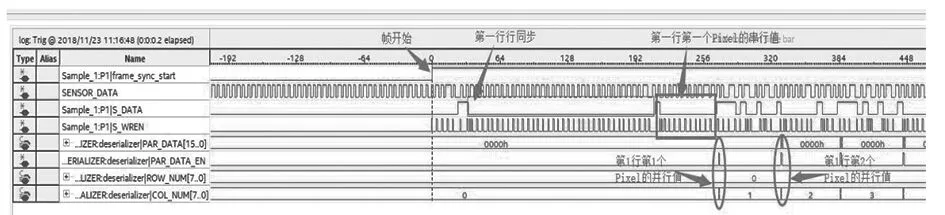

3.1 IP核SignalTap II测试

IP 核编译后接上NanEye 2D 传感器在SignalTap II(Altera 公司的Quartus II 开发软平台软件自带的嵌入式逻辑分析仪)上测试,观察到的信号如图9 所示。结果表明,该IP 核可以每秒44 帧正常识别和提取摄像头的帧同步、行同步、列同步和pixel 值等数据,实现了设计的目标功能。

图9 IP核SignalTap II测试结果

3.2 图像数据上位机显示测试

IP 核正常获取到NanEye 2D 的帧图像数据后,将IP核采集到的帧图像流通过UART 上传到PC 机上,经过软件Bayer 解码算法[15-16]恢复后得到的结果图(图10a,手机打光,偏黄)。图10b 为手机拍摄的实物图(白色日光灯照射,由华为荣耀10 拍摄)。对比图10a 和图10b,虽然获得的图像整体较暗且色彩饱和度不够,但结果表明IP 核采集到的帧图像数据经过软件解码算法后可正确显示流畅的视频流,本IP 核获取的数据是正确连续且稳定可靠的。

图10 图像数据显示测试

4 结论

本IP 核作为NanEye 2D 微型图像传感器的数据采集部分,负责完成图像数据的采样和帧数据提取。经测试结果证明,该IP 核运用在NanEye 2D 摄像头传感器上可以每秒44 帧的速率采集和提取图像数据。该速率大于NanEye 2D 理论的最小帧速率42 Fps,小于最大帧速率55 Fps。采集到的帧图像数据通过UART 接口上传到PC 机上,经过软件汉密尔顿Bayer 插值解码算法[17]后可以显示流畅的视频流。结果表明,本IP 核很好地解决了NanEye 2D 图像传感器的数据采集问题。本文中的研究成果为后续开发基于NanEye 2D 微型图像传感器的医用内窥镜成像系统奠定了重要基础。