一种二次雷达射频收发一体机设计

2019-08-27倪文飞鲁长来

倪文飞 谢 迟 夏 丹 鲁长来 水 泉

(安徽四创电子股份有限公司 合肥 230000)

0 引言

二次雷达[1]与飞行器通过询问-应答工作模式进行飞航信息交互,二次雷达询问信号以特定模式体现,如标准询问模式、联合询问模式及S模式[2]。传统二次雷达接收系统将频率1090MHz应答信号通过模拟下变频转变为60MHz中频信号并进行数字基带处理,同时需要合成1030MHz询问信号及旁瓣抑制信号,设备较复杂。收发设备一般通过高速光纤传输数据,而在实时传输模式下,设备量大,并且随着信号通道增加,光纤传输可靠性将会下降。目前小型化、可移式已成为二次雷达收发设备发展趋势,二次雷达对射频采样及高速信号合成存在极大需求,同时异步传输可简化传输设备。基于以上目的,提出了一种射频收发一体机,通过异步传输实现数据通信。

1 设计思想

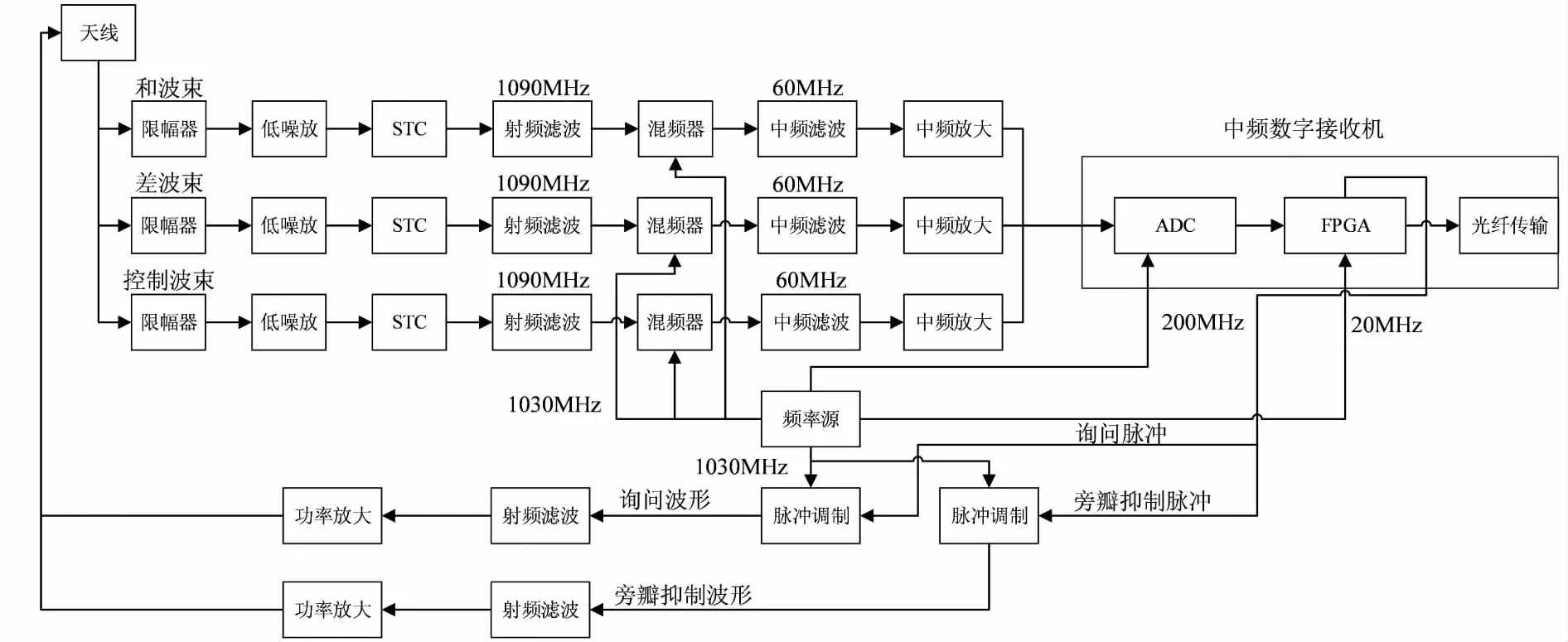

传统二次雷达收发系统如图1所示,和波束应答、差波束应答及控制波束应答[3]经过模拟下变频输出,频率源模块输出3路1030MHz信号至3路模拟混频器,3路60MHz应答信号传输至中频数字接收机[4]进行数字下变频处理[5],模拟通道设计复杂。

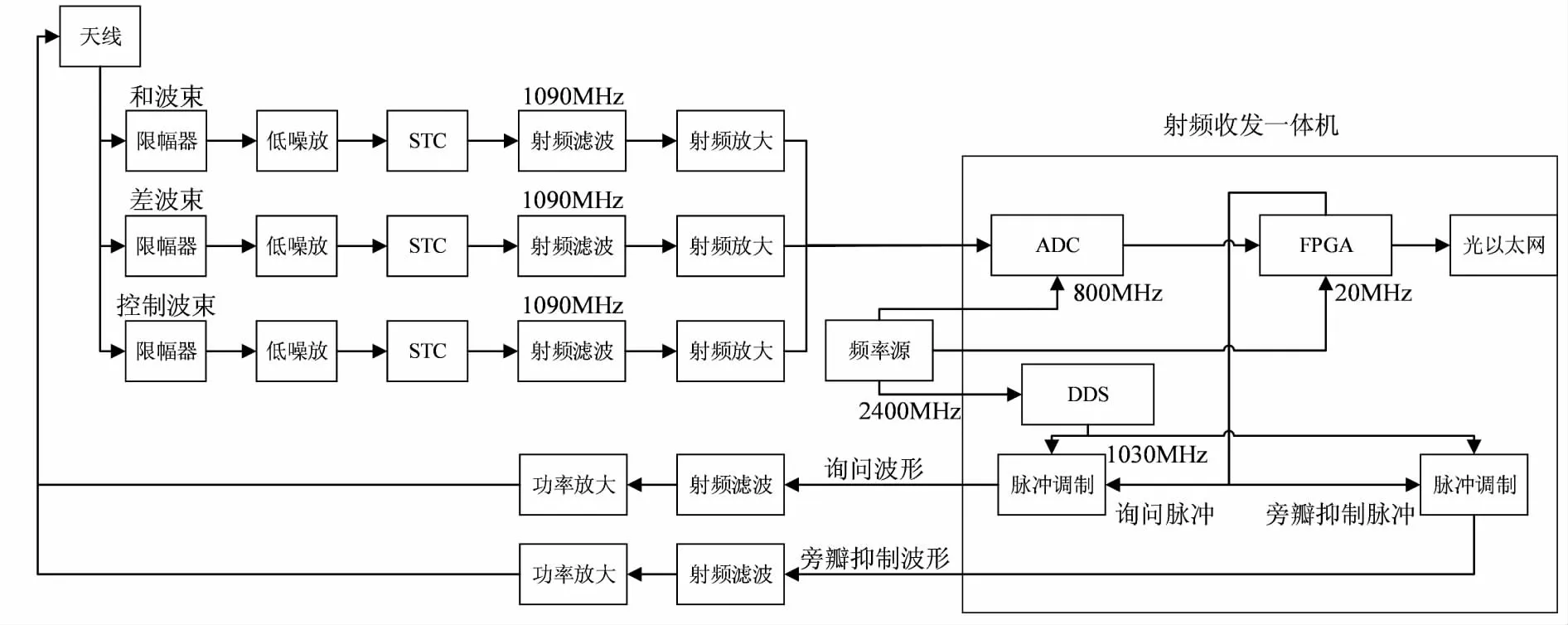

图2为以射频收发一体机为核心的收发系统框图,与图1相比少了3路模拟混频器及3路中频放大器,频率源模块更加简单。图2添加了高速DDS模块,通过高速DDS与调制开关直接合成询问信号及旁瓣抑制信号,直接通过高速ADC对1090MHz应答信号进行模数转换,最终数据通过光吉比特以太网传输。

图1 传统二次雷达收发系统框图

图2 新型二次雷达收发系统框图

2 射频接收设计

射频接收通过高速ADC与FPGA实现[6],高速ADC芯片为TI公司的ADC12D1800RF,芯片以800MSPS采样率对1090MHz应答信号直接进行采样,采样所得数字信号传输至FPGA进行数字基带处理。射频采样特征是高输出数据率,FPGA芯片为Altera的EP4SGX230KF40I3,其最大运算速率455MSPS,如果采样输出信号直接以速率800Mbps传输至FPGA,则无法进行串并转换。ADC12D1800RF支持单通道1:4输出及双通道1:2输出模式。在双通道1:2输出模式下,芯片将输出数据率降至400Mbps,可通过ECM模式将ADC芯片地址0h寄存器设置为2008h实现。

图3为射频接收处理框图,ADC芯片将3路应答信号以采样率400MSPS、中心频率110MHz形式传输至FPGA进行数字基带处理,通过数字下变频将其转变为数据率10Mbps的零中频信号。LVDS_CORE为串并转换模块,可将多路串行数据转换为单路并行数据。在数字下变频中,信号与数字本振混频得到零中频信号,通过CIC抽取滤波器[7]将零中频信号采样率由400MSPS转变为10MSPS,最后通过FIR滤波器进行带内幅度补偿及提高带外抑制,最后得到IQ正交信号。

图3 射频接收处理框图

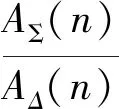

得到IQ正交信号后,需要进行对数运算得到信号幅度值,其次进行幅相比较。式(1)为和波束与差波束幅相比较计算公式,该值直接为软件化处理系统提供幅相标校依据。

(1)

式(1)中,IΣ(n)为AΣ(t)cos(φΣ(n)),QΣ(n)为AΣ(t)sin(φΣ(n)),IΔ(n)为AΔ(t)cos(φΔ(n)),QΔ(n)为AΔ(t)sin(φΔ(n)),其中AΣ(t)及AΔ(t)为幅度信息,φΣ(n)及φΔ(n)为相位信息,因此和波束与差波束之间的幅相比较值可表示为:

(2)

由式(2)可知,当和波束回波与差波束回波保持一致时,幅相比较值为1。

RSLS为副瓣匿影控制[8],它是抑制天线接收副瓣干扰的有效措施,当和波束应答信号幅度高于控制波束时,则该信号来源于天线主瓣方向,应当保留,反之则来源于天线副瓣方向,应当丢弃。 其计算

结果如式(3)、(4)所示:

(3)

(4)

式(3)、(4)中RΔ与RΩ分别为差通道校准系数及控制通道校准系数,通过引入校准系数可更好实现副瓣匿影控制。射频接收产生的幅度信息及标校数据最终通过光吉比特以太网传输至软件化处理系统。

3 射频发射设计

射频发射通过高速DDS及FPGA实现,其作用是产生询问信号及旁瓣抑制信号。DDS芯片以频率控制字为工作依据,通过相位累加实现频率合成[9]。AD9914采用先进DDS技术,连同高速、高性能数模转换器以构成数字可编程合成器。AD9914工作于2.4GSPS采样率,为正确输出信号,FPGA通过SPI总线将DDS内部FTW设置为6dddddddh,并使DDS工作在连续波模式下,最后通过询问脉冲及旁瓣抑制脉冲对DDS输出信号进行调制。

图4 信号产生原理框图

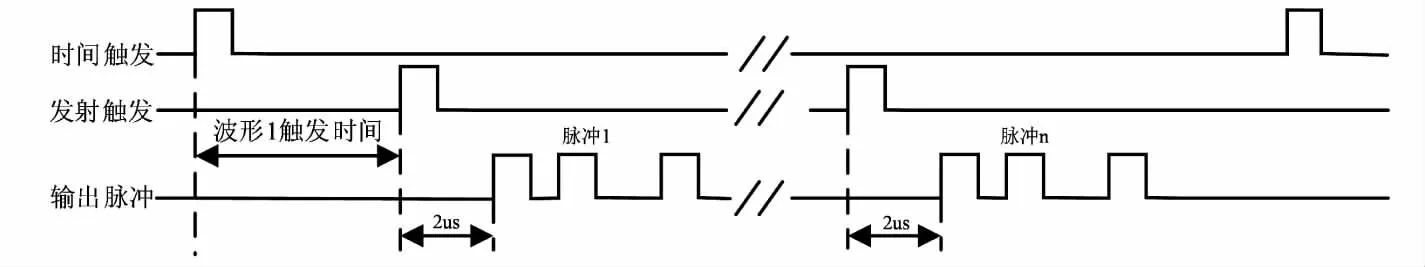

询问脉冲及旁瓣抑制脉冲由FPGA产生,需要在FPGA内部RAM[10]建立一个64×16bit时间周期表和一个1024×16bit脉冲信息表,表中数据由控制计算机发送的控制帧进行写入和更新。FPGA脉冲触发单元读取时间周期表中时间触发参数产生时间触发,脉冲产生单元读取脉冲信息表参数输出询问脉冲、旁瓣抑制脉冲以及发射触发脉冲,发射触发提供时间依据。

图5 脉冲产生时序图

4 光吉比特以太网传输设计

传统收发设备通过光纤将数据传输至光纤采集卡,光纤采集卡将数据输出至服务器,服务器再将数据传输至交换机实现数据共享,传输形式复杂,而异步传输可解决这一问题。在异步传输模式下,数据通过光吉比特以太网传输至网络交换机,直接免去了光纤采集卡,提升了软件化处理功能,文中数据读写通过双口RAM以乒乓操作[11]实现。以太网最大

帧字节为8192,每帧可传输4096个16位数据。数字下变频最终输出3路14位对数视频信号、1路16位幅相校准误差值,原始数据率640Mbps。在设计中,每帧以太网数据包含7998字节数据及50字节数据帧头,四路数据通过4组双口RAM实现读写操作,即在199.9μs时间内,4组双口RAM的A口进行实时数据写操作,双口RAM的B口以时间间隔进行数据读操作并发送,在下一个199.9μs时间内,4组双口RAM的A口以时间间隔进行数据读操作并发送,双口RAM的B口进行实时数据写操作。

图6 实时网络数据包

5 结束语

图7为询问信号频谱图,图8为和波束IQ实测频域图,由最终实测图可知设计实现了射频收发功能。本次论文设计不仅可有效运用于二次雷达,更可应用于L波段航管及风廓线雷达等,并为射频收发一体化提出了确实有效的实施方案。

图7 询问信号频谱图

图8 和波束IQ实测频域图