基于CCSDS标准的卫星遥控LDPC编码方案探讨

2019-07-31王柏岩刘治军王睿叶勉熊晓将韩笑冬

王柏岩 刘治军 王睿 叶勉 熊晓将 韩笑冬

(中国空间技术研究院通信卫星事业部,北京 100094)

遥控链路是实施星上设备状态控制的唯一通道,主要实现遥控指令的接收、解调和译码,帧长较短的遥控指令以每天几次甚至每周几次的频率传输到卫星,因此遥控方案设计需要考虑短指令、低延时、实现简单及高可靠性等特点。现有CCSDS遥控标准[1-2]推荐使用BCH(63,56)编码方案,该方案适合低时延、指令帧较短的遥控系统。随着航天技术的发展,下一代卫星需要使用遥控链路来支持越来越多的用途,例如将更大量的数据传输到卫星以实现在轨软件的更新。因此,采用新的信道编码技术、获得更好的编码增益,是升级现有CCSDS遥控信道编码标准的核心要素。而目前BCH(63,56)编码方案具有以下不足[3]:①遥控信道采用的BCH编码方案较为简单,只能纠正或检测少量比特错误。②BCH编码方案的接收机只能进行硬判决,无法进行软判决,严重限制了编码增益。由于无法获得更好的编码增益,只能通过提高发射端发射功率来确保遥控信息传输的可靠性,但由于卫星设备在尺寸、质量、功耗和效能等方面的限制,不可能无限制提升设备发射功率。对于下一代卫星而言,需通过优异的信道编码方案设计来获得可观的信道增益,有效降低信号解调门限,进而抵消信号在长距离空间传播过程中带来的能量损失。

CCSDS委员会在2014年提出下一代卫星遥控业务[4]需要满足:①比目前CCSDS遥控系列标准更高的遥控速率,遥控瞬时速率应至少在数千比特每秒。②利用现有的发射机和天线系统实现更高的性能,包括降低译码门限和提高编码增益。为此,CCSDS于2015年发布CCSDS 231.1-O-1橙皮书[5],提出了3种性能优异的短码长LDPC码,以替代目前广泛使用的BCH(63,56)码。LDPC码是分组码,具有很优异的译码性能,译码方式是逐比特的迭代算法,在良好的译码方案下其性能甚至要高于Turbo码[6]。目前,LDPC编码方案主要用于下行数传链路,例如:我国嫦娥2号探月卫星和“高分”卫星(下传数据率最高可以达1 Gbit/s),以及实践十号卫星(编码速率为两路并行300 Mbit/s);NASA的“界面区成像光谱仪”(IRIS)任务;在ESA下一代卫星数字视频标准DVB-S2中作为内码(码长为16 200 bit或64 800 bit)。LDPC码的研究主要集中在数传链路和遥测链路[7],其LDPC编码方案设计无法满足遥控链路短指令、低延时、实现简单、高可靠性的特点,因此需要针对下一代卫星遥控链路的业务需求设计合适的LDPC编码方案。

本文将遥控指令分为短指令模式与内存上注指令模式,针对2种不同指令模式设计不同的LDPC编码方案,可以获得更好的编码增益,提高遥控链路的可靠性。在此基础上,通过仿真分析给出了本文中不同指令模式下LDPC编码方案的误码字率曲线与漏检错误率曲线,对比了编码性能。针对本文的LDPC编码方案可行性分析表明,此方案适用于卫星遥控协议体系,可以提高卫星遥控业务的可靠性。

1 LDPC编码方案探讨

在卫星遥控通信中,信道编码技术是保证通信可靠性的必要手段。目前,在轨卫星越来越多,环境也越来越复杂,遥控的业务需求不断变化,越来越多的大数据量业务需要通过这条链路传输到卫星(例如在轨软件更新)。本节根据不同的遥控业务模式探讨CCSDS遥控标准推荐的LDPC编码方案,以期获得更好的编码性能,提高遥控可靠性。

1.1 遥控LDPC编码模式分析

为了应对复杂多变的业务需求,根据卫星遥控链路的业务需要[8],可以将遥控指令分为两大类,如表1所示。

短指令模式是以低码速率提供数据长度约100 bit的短指令,遥控码速率为1~4 kbit/s,所占用的频段为S或X频段。由于速率较低,此模式下带宽不受限。短指令大部分是对卫星能源、姿态的控制指令,以及重要载荷的指令,因此发出错误指令可能是灾难性的。目前,未采用信道编码时,遥控链路预算余量约为1.5 dB,而BCH编码方案只可以提供1~2 dB的编码增益,余量均较小。在实际任务中,采用BCH编码方案时没有出现普遍丢帧的情况,主要是因为天地设备也均留有较大的裕量,尽管如此,还是应该进行理论计算,尽量提升编码增益,而不是依赖设备自身的裕量。因此,针对短指令模式,CCSDS 231.1-O-1橙皮书于2015年推荐3种码长的LDPC短码,其性能优于目前广泛使用的BCH码,可以保证获得更好的可靠性。

内存上注指令多用于卫星软件在轨更新,上传的数据量较大,长度约为4000 bit,因此需要较高的码速率(最高可达1 Mbit/s)来缩短内存上注的时间。因为码速率较高,可以借用载荷业务链路完成卫星遥控指令注入,所占用的频段可以为Ka或Ku频段。在此模式下,受限于天线的发射功率,较高的码速率所需要的带宽也较大,因此需要较高的编码效率。针对内存上注指令模式数据量大、速率高的特性,可以参考CCSDS 131.0-B-2蓝皮书于2011年发布遥测信道编码标准中编码效率为223/255的LDPC编码方案。

1.2 短指令模式中的LDPC编码方案

根据表1中所示,对于帧长较短的遥控指令,需要选择码块长度在100 bit左右且拥有良好纠检错能力和较低译码复杂度的编码方案。当采用低编码效率的编码方案时,需要更多的迭代来保证正确的译码,这样也会相应增加遥控接收机信号捕获锁定的难度,因此,本文对编码增益和系统复杂度折中考虑,编码效率建议设置为1/2。CCSDS 231.1-O-1橙皮书中推荐了3种码长的LDPC短码,这3种码率为1/2的LDPC(n,k)短码分别为LDPC(128,64)码,LDPC(256,128)码,LDPC(512,256)码,其中n代表编码后的码块长度,k代表有效信息位长度。

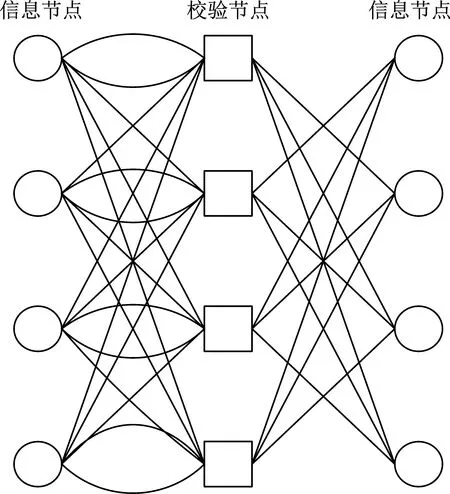

LDPC码最初是用一个稀疏校验矩阵来定义的线性分组码,后来将LDPC码的校验矩阵H对应到被称为Tanner图的双向二分图上。Tanner图上的两部分节点分别为信息节点和校验节点,它们之间的连接线称为“边”。若第j个信息节点与第i个校验节点有边相连接,则校验矩阵中的H(i,j)=1,否则为0。在Tanner图中,与节点i相连的边称为节点i的度。图1给出了编码效率为1/2的LDPC码的Tanner图[9],其中信息节点用圆圈表示,校验节点用方块表示。信息节点的度分布为非正则的,每个信息节点的边数平均为4个。这样设计可以降低短码长LDPC的误码平层,但代价是提高了信噪比的门限和译码复杂度。

图1 编码效率为1/2的LDPC码Tanner图Fig.1 Protograph for rate of 1/2 LDPC codes

根据图1所示的Tanner图构建LDPC(128,64)码,LDPC(256,128)码,LDPC(512,256)码[10]。这3种LDPC码字的校验矩阵H由m×m的子矩阵构成,其中m=k/4=n/8。

(1)

(2)

(3)

式中:Im和0m为m×m的单位矩阵和零矩阵;Φk为单位矩阵Im循环右移k位后的矩阵;⊕为模2加法运算。

LDPC编码过程实际上是输入信息序列和生成矩阵G的乘积。为了完成上述3种LDPC编码,必须先通过校验矩阵H求得生成矩阵G,然后利用生成矩阵进行编码。

上述3种码长的LDPC短码生成矩阵都可以由校验矩阵通过运算给出,其计算步骤如下。

(1)将校验矩阵H分为前4m列和后4m列两部分,P是大小为4m×4m的子矩阵,组成了H矩阵的最后4m列,Q是大小为4m×4m的子矩阵,组成了H矩阵的前4m列,即H=[QP]。

(2)计算矩阵W=(P-1Q)T,采用模2运算。

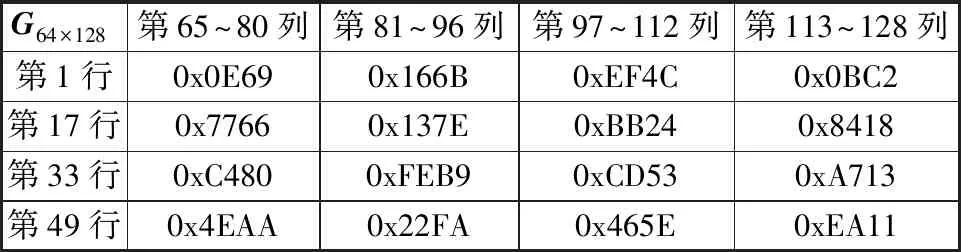

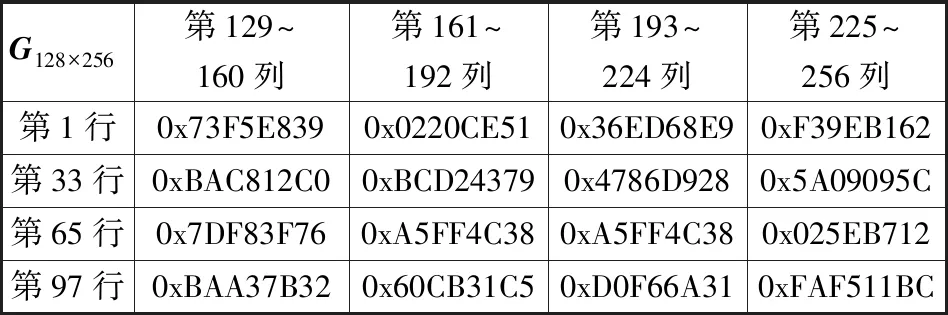

上述3种LDPC码长均较短,其生成矩阵大小相对较小,且具有块循环特性,因此可以采用循环移位的方式构造生成矩阵。表2~4给出了这3种LDPC码的第1行,第m+1行,第2m+1行,第3m+1行的十六进制值。

表2 LDPC(128,64)码生成矩阵Table 2 Generator matrix of LDPC(128,64) code

表3 LDPC(256,128)码生成矩阵Table 3 Generator matrix of LDPC(256,128) code

表4 LDPC(512,256)码生成矩阵Table 4 Generator matrix of LDPC(512,256) code

通过表2~4中的每一行进行循环移位,即可得到CCSDS遥控应用中推荐的3种LDPC码的生成矩阵G。在进行编码时,只需要存储上述表格中的4行十六进制数,因此所占用的存储资源大大减少。

1.3 内存上注指令模式中的LDPC编码方案

由于卫星设计越来越复杂,对于大数据量内存上注的需求不断增加。星载软件需要经常在轨更新,FPGA也需要在轨重复配置。因此,现有的短码字信道编码方案和数据链路协议设计已经无法满足如此大量数据的传输。而长码字的信道编码方案可以获得更大的编码增益,在传输过程中能提供更好的纠检错能力。

通过表1中内存上注指令的特性分析,可以得到如下结论:①内存上注指令需要更长的码块,这样才可以获得更好的编码增益。②编码效率需要折中考虑到带宽和功率的因素。在一定的链路性能条件下,一般通过编码增益的最大化尽可能减小星载发射功率,但是付出的代价是需要提高编码效率,并占用更大的带宽,而编码效率和频谱效率又共同决定了能获得的最大信息传输速率。对于内存上注指令的编码方案设计,可以参考遥测信道编码标准[7]中信道编码方式的设计。该标准中主要规定了5种遥测信道编码方式,包括卷积码、R-S码、级联码、Turbo码、LDPC码。对于大数据量的遥控指令,需要选择编码增益较好且编码效率较高的编码方案,这样可以提高译码的正确性,也会相应减少遥控接收机信号捕获锁定的难度。因此,本文推荐使用码率为223/255的LDPC码。标准中LDPC码采用截断码形式,先产生LDPC(8176,7154)码,其校验矩阵见式(4)。每个Ai,j是一个511×511的循环矩阵。每个32阵列的循环子矩阵的行重为2,即每行中1的个数为2。校验矩阵每行的总行重是32。每个循环子矩阵中第1行中1的位置在表5的第2列被定义,每个随后的行是由前1行的1 bit右循环移位给出。有511个可能位置,由0到510表示。第3列代表校验矩阵中1的绝对位置,有8176个可能的位置,由0到8175表示。LDPC(8176,7154)子码的生成矩阵见式(5)。

(4)表5 LDPC(8176,7154)码循环矩阵Table 5 Circulants of LDPC(8176,7154) code

(5)

LDPC(8176,7154)码可截断生成LDPC(8160,7136),编码效率为223/255。其构造方法为:①编码器接收长度为7136 bit的传送帧作为输入;②将18个0放置在待编码(U)的7136 bit信息之前,产生一个7154 bit元素的行向量;③这个向量乘以式(5)定义的生成矩阵,产生一个8176 bit的向量,这个向量由18个0、7136个信息比特和1022个效验比特(P)组成;④丢弃这个向量中的18个前导0,在末端附加2个0,就产生了一个8160 bit的码字。

18个填充比特、信息比特、校验比特和2个填充0比特的格式,如图2所示。

图2 LDPC(8160,7136)码格式Fig.2 Format of LDPC(8160,7136) code

2 LDPC编码性能仿真分析

为了研究LDPC码在遥控应用中的性能,本节给出了LDPC码在高斯白噪声信道条件下的性能曲线,采用经典的置信传播(BP)译码算法进行译码,译码过程中最大迭代次数设置为100次。本次仿真的3种LDPC短码码率均为1/2,编码前信息序列长度分别为64,128,256,LDPC(8160,7136)码率接近223/255,编码前信息序列长度为7136。图3和图4给出了3种LDPC码的误码字率和漏检错误率曲线。其中,未编码数据的误码字率用虚线表示,由于未编码系统中所有的错误都无法被检出,因此2张图中的虚线相同。对于CCSDS遥控信道编码标准推荐采用BCH(63,56)码,根据系统设计需求,BCH译码可以工作在检错与纠错2种模式下[11-12]。当工作在检错模式下,可以实现3 bit的检错;当工作在纠错模式下,可以实现1 bit的纠错和2 bit的检错。图3中检错模式误码字率曲线在未编码曲线的右边,是因为检错模式没有纠错能力,纠错模式则可以获得有限的编码增益,但检错能力较差。图4中检错模式的检错能力明显好于纠错模式,但检错模式没有纠错能力。

图3中,在误码字率为10-5量级时,LDPC(128,64)码较未编码系统增益为6 dB,较纠错模式BCH码增益为4 dB,LDPC(256,128)码较LDPC(128,64)码增益为1 dB,LDPC(512,256)码较LDPC(256,128)码增益为1 dB。图4中,LDPC码的漏检错误率曲线也明显低于BCH码,其中,LDPC(256,128)码只有很少的漏检错误,而LDPC(512,256)码完全没有漏检错误。

对于LDPC(128,64)码,其误码字率曲线最大约为1.5 dB,因为其性能既取决于编码器,也取决于译码器。LDPC码采用的迭代译码算法基本思想是利用校验位提供的冗余信息对有效信息进行补偿。迭代次数不断增加,校验位能提供的新的外部消息越来越少。因此,迭代次数超过一定数量后,译码性能并不会有明显的改善。在实际系统中采用LDPC码,应根据应用需求合理地选择最大迭代次数,以平衡性能和译码延时之间的矛盾。

图5为标准中推荐的LDPC(8160,7136)码的性能曲线。当误码字率为10-5量级时,LDPC(8160,7136)码所需信噪比(Eb/N0)约为3.8 dB,未编码系统所需Eb/N0约为11 dB,编码增益约为7 dB。

在未来卫星的遥控链路设计中,传输遥控指令仍然作为一个最基本功能,同时应当还包括在正常或者突发情况下向卫星传输一些大容量的数据。由于卫星本身携带的天线尺寸非常小,可用来提供数据通信的功率非常有限,因此需要尽可能地节省在遥控上消耗的功率。通过上述仿真结果分析可知,不同类型卫星的遥控业务采用LDPC编码方案设计,可以获得4~7 dB的编码增益,这样能有效降低信号解调门限,进而抵消遥控信号在长距离空间传播过程中带来的能量损失。

3 LDPC编码方案可行性分析

3.1 通信链路传输单元数据格式设计可行性分析

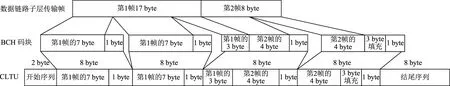

通过仿真分析可以看出,LDPC码在遥控应用中可以获得很好的性能,但是需要考虑在协议方面的实现问题。CCSDS遥控标准中,信道编码方案的可靠性和有效性尤为重要,因此需要设计良好的协议格式。CCSDS 231.0-B-2[2]中同步与信道编码子层接收数据链路协议子层的传输帧,将其组织成遥控链路传输单元(CLTU)帧格式后从物理层发送出去。BCH码块的数据格式依靠CLTU数据格式来实现。数据链路层传输帧被分割成56 bit的信息块,其中最后一段不足56 bit时填充0。之后每个56 bit信息块分别通过BCH(63,56)编码器编码,每个BCH码块后面需要补充一个0来保证整字节,生成连续的BCH码块组成CLTU帧。CLTU帧格式如图6所示。CLTU的开始序列界定了一个CLTU帧的开始,由16 bit同步字组成。CLTU的结尾序列界定了帧的结尾,接收端检测到该序列后即停止解码,结尾序列与BCH码块长度一致。

图6 BCH码CLTU组帧示意Fig.6 Components of BCH CLTU

对于本文的LDPC编码方案,可以采用与BCH编码相似的格式设计。遥控同步与信道编码子层可以组成相应长度k的码块。此外,对于结尾序列,其长度要求等于码块长度。本文以LDPC(128,64)码为例,2个数据链路子层传输帧分别为25 byte和15 byte,如图7所示。传输帧被分割成64 bit的数据块,此时不需要填充,因为40 byte正好可以分割成5个64 bit的数据块。通过LDPC编码器生成连续的128 bit的码块,并添加开始序列和结尾序列,最后完成LDPC(128,64)码的CLTU组帧。

目前,大多数低轨卫星遥控业务已采用BCH编码方案,高轨卫星(如地球同步轨道卫星)仍采用大回路比对校验方案,建议后续高低轨卫星遥控业务选择合适时机完成LDPC编码方案的转型。本文的LDPC编码方案在提高遥控可靠性的同时,其CLTU帧格式设计可以兼容现有CCSDS遥控标准中数据链路层和物理层协议,改动量较小,能够满足我国下一代卫星遥控业务的应用需求。

图7 LDPC(128,64)码CLTU组帧示意Fig.7 Components of LDPC(128,64)code CLTU

3.2 译码方案复杂度可实现性分析

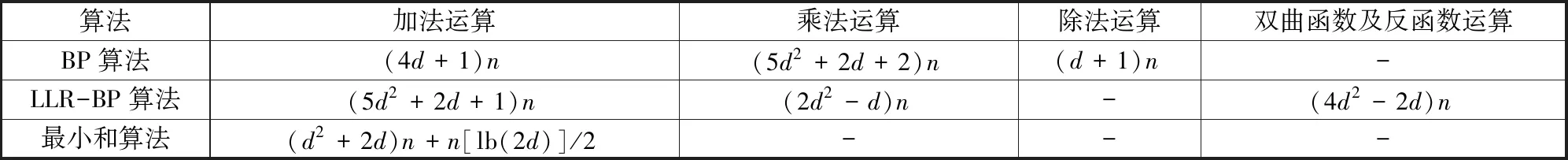

LDPC码译码算法众多,CCSDS标准中并未给出译码算法的具体规定。由于LDPC码的校验矩阵具有稀疏性,因此存在许多高效LDPC译码算法,如BP算法,其基本原理是通过贝叶斯准则获得近似最大后验概率进行译码。而后续衍生的对数域置信传播算法(LLR-BP算法)及最小和算法,也主要是对这两个过程进行优化,其大体的译码流程如下。①初始化:将接收到的码字序列分别送至各个变量节点;②迭代处理:完成校验节点和变量节点更新,直到获得合法码字或者达到最大迭代次数;③后验信息更新及判决输出:根据校验节点反馈的信息,变量节点的后验信息进行更新,并利用后验信息进行码字判决,作为译码码字输出。

表6中给出上述3种译码算法进行一次迭代译码的复杂度,其中d为列重。

表6 不同译码算法复杂度比较Table 6 Complexity of different decoding algorithms

在上述3种译码算法中,BP算法包含大量乘法运算,复杂度最高。LLR-BP算法是将基于概率的BP算法转化到对数域中,即把乘法运算转化为加法运算,从而使其复杂度大幅降低。最小和算法只采用LLR值进行校验节点更新操作,因此译码过程中只有加法运算,复杂度明显小于上述2种算法。

针对本文中2种不同指令工作模式,LDPC码方案的译码算法可以统一,但在实现上有略有区别。由于工作模式的信息长度不同,星上译码器的输入输出缓存需要根据信息长度自适当调整。由于编码方案中校验矩阵不同,星上译码器的矩阵校验节点和变量节点设计也需要满足相应的编码方案。

目前,FPGA和数字信号处理器(DSP)是卫星数字信号处理中常用的主处理芯片。DSP适合于串行运算,其主频较高功耗较大;FPGA则适合于实现高度并行的运算结构,同时具有可重复编程的特点,灵活性较高。由于LDPC码具有准循环结构,其编译码器设计适于并行实现,能够支持较高传输速率信号的处理。

通过对译码方案复杂度的分析可知,在下一代卫星遥控应用中,星上遥控译码器可以采用并行的FPGA译码器架构,译码算法可以采用最小和算法,其译码复杂度较低,硬件实现资源占用较低,能够满足卫星遥控LDPC编码方案的实施。

4 结束语

目前,卫星遥控应用中广泛采用BCH码,很难满足未来航天应用复杂多样的需求。为此,本文基于CCSDS标准,探讨在下一代卫星遥控系统设计中采用LDPC码来提高编码增益。根据下一代卫星遥控业务需要,将遥控指令分为短指令模式与内存上注指令模式,针对2种不同指令工作模式探讨不同的LDPC码应用方案。针对LDPC编码方案的可行性,本文提出采用与BCH码相似的格式设计,星上遥控译码器采用并行的FPGA译码器架构,可实现更为优异的编码增益,提高遥控数据传输速率。虽然LDPC码在工程上存在编译码复杂度较高的问题,但本文中LDPC码长均较短,编译码器电路实现只需要较少的逻辑资源,因此通过合理的编码器架构设计可以大大降低编译码复杂度,后续会针对这一问题开展进一步研究。