基于DSP和HI-6121的1553B远程终端通讯技术研究

2019-07-25

(凯迈(洛阳)测控有限公司,河南 洛阳 471009)

0 引言

随着GJB1188A-1999《飞机/悬挂物电气连接系统接口要求》在机载航空电子系统中的贯标,MIL-STD-1553B标准逐渐成为目前航空电子综合系统中信息交换的主要标准。1553B总线远程终端(Remote Terminal,RT)通讯技术也成为航空电子子系统的关键接口技术之一,其作用是在航空电子子系统和作为1553B总线控制器(Bus Controller,BC)的航空电子管理系统之间搭建一座桥梁,使得二者的信息流能够实时、准确和可靠地进行交互。

1553B总线协议的实现主要有两种方式,一种是基于单功能或多功能的1553B协议芯片实现,另一种是基于IP的FPGA实现。地面测控仿真模块从设计的灵活性考虑,多使用FPGA来实现1553B协议;机载航电设备从可靠性角度考虑,一般使用协议芯片连接到控制器来完成1553B总线协议。国内外多家公司推出了各种不同功能、封装的协议芯片,能与DSP、FPGA、ARM等各种嵌入式器件相连接,实现1553B总线RT、BC和BM功能。DDC公司的BU-61580是使用最广泛的协议芯片之一,它功能强大,但应用复杂,价格昂贵,封装也较大,并不适用于某些对成本和封装体积有较高要求的航空电子设备。而HOLT公司单一RT功能协议芯片HI-6121具有封装小,价格低,功能丰富,接口简单,使用简便等优点,能够满足多数航空电子设备的要求,特别是那些小型化低成本无人机航空电子设备。本文给出了一种基于DSP和HI-6121的1553B远程终端通讯技术方案,探讨了软硬件设计要点。目前,该方案已在某型挂飞训练弹与导弹模拟器中应用,具备一定的应用推广价值。

1 1553总线结构及原理

MIL-STD-1553B总线(简称1553B总线)是美国国防部定义的一种军用数据总线标准,全称为飞机内部时分制命令/响应型多路传输数据总线,对应我国军标为GJB289A-1997。它规定了数据总线及其接口电子设备的技术要求[1]。

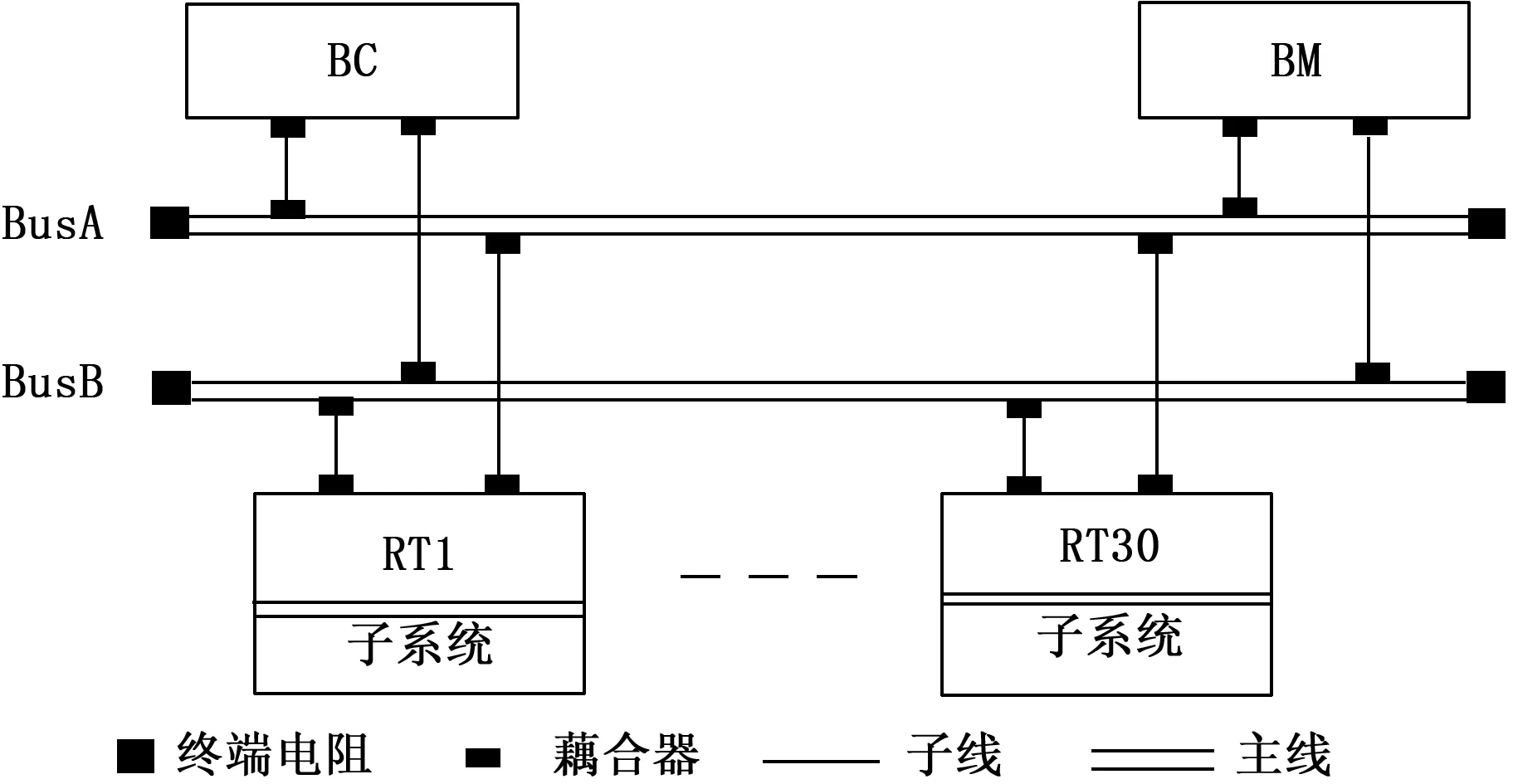

1553B总线为多冗余度总线型拓扑结构,具备两个互为冗余的数据通道,保障了良好的故障隔离和容错性,具有双向传输特性,半双工工作方式,主要由四部分组成:屏蔽双绞线的传输介质;1个控制和管理总线消息传输的BC;1个接收总线消息用于监测和记录的总线监控器(Bus Monitor,BM);1~30个作为用户子系统接口的RT,结构如图1所示[1-2]。该总线有10种消息格式,实现了BC→RT、RT→BC、RT→RT和各种广播与控制方式指令。每个消息最少有两个消息字,每个消息字包括3个bit的同步头、16个消息bit和1个奇偶校验bit,所有的消息字都采用曼彻斯特II码构成[2-3]。

图1 1553B多冗余度总线型拓扑结构

2 系统硬件设计

2.1 HI-6121的功能与特点

HI-6121是符合1553B协议所有要求的全集成3.3 V远程终端器件;采用SPI总线作为主机接口,方便MCU、DSP和FPGA等多种处理器连接,简化了接口电路与时序匹配;片内32K×16bit RAM,可配置为四种数据缓存模式,每个子地址收发命令的数据缓存模式都可以独立设置;内置可编程设置时间精度的16位时标计数器,为1553B消息提供实时时标;优化中断缓存和管理,最高可缓存16个中断申请,减轻了主机的中断资源开销;可选上电自EEPROM自动初始化配置,缩小系统软件代码尺寸;PQFP-52的小型封装,便于在嵌入式系统中使用[4]。

2.2 硬件系统实现

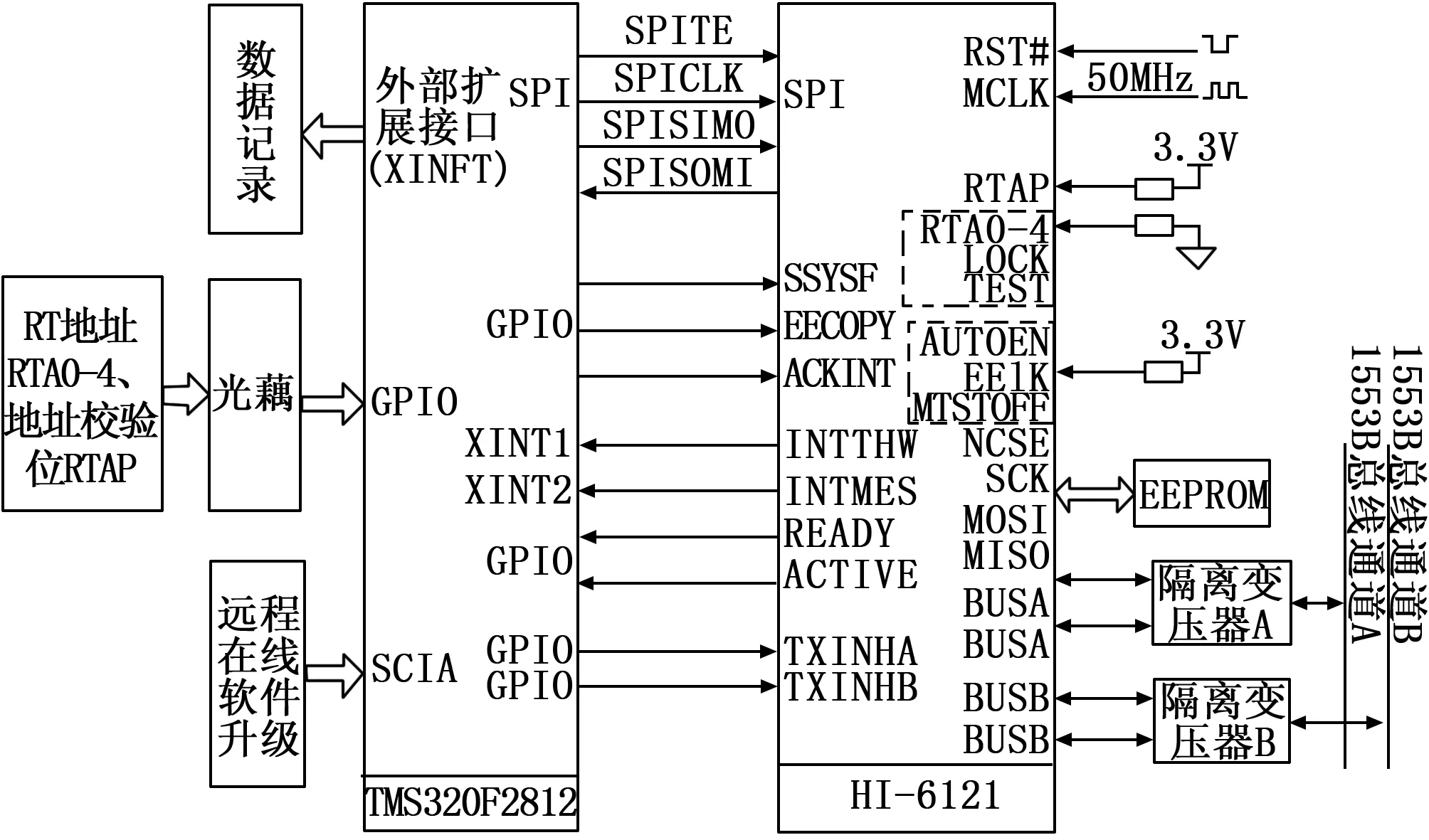

硬件电路主要包含控制器与HI-6121之间接口电路,总线耦合电路,时钟、复位与电源电路和功能扩展电路等4个部分,硬件系统原理如图2所示。

图2 硬件系统原理图

2.2.1 控制器接口电路设计

选用TI公司基于增强型哈佛结构的32位DSP器件TMS320F2812作为核心控制器,其主频最高可以达到150 MHz,具有片内128K字FLASH,2个CPU定时器,SPI、外部总线接口、UART、ADC和外部事件管理器等多种外设资源[5]。如图2所示,控制器与HI-6121之间接口电路原理主要如下:

1)HI-6121作为SPI从机,具备两种SPI时序模式:Mode0(CPHA = 0, CPOL = 0)和Mode 3 (CPHA = 1, CPOL = 1), SPI同步时钟SCK最高速率可以达到40 MHz。本文中TMS320F2812作为SPI主机采用SPI模式Mode0与HI-6121连接,从数据传输可靠性角度考虑选择4 MHz作为SCK频率;

2)HI-6121的READY管脚用于指示内部自检完成或是自初始化完成,DSP通过GPIO检测到READY管脚电平变高后,才能对HI-6121进行操作;

3)HI-6121的AUTOIEN和EE1K上拉接高电平,使用芯片的EEPROM自初始化配置模式,上电时芯片自动搬移EEPROM地址0x0~0x3FF中的数据到芯片内部对应地址中,主要包括寄存器、非法命令表和描述数据,可以节约DSP的内部RAM资源开销;DSP通过GPIO输出宽度不小于1 ms的高电平脉冲给EECOPY管脚,使HI-6121自动搬移芯片内部0x0~0x3FF中的数据到EEPROM地址对应地址中;

4)HI-6121有两个中断输出管脚INTHW和INTMES,分别连接到DSP的两个外部中断,INTHW用于指示芯片内部SPI通讯、时标计数器溢出、RT地址校验错误、EEPROM校验错误和RAM初始化错误等硬件自身事件,INTMES用于指示1553B消息收发事件,二者的输出电平状态均可设置。DSP的GPIO连接HI-6121管脚ACKINT,对接收到的中断作出确认,以便HI-6121释放中断;

5)HI-6121的RT地址既可以由外部信号注入,也可通过软件配置RT地址寄存器来完成。在RST#的上升沿将外部RT地址信号、RT地址校验信号和LOCK信号锁存,当LOCK信号为高电平时,DSP就不能再通过软件重新配置RT地址。考虑到测试和排故等原因,更宜采用灵活的软件配置RT地址模式。因此,下拉LOCK信号为低电平,使能RT地址寄存器可重配置。RT地址信号RTA0-4和RT地址校验信号RTAP先通过光耦隔离进入DSP进行校验,作为系统自检工作之一,再由DSP写入HI-6121的RT地址寄存器,完成RT地址配置;

6)DSP通过复用SPI总线操作板载实时时钟芯片DS3234,获得实时时间信息作为接收和发送的1553B数据包的的绝对时标,相对时标通过HI-6121的时标计数器获得,精度有2 μs、4 μs、8 μs、16 μs、32 μs和64 μs等六种,通过软件配置,可任选其一;

7)通过控制TXINHA和TXINHB管脚,可以禁止芯片的BusA和BusB总线传输。通过控制SSYSF管脚,可以置1553B状态字中的“SUBSYS”标志位,向BC表明子系统出现了故障。

2.2.2 总线耦合电路

1553B总线的连接方式有两种:变压器耦合与直接耦合。直接耦合方式适用于不超过0.3 m的短距连接。变压器耦合方式适用于不超过6 m的长距离[6]。无论哪一种,子系统都需要通过一级隔离变压器进行故障隔离。根据应用要求,HI-6121与1553B总线的连接方式采用变压器耦合方式,隔离变压器选用HOLT公司的PM-DB2791S,变压比值为1:2.5[7]。

2.2.3 时钟、复位与电源电路

选用TI公司的电源芯片TPS767D318PWP,输出3.3 V和1.8 V两路电源,其中3.3 V作为DSP的IO供电与其它电路供电,1.8 V作为DSP的核心供电。TPS767D318PWP能够在上电时输出延迟时间为200 ms的低电平复位信号,使DSP和HI-6121能够可靠地上电复位。DSP时钟选用30 MHz的晶体谐振器,内部倍频为150 MHz作为系统时钟;HI-6121时钟内部无倍频电路,直接选用50 MHz有源晶体振荡器输出的时钟作为系统时钟。

2.2.4 功能扩展电路

TMS320F2812有两个UART,其中一个用于远程在线软件升级和实时时钟芯片的校时,另一个用于与其它功能系统进行数据交互。通过XINTF接口,DSP将收发到的1553B消息字写入数据记录模块的RAM缓存区,扩展1553B数据记录功能。

3 系统软件设计

3.1 软件组成

软件系统完成协议芯片及其它功能电路的控制和1553B数据的接收、发送和校验处理,主要包括: HI-6121底层驱动和初始化,中断处理与系统工作流程等三个部分。

3.2 HI-6121底层驱动和初始化

3.2.1 地址映射

HI-6121的功能与状态寄存器和共享RAM统一以字为单位映射在32 K地址空间,0x0000-0x001F为功能与状态寄存器映射地址;其余为共享RAM映射地址。包括了数据接收暂存、中断日志、非法命令表、描述表和子地址数据收发缓存。寄存器读写模式为直接地址映射,共享RAM读写模式为指针地址映射。DSP通过对HI-6121的各种寄存器及共享RAM进行数据读写操作来完成1553B消息字的接收与发送。

3.2.2 主要功能寄存器说明

1)配置寄存器1#和2#:用来设置HI-6121的总线收发器的开/关,中断输出模式,时标精度、复位和重载,软复位,芯片工作开始/停止,广播消息有效性,未定义方式字有效性,RT→RT超时等;

2)操作状态寄存器:主要用于RT地址和校验位读写及锁定;

3)最新命令字寄存器:存放消息中断的最新消息命令字;

4)最新控制字地址寄存器:存放消息中断的消息控制字在内存中所在地址,使主机可以通过该地址读取芯片缓存中1553B消息数据字和状态字;

5)内存地址指针寄存器:HI-6121的内存0x0-0xF地址可以直接访问,其余地址通过内存地址指针间接访问;

6)描述表基地址寄存器:设置描述表的起始地址;

7)1553状态字位设置寄存器:设置/读取RT状态;

8)中断使能寄存器:对各种中断源进行使能或是禁止;

9)时标寄存器:读取该时刻的绝对时标值。

3.2.3 HI-6121初始化步骤[8]

系统上电复位后,通过设置相应的功能寄存器来初始化HI-6121的基本工作模式,配置子地址描述表来设置合法消息处理机制,配置非法命令描述表来设置非法消息处理机制。初始化步骤如下,在实际应用中可根据具体情况删减和更改。

1)读取READY信号,到READY变高后,DSP才能对HI-6121进行读写操作。

2)建立描述表:描述表定义了RT终端对有效命令的响应,由4部分组成,分别是子地址接收消息描述块、子地址发送消息描述块、接收方式命令消息描述块、发送方式代码消息描述块。每个消息描述块都有128字,分为32个4字组(1个控制字和3个描述字)。子地址接收消息描述块的控制字设置该子地址接收消息数据的缓冲模式、是否产生中断、是否为合法命令等。芯片共有4种数据缓存模式:单消息模式、乒乓模式、循环1模式、循环2模式。3个描述字根据缓存模式不同而放置相应的地址指针,本文选择发送数据缓存模式为单消息模式,描述字2为消息指针,描述字3为0,,描述字4为广播消息指针。接收数据缓存模式为乒乓模式,描述字2为数据区A指针,描述字3为数据区B指针,描述字4为广播消息指针。中断模式设置为消息中断。未用子地址的控制字和3个描述字都置0,设置为非法命令。

3)建立非法命令表:HI-6121通过256个字的非法命令表来实现非法消息命令的设置和检查,分为广播接收命令设置块、广播发送命令设置块、子地址接收命令设置块、子地址发送命令设置块。每条收发命令和方式命令都有两个控制字,共32bit,代表了32个数据字的合法性,‘0’为合法,‘1’为非法。非法命令检测是一个可选过程。当不使用非法的命令检测时,终端对所有有效的命令字都进行响应,回复传输状态字并处理命令字中定义的数据字数。当不使用非法命令检测时,BC无法根据RT终端的传输响应判断命令是合法的还是非法的。

4)DSP通过GPIO读取RT地址和RT地址校验位,校验后写入操作状态寄存器并锁定。

5)设置配置寄存器1#,禁止芯片工作,设置时标计数器精度,选择兼容1553B NOTICE2协议,选择方式命令处理流程简化模式。

6)设置配置寄存器2#,选择RT-RT超时时间,装载时标计数器,选择方式命令消息处理模式;

7)根据实际需要设置中断使能寄存器;

8)根据配置寄存器2#中的“MCOPT4”位逻辑值来配置BusA/B选择寄存器,用于执行方式命令中的“selected transmitter”shutdown和override两项命令;

9)设置自检模式和测试控制模式;

10)将描述表和非法表写入HI-6121的共享内存;

11)配置寄存器1#的“STEX”置位,芯片开始工作。

如前文所述,HI-6121初始化模式有主机配置和EEPROM配置两种模式,初始化步骤基本一致。不同在于,主机配置时初始化步骤放在系统软件中,由DSP完成功能寄存器和共享RAM的数据写入;而本文选择的EEPROM配置,初始化步骤是独立的软件,步骤11)改为给EECOPY管脚一个大于1 ms的脉冲信号,触发HI-6121将数据写入EEPROM。在系统软件中完成RT地址重新配置,并使能芯片开始工作。

3.2.4 SPI总线传输过程中的中断处理

HI-6121采取指针方式对0xF以上的地址进行寻址。如果在SPI数据传输过程中,有事件触发DSP中断,系统软件转入中断服务子程序对HI-6121进行读写操作,将更改指针数据,从而影响了中断前正在进行的SPI数据传输。因此,进入中断服务子程序后必须先将HI-6121指针寄存器的数值暂存,中断服务子程序结束前将指针寄存器的数值还原,避免指针跑飞造成器件功能异常。

3.3 系统工作流程

系统工作流程采用模块化设计,如图3所示,主要包括初始化模块、中断处理模块、数据接收模块和数据发送模块。

图3 系统软件设计流程

初始化模块:DSP自身初始化,然后等待HI-6121自初始化完成后,完成RT地址重新配置,并使能芯片开始工作。开启外部中断等待1553B消息中断;

中断处理模块:读取当前中断消息的命令字(地址0x03)和信息字映射地址(地址0x0A)放入1553B消息命令堆栈,并使堆栈指针递增,堆栈深度可根据具体情况设置。

数据接收模块:主程序根据堆栈指针判断堆栈中是否有未处理的1553B消息,根据1553B消息命令字解析子地址、T/R、数据个数。如果是“接收”命令字则根据信息字映射地址和数据个数来读取HI-6121共享内存中缓存的数据;如果是“发送”命令字,则表明BC取走的HI-6121共享内存中该子地址的数据。

数据发送模块:将准备好的数据写入子地址对应的HI-6121共享内存区间,根据GJB1188A的规定,置位子地址对应的矢量字位,并将矢量字写入对应的HI-6121共享RAM相应地址。BC收到矢量字后,按照矢量字位下发RT发送命令,HI-6121接收到命令后自动将数据上传给BC[9]。

4 测试与验证

4.1 测试环境

根据上文所述的技术方案设计了1553B总线远程终端通讯板卡。根据图1的总线架构,选用GE公司CPCI总线1553B板卡作为1553B总线 BC,本文设计的通讯板卡作为1553B总线RT,使用1553专用线、2个盒式耦合器和78欧姆终端匹配电阻构建双通道测试环境,进行消息收发测试。主要包括BC与RT之间的消息收发测试、方式代码测试和双冗余通道测试三种[10]。

4.2 BC与RT之间的消息收发测试

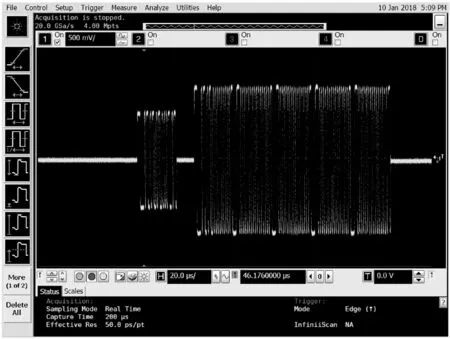

1)BC向RT发出命令字(接收)+4个数据字,RT回复1个状态字,DSP得到的数据与GE板卡发出的数据一致, RT端波形如图4所示。

图4 RT接收消息波形

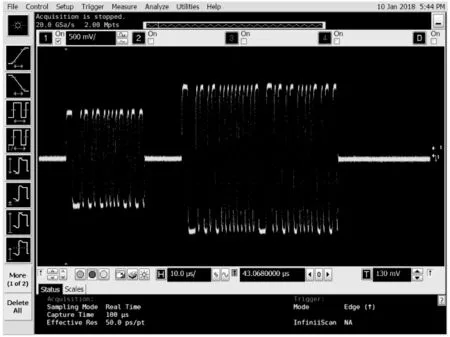

2)BC向RT发出命令字(发送),RT回复4个数据字+1个状态字,GE板卡得到的数据与DSP设置的数据一致,RT端波形如图5所示。

图5 RT发送消息波形

4.3 方式代码测试

BC向RT发出方式代码(查询矢量字),RT回复1个矢量字+1个状态字,GE板卡得到的数据与DSP设置的数据一致,RT端波形如图6所示。

图6 查询矢量字波形

4.4 双冗余通道测试

双冗余通道是1553B总线可靠性保障之一,BusA作为主通道,BusB为冗余备份通道。测试时,从盒式耦合器端将BusA通道断开或将BusB通道断开,重复进行上述的BC与RT之间的消息收发测试、方式指令测试,通讯板均能正常工作,数据收发正确。

5 结束语

本文主要介绍了一种小型化、低成本的1553B总线远程终端设计、实现、测试与验证,以TMS320F2812为控制器,以HI-6121为1553B协议芯片,简化了硬件与软件的设计,可以使电子设备快速接入1553B总线。该通讯板已批量应用在某小型航空制导炸弹挂飞训练弹及导弹模拟器项目中,通过试验室试验、环境适应性试验和外场挂飞试验,系统工作正常,具备良好的可靠性,在1553总线设备的小型化,低成本等方面具有一定的参考价值。