多级中断屏蔽技术分析

2020-12-08赵琳娜

赵琳娜

(内蒙古民族大学 计算机科学与技术学院,内蒙古 通辽 028000)

0 引言

在现代的计算机系统中,为了提高整个系统的资源利用率及吞吐量,均引入了中断机制,采用中断技术对计算机内部、外部的随机或突发事件要求进行实时及时的处理。在引入中断机制的计算机系统中,一旦I/O设备完成传输数据的准备工作(输入设备完成新数据的输入/输出设备完成旧数据的输出),设备控制器便通过控制线向CPU发送中断信号,CPU在条件允许的情况下,暂停当前程序的运行,为外设进行输入输出。一方面,由于在CPU工作时,允许多进程模式,通过不同进程启动不同I/O设备,从而达到CPU和多个外设同时并行工作的要求,大大提高CPU的利用率及数据输入、输出的速度。另一方面,中断技术以I/O设备的控制器向CPU发出请求作为启动中断服务的前提,因此计算机在运行过程中,出现的各种软硬件故障,计算机可以利用中断系统自行处理,而不必停机或报告工作人员。

1 中断屏蔽作用

一方面,由于中断技术在计算机系统中涉及的软硬件中断事件很多,在中断处理的过程中为了增加处理的灵活性及与不同事件处理需求的适应性,需要在中断过程中采用中断屏蔽技术。另一方面,在中断过程中,紧急事件对非紧急事件的嵌套执行的实现也需要采用中断屏蔽技术做技术支撑。中断系统实现中断嵌套的功能,应具备以下条件。

(1)CPU内部中断允许标志位设置为允许,即为开中断,反之为关中断,关中断相当于将I/O设备的控制器向CPU发出请求的中断请求全部屏蔽,即屏蔽了比CPU主程序优先级别低的I/O设备程序。

(2)优先级别高的中断源有权中断优先级别低的中断源。在满足(1)的前提下,只有优先级别更高的中断源请求才可以中断比其级别低的中断服务程序,反之则不然。

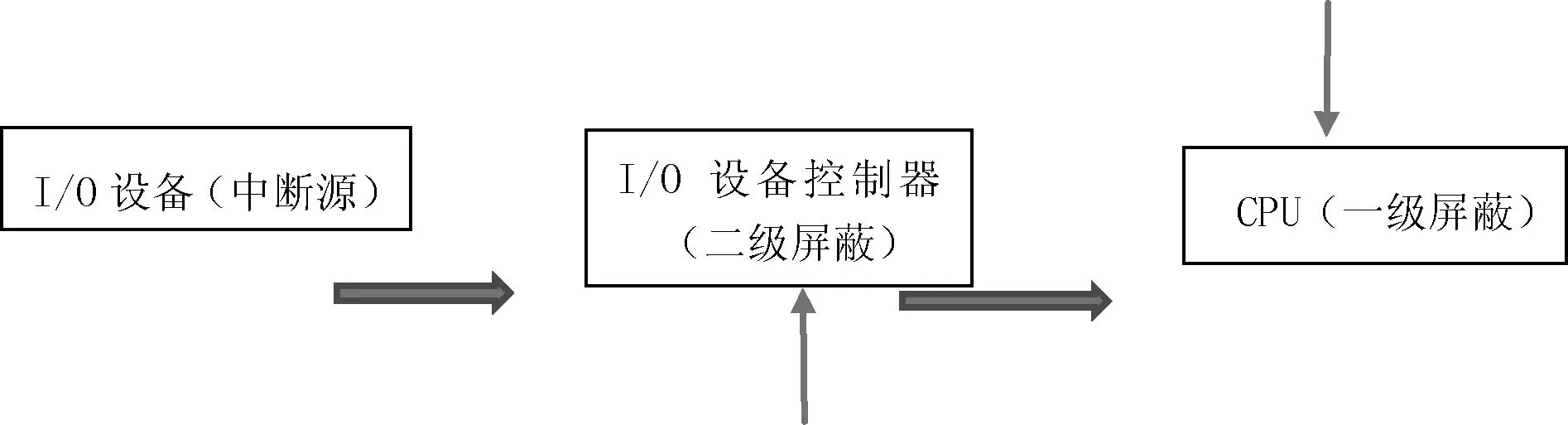

上述两个条件都具备关闭一些程序或事件执行而开放另一些程序/事件执行的作用,这一作用被称为屏蔽。同时由上述条件可知,屏蔽作用具有两个层次,一个层次直接在CPU内部进行描述,另一层次在中断源侧描述,在此将前一层次称为一级中断屏蔽,后一层次称为二级中断屏蔽,两个级别的中断屏蔽层次关系如图1所示。

图1 两级中断屏蔽层次示意

用于进行CPU当前主程序与I/O控制器请求执行的中断程序的嵌套关系设置,用于进行不同优先级别中断源的嵌套关系设置。

由图可知,二级屏蔽的主要作用在于灵活处理多个中断源的服务竞争问题,这级屏蔽主要通过在中断管理接口部件中设置完成,在微机系统中二级中断屏蔽设置由中断控制器实现,例X86系统的intel8259A芯片。一级屏蔽的作用在于灵活处理CPU当前执行的程序与新提出服务请求外设程序的竞争问题,因涉及对程序进行转移切换,所以这级屏蔽要通过在CPU内部的设置实现[1]。

2 二级屏蔽技术

二级屏蔽技术实现的硬件支撑主要是中断屏蔽触发器。在近中断源的中断控制接口电路中为了实现二级中断技术需要设置中断屏蔽触发器,每个中断源对应设置一个中断屏蔽触发器,当该触发器的值设置为1时,对该中断源起屏蔽作用,反之允许该中断源的中断请求向CPU端传递。显然在此处设置的中断屏蔽触发器对各中断源向CPU提出中断服务的请求起到了一个根据各中断源的实际情况灵活允许和禁止的控制技术。

将各中断源对应的中断屏蔽触发器8个一组连合在一起便构成了一个中断屏蔽寄存器。屏蔽寄存器的内容称为屏蔽字。屏蔽字与中断源的优先级有对应关系,可以从另一个层面对中断源的中断服务请求进行竞争管理[2]。

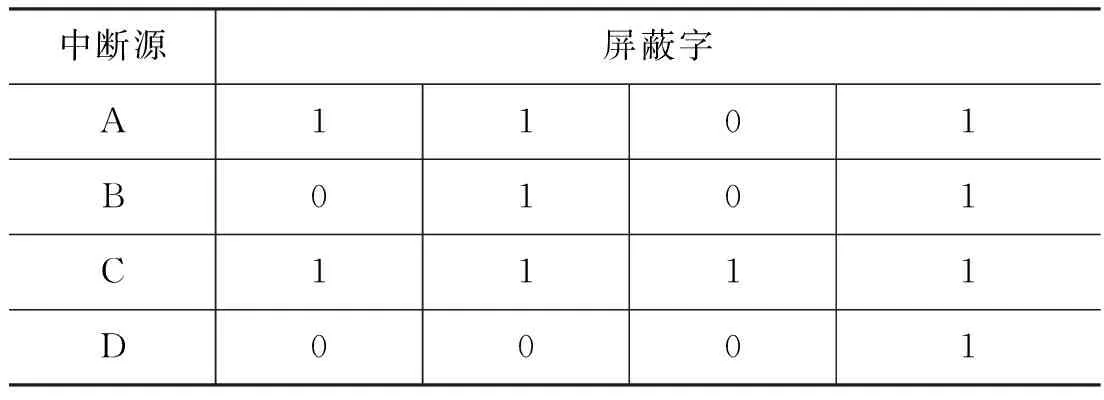

一般中断源的优先级包含响应优先级和处理优先级。响应优先级是指CPU响应各中断源请求的优先次序,这种次序一般通过链式硬件线路设置,不便于改动。处理优先级是指CPU实际处理各中断源服务的优先次序。不采用屏蔽技术时,各中断源的响应优先级次序和处理优先级次序一致。当设置屏蔽字即采用了屏蔽技术后,CPU对各中断源的处理优先级别随之改变,例如,在系统中有A,B,C,D 4个中断源,响应优先级别按A->B->C->D降序排列,在不采用屏蔽技术的情况下,处理优先级与响应优先级一致,按A->B->C->D降序排列。当设置屏蔽字如表1所示,响应优先级次序不变,处理优先级次序改变为C->A->B->D。

表1 中断源的屏蔽字设置

C中断源屏蔽字各位全为1,优先级最高,在该中断源服务时,屏蔽了包括本中断源在内的所有中断源的服务请求。A优先级次高,屏蔽字第2位为0(对应C中断源),说明A中断源在中断服务程序执行期间不能屏蔽C中断源的服务请求,其余位为1,说明在A中断源服务时,能够屏蔽包括本中断源在内的A、B、D中断源的服务请求,其他同理,不再论述。由此可见当需要根据实际应用需求灵活改变中断源的处理优先级别时,可以通过设置不同的屏蔽字实现[3]。

3 一级屏蔽技术

在通过上述中断接口电路的控制后,竞争获胜的中断源的中断请求送达了CPU,在微机系统中送达CPU的中断请求传送到INTR引脚,称为可屏蔽的中断请求。如上文中所述,该引脚输入的请求将受CPU内部中断允许标志位的控制。当CPU当前执行的程序重要程度高于获胜中断源要求执行的程序时,CPU令中断允许标志位为0,相当于CPU关闭对外部中断源响应的总开关,将外部中断源全部屏蔽,实现了CPU执行程序的实际灵活控制;若CPU当前执行的程序是某中断源的服务程序(假设该中断源的处理级别低于通过INTR引脚新输入来的中断源的级别),上述操作的结果也将导致中断嵌套被禁止,从而体现了CPU内部的中断允许标志位对中断屏蔽技术的作用[4]。

4 结语

中断屏蔽技术对中断过程的影响非常关键,在中断源的中断请求、中断响应、中断服务及中断返回4个阶段,一级、二级及三级中断屏蔽设置发挥着灵活改变优先级、适应实际应用要求、选择不同传输模式等作用,理解中断屏蔽技术,在程序设计中灵活运用该技术,对编写高质量的程序非常必要。