基于宽带DAC的雷达信号模拟器信号产生设计

2019-07-22王思远江友平

王思远,江友平

(中国船舶重工集团公司第七二三研究所, 江苏 扬州 225101)

0 引 言

随着电子技术的发展,现代战争对雷达系统提出了越来越高的性能要求。在雷达的研制过程中,如何去检验和测试雷达的性能是一个关键问题。越来越多的雷达系统采用雷达信号模拟器去测试雷达性能。相比于外场实测来说,雷达信号模拟器检测具有经济、便捷等优势,从而成为了雷达性能测试的主要选择。

现代雷达系统要求雷达信号模拟器不仅能做到频带更宽、稳定性更好、波形及频率跳变速度更快,并且能根据数学模型产生各种雷达波形信号、干扰信号以及通信信号。传统的雷达信号模拟器一般采用专用DDS集成芯片来产生信号已不能满足现代雷达系统的需求。近年来,集成电子技术的发展使得现场可编程门阵列(FPGA)的性能得到了极大的提高,可以利用FPGA 实现直接数字频率合成(DDS)系统的数字部分。这使得采用FPGA内嵌DDS核加宽带DAC成为可能[1]。FPGA的强大运算能力可以提高跳变速度,并能产生各种波形。本文基于FPGA加宽带DAC来进行软硬件的设计,产生各种雷达波形调制信号,可以广泛应用于雷达信号模拟器的信号产生。

1 DDS的原理

DDS是通过奈奎斯特采样定理实现频率合成的技术。假设一个理想的正弦波为

S(t)=Acos(2πft+φ)

(1)

其中,A为振幅,f为频率,φ为初始相位。在实际应用中,一般只考虑相位变量Δφ,可表示为

Δφ(t)=2πft

(2)

对两边微分可以推出

dΔφ(t)/dt=2πf

(3)

所以

f=Δθ/2πΔt=ΔθFclk/2π

(4)

通过上式可以看出,在系统时钟确定的情况下,输出频率f和相位增量Δθ为一一对应关系,所以可以通过控制相位增量Δθ来控制频率输出。具体方式是通过改变频率控制字 FTW(Frequency Control Words)来控制相位累加器的输出相位增量。相位累加器位数越多,控制精度就越精确[2]。

本文采用32位的相位累加器进行设计。相位累加器输出的相位码进入正弦波形查找表。通过寻址得到的量化幅度字经过DAC变为相应的阶梯波,最后通过低通滤波器平滑后得到信号波形。基本原理如图1所示。

2 信号产生模块

2.1 宽带DDS核

FPGA中的DDS核主要是实现相位累加器与幅度码查找表的功能。单个DDS核的工作频率理论最高值为550 MHz[3],所产生的信号带宽较窄,不能满足现代雷达带宽的需求。因此,本文采用多个DDS核合成的方法来解决这个问题。

假设有n个低速DDS核,它们的工作频率同为xMHz,且每个DDS核之间的相位相差2πfΔT/n(f为所需频率,ΔT为所需采样间隔)。将他们按相位从小到大的顺序进行排列(见图2),就可以构成采样频率为nxMHz的宽带DDS核[4]。

本文采用16个DDS核并行构建一个2 GHz采样率的宽带DDS核模块。该宽带DDS核模块由16个DDS核组成,工作频率同为125 MHz,依次排序为1、2、3…16。每个核的相位增量控制字(PINC)和相位初始控制字(POFF)可以通过公式(5)和(6)算出。

(5)

其中,fout为需要输出的频率,精度为1 Hz;pout为需要输出的相位,精度为1°;fclk为DDS核的工作频率125 MHz;n为DDS 核在DDS核序列中的排序。

计算完成后,将PINC和POFF输入相应的DDS核。每个DDS核会输出一组14位的正弦波数字序列。将16组数列按相应的方式经过宽带DAC,经平滑后得到相应的输出信号。

2.2 调频信号的实现

任意波形的产生在FPGA内实现。以线性调频为例,线性调频信号可以表示为

(7)

其中,f0为信号的起始频率,T为扫频周期,B为信号带宽。

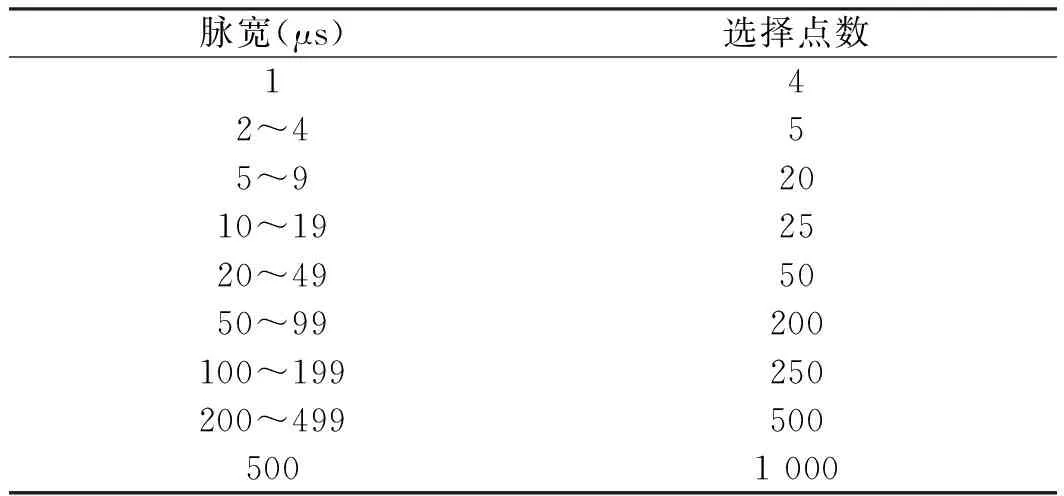

本文在FPGA内部构建一个ROM。ROM中存储一个表长度为1 000个点、带宽为1 M的线性调频信号查找表。当需要产生线性调频信号时,上位机将信号的中心频率fm、带宽B、脉宽pw、扫频周期T等参数发送给FPGA。FPGA通过fm-B/2计算出线性调频的初始频率f0。根据脉宽与子码宽度选择表(见表1),确定从1 000个点中选择的点数,并将选出第1个点的频率控制字送给宽带DDS核,持续1个子码宽度的时间。再将第2个点的频率转化为频率控制字送给宽带DDS核,同样持续1个子码宽度的时间(见图3)。

表1 子码宽度选择表

这样逐渐累加,直到完成这个扫频周期。这样就完成了1个周期的线性调频信号,线性调频流程(见图4)。

非线性调频的产生与线性调频信号类似,不同之处在于ROM里存储的是一个1 M的非线性调频信号(如正弦波、三角波)。

2.3 相位编码信号的实现

相位编码信号是通过对载波的相位进行离散编码得到的,一般分为只有0°、180°两种相位的二相编码和多种相位的多相编码。

相位编码信号实现方式与线性调频类似,还是利用FPGA的ROM存储1个相位查找表。以7位L码举例,存储地址依次存放0°、180°、180°、0°、180°、0°、0°。上位机将中心频率、子码宽度、相位编码类型以及调制周期发送给FPGA,FPGA通过选取存储7位L码的ROM,取出第1个地址存放的0°作为初相发送给宽带DDS核,经过1个子码宽度的时间,取出第2个地址存储的数据180°发送给宽带DDS核,如此循环直至完成1个周期。

3 硬件实现

本文使用Xilinx公司Virtex6系列中的XC6VLX240T型号FPGA来实现控制部分以及DDS的数字部分,DAC则使用AD公司一款14位的高速高性能射频DAC芯片AD9739。

由于AD9739通过LVDS双通道输入,而FPGA则具有多达数百个LVDS接口,所以二者可以实现直连。FPGA通过连接AD9739的SPI接口控制AD9739。2 GHz差分时钟输入AD9739的DACCLK接口作为工作时钟。AD9739将2 GHz时钟4分频通过DCO输出500 MHz的差分时钟给FPGA。FPGA将500 MHz作为数据传送模块的串行时钟,同时再将之4分频作为DDS核的工作时钟和输出并串转换器(Oserdes)模块的并行时钟。

数据传输时,FPGA将宽带DDS核排序为奇数的8路输出连接到数据传送模块1,排序为偶数的8路输出连接到数据传送模块2。数据传送模块由Oserdes模块组成。由于Oserdes只有6路输入,所以构建1个数据传送模块需1片主Oserdes和1片从Oserdes组成。数据传送模块将16路并行数据转换成两路奇偶的数据,分别发送到AD9739的DB0与DB1接口。

在产生数据的同时,按照同样的逻辑产生1路随路时钟DCI。DCI的产生方式与数据产生方式一样,以保证到达AD9739的传输延时相同。

AD9739接收数据后,通过数模转换并经低通滤波器平滑后得到所需要的信号波形。

图5为硬件连接框图。

4 测试与结果分析

利用信号源产生2 GHz的工作时钟给AD9739测试所设计的方案。分别发送500 MHz的连续波信号、中心频率为500 MHz的线性调频信号、正弦波调频信号、调相信号。用频谱仪测试连续波信号,用信号分析仪测试各种调频调相信号。测试结果如图6~9所示。因本文主要完成的是调频信号的产生,单点信号的质量不作为重点,杂散≤-50 dB,谐波≤-60 dB。

5 结束语

本文设计了一种雷达模拟器波形信号产生方案。该方案是以FPGA为控制核心,同时与宽带DAC相结合,实现了雷达信号模拟器中各种波形信号的产生。结果显示,该方案能灵活地实现各种信号的产生。