2~18 GHz超宽带低噪声放大器芯片研制*

2019-07-16文晓敏

文晓敏,李 斌

(1. 中国科学院上海天文台,上海 200030;2. 中国科学院大学,北京 100049)

作为射电天文望远镜接收机前端的核心器件,低噪声放大器(Low Noise Amplifier, LNA)不仅要将天线接收到的来自外太空的微弱信号进行低噪声放大,还要求具有较高的增益抑制后级链路的噪声,保持接收系统的灵敏度。单片微波集成电路(Monolithic Microwave Integrated Circuits, MMIC)形式的低噪声放大器芯片是实现超宽带、低噪声、高增益器件的重要途径。变组分高电子迁移率晶体管(Metamorphic High-eletron-mobility Transistor, mHEMT) 具有高频、高功率及噪声性能好的优点,广泛应用于雷达、遥感、辐射测量等领域[1]。本文设计单片微波集成电路低噪声放大器芯片所用的OMMIC D007IH mHEMT工艺,拥有70 nm栅长和高掺铟沟道,在组分缓变的缓冲层上生长高铟浓度的外延活跃层,从而实现与砷化镓(GaAs)衬底的平稳过渡,因而使其具有极低的噪声和超高频特性[2]。本文设计的2~18 GHz低噪声放大器芯片频率覆盖达到9倍频程,结合超宽带馈源和极化网络,可以构建超宽带射电天文接收系统,实现S, C, X, Ku 4个传统射电频段的同时观测,极大地提高连续谱观测灵敏度和多谱线观测效率,是国际上射电天文技术发展的重要方向。

1 电路设计

1.1 噪声特性及器件选择

低噪声放大器级联噪声系数公式为

(1)

其中,NFn,Gn分别为第n级的噪声系数和增益。由(1)式可知,低噪声放大器的整体噪声性能主要取决于第1级的噪声系数,后级的噪声可通过前级的高增益加以抑制。在对噪声性能要求比较高的射电天文接收系统中,通常用噪声温度Te表征其噪声性能。噪声温度与噪声系数的转换关系为

(2)

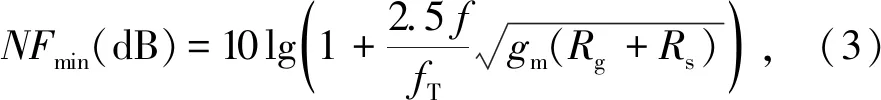

晶体管的选择要兼顾噪声、增益以及驻波比的特性。图1为砷化镓金属-半导体场效应晶体管的噪声等效电路图,根据FUKUI建立的金属-半导体场效应晶体管最小噪声模型[3]:

同时,对于单指晶体管:

Rg=Rg0×W,

(4)

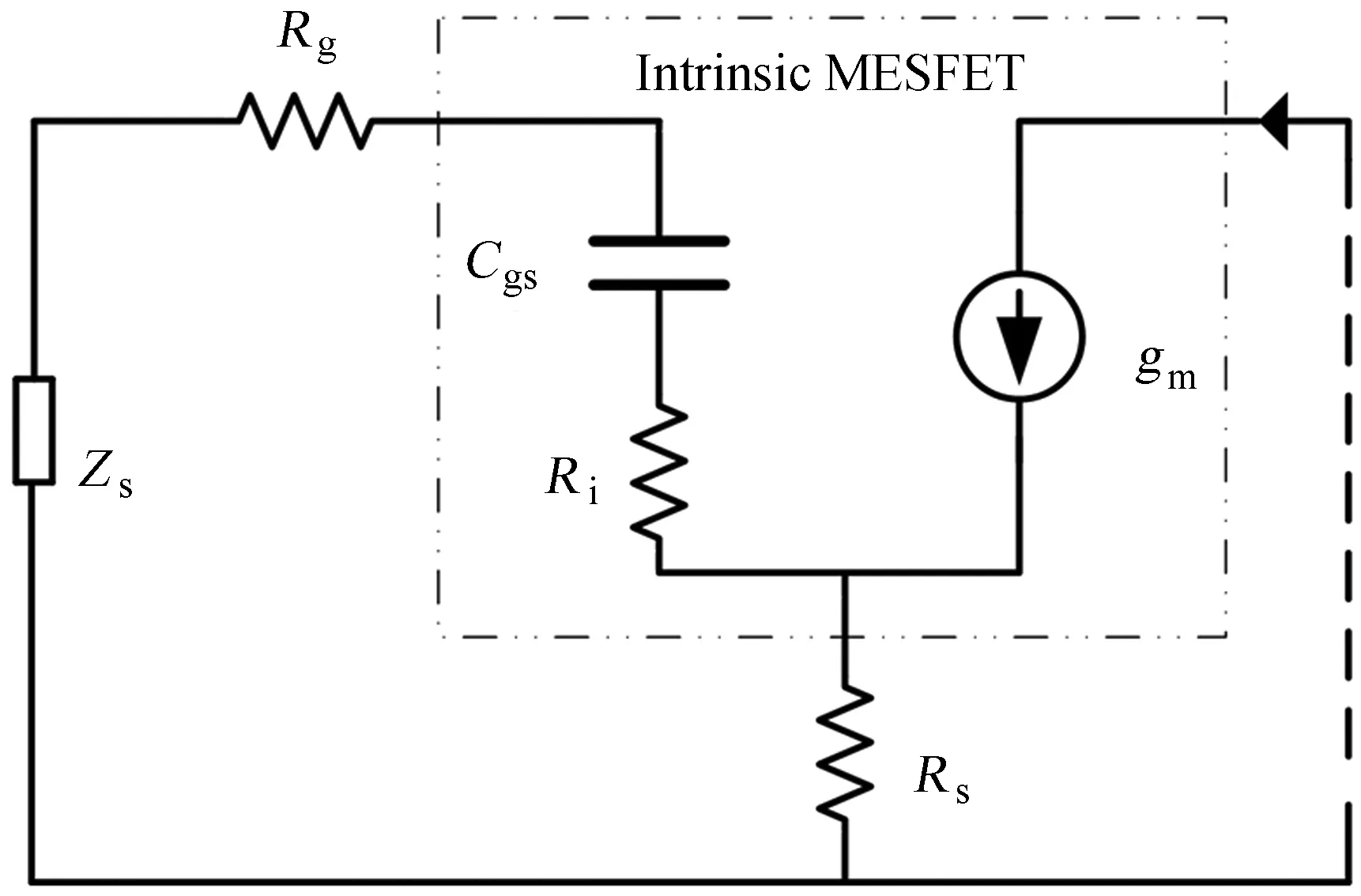

对于多指晶体管:

(5)

其中,fT为晶体管的截止频率;gm为跨导;Rg栅极金属层总电阻;Rg0为单位宽度栅极金属层电阻;W为晶体管总栅宽;Nbd为栅指数;Rs为源极串联电阻。图2给出了OMMIC D007IH工艺三款不同指数的晶体管版图。

图1 砷化镓金属-半导体场效应晶体管的噪声等效电路图

Fig.1 Noise equivalent circuit of GaAs MESFET

图2 单指和多指晶体管版图

Fig.2 Transistors with single finger and multiple fingers

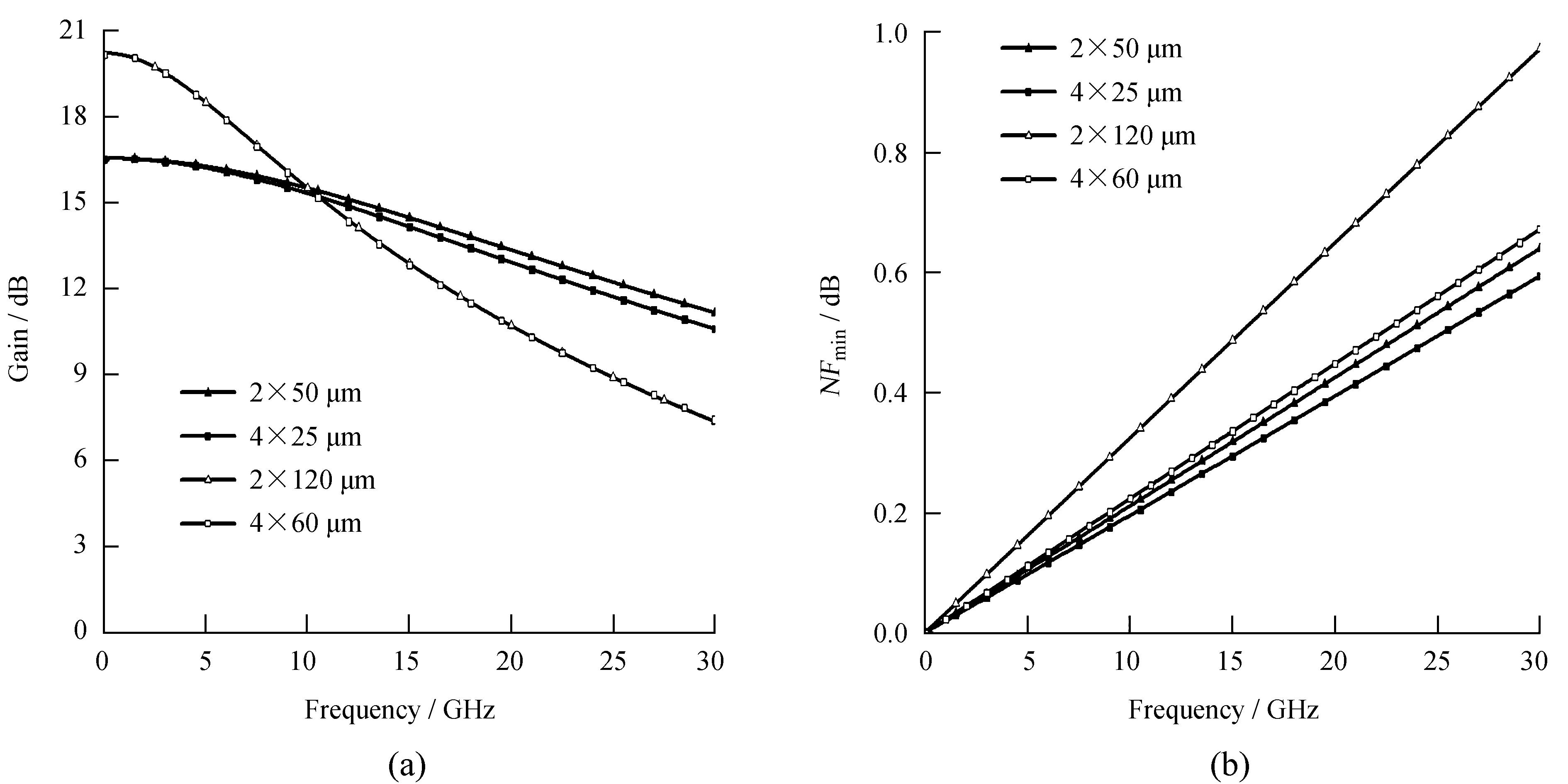

由(3)式~(5)式可知,晶体管最小噪声系数NFmin与栅宽、栅指数均有关,且与总栅宽呈正相关,与栅指数的平方呈负相关,故NFmin随栅指数变化的幅度较栅宽大。利用电子设计自动化仿真软件先进设计系统(Advanced Design System, ADS)仿真对比OMMIC提供的元件库中2 × 50 μm和4 × 25 μm总栅宽为100 μm以及2 × 120 μm和4 × 60 μm总栅宽为240 μm的4种不同尺寸的小信号模型晶体管在相同偏压下的增益和最小噪声系数。从图3可以看到,在总栅宽相同时,2指的晶体管高频增益优于4指,而噪声系数是4指优于2指。当总栅宽增大时,低频增益提高,且随着频率升高增益下降幅度大。同时噪声系数在少指(2指)与多指(4指)之间的差异在高频处更为明显,而增益相差无几。根据高增益、低噪声的指标要求,本文设计选用尺寸为4 μm × 60 μm的晶体管。

1.2 稳定性

射频电路中的有源和无源器件都属于双向元件,所以在有源电路输出端的匹配阻抗会通过晶体管的反向传输系数S12反射回输入端,若反射的信号与由信号源输入的信号同相时,有可能造成放大器电路振荡[4]。稳定性决定了设计的低噪声放大器能否正常工作,所以对稳定性的分析也是设计单片微波集成电路低噪声放大器不可忽略的环节。1962年,文[5]提出了K指数法则判断电路的稳定性:

(6)

(6)式表明,K指数与晶体管等效的二端口网络正向、反向传输系数S21、S12,输入、输出端口反射系数S11、S22都有关,只有在全频带内K> 1且|Δ| < 1时,系统才能称之为绝对稳定,此时放大器的状态不随信号源阻抗和负载阻抗的变化而变化,也不会在输入信号后产生自激振荡。在晶体管源极与地之间串接反馈电感的方式可以改善低噪声放大器的稳定性,而实际在进行电路设计时,通常用微带线代替电感引入少量感性阻抗,既能满足稳定性要求,也方便电路优化。

图3 4种不同尺寸晶体管性能对比。(a) 增益;(b) 最小噪声系数

Fig.3 Performance comparison of four different size transistors. (a) Gain; (b) Minimum noise figure

1.3 直流偏置电路

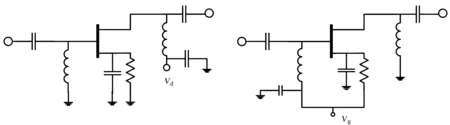

直流偏置电路关系到放大器能否在选定的静态工作点下工作,而不同的静态工作点下晶体管的噪声特性、增益等都有区别。高电子迁移率晶体管(High-Eletron-Mobility Transistor, HEMT)常用的直流偏置类型有单电源供电和双电源供电两种方式。图4的单电源供电拓扑结构中,源极通过负反馈电阻将源端电位调节到所需的电压值,不可避免地消耗直流功率,降低放大器的工作效率[6]。

图4 单电源直流偏置电路拓扑结构

Fig.4 Single power supply DC bias circuit structure

设计低噪声放大器常用图5的双电源供电拓扑结构,其中电感可以防止射频信号进入直流偏置电路,保证电路的稳定性。但是仅仅依靠电感作为射频扼流圈无法完全隔离射频信号,因此为了防止少量射频信号进入直流电源造成电路振荡,通常还需要并联去耦电容以进一步吸收射频信号。输入、输出端常采用隔直电容防止偏置电路中的直流分量进入射频信号。本文设计的电路中,晶体管所加漏极偏压Vd为正电压,栅极偏压Vg为负电压以控制漏极电流。值得注意的是,双电源供电结构需严格控制加电、去电顺序,否则容易造成晶体管由于瞬间超压而损毁。

图5 双电源直流偏置电路拓扑结构Fig.5 Dual power supply DC bias circuit structure

1.4 匹配电路

匹配电路可调节整个低噪声放大器的噪声、增益及其平坦度和输入输出回波损耗。设计低噪声放大器的匹配电路需要考虑输入匹配、级间匹配和输出匹配,从前面对噪声的分析可知,第1级电路的噪声系数对整个低噪声放大器的噪声性能起决定性作用,所以输入匹配采用最佳噪声阻抗匹配方式。级间匹配主要采用最大功率增益匹配,保证电路有足够高的增益,而输出匹配采用最大增益输出匹配方式,同时要考虑输出回波损耗和增益平坦度。各个重要参数之间的变化通常是相互影响、相互牵绊的,所以设计电路时还需要根据实际指标要求进行取舍。

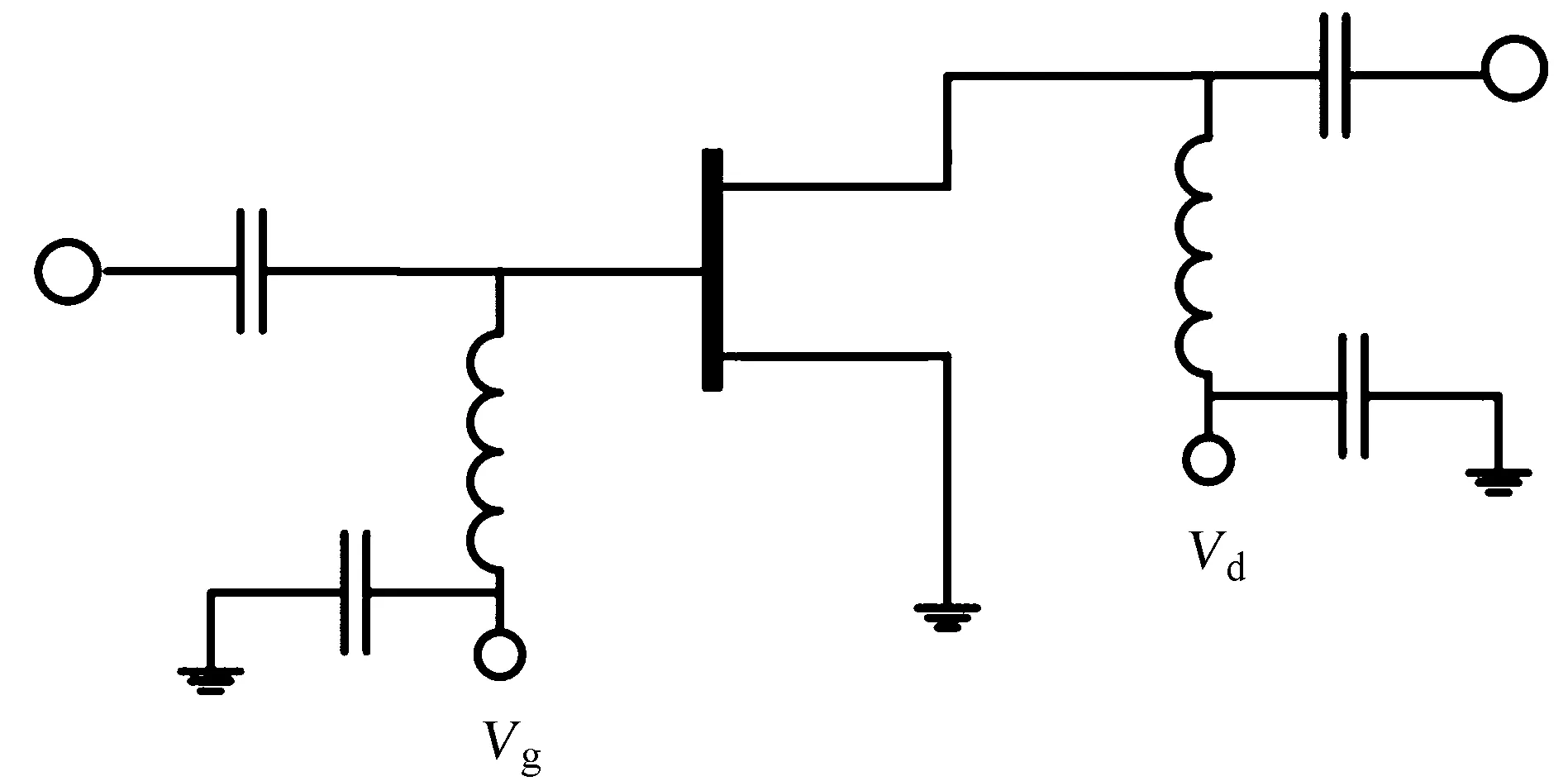

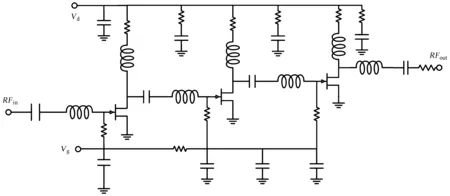

1.5 原理图和版图设计

为了满足增益指标要求,低噪声放大器芯片采用三级级联放大拓扑结构,直流偏置为双电源供电,三级晶体管采用同一Vd提供漏极正偏压,同一Vg提供栅极负偏压。由于晶体管的噪声随着频率而增加,使第1级、第2级、第3级电路分别控制高频、中频和低频增益,如此可保证工作带宽内增益和噪声的平坦度。本文设计的2~18 GHz低噪声放大器芯片电路拓扑结构如图6。射频信号从左端输入,先经过一个大的隔直电容滤除直流杂波,降低噪声。栅极偏压通过大台面电阻给晶体管提供控制电压,同时防止射频输入信号进入直流支路导致信号损耗。漏极供电电路上的电感和电阻不仅起到防止射频信号进入直流电源的作用,其数值对增益和增益平坦度的调节也有非常显著的效果,同时第1级的电阻还对电路的噪声产生影响。源极串接电感可以提高电路的稳定性,对第1级来说,电感值越大,稳定性越高,同时噪声也越大,故为了保证整个电路的噪声性能,尽量取较小的电感值,此时可用一小段微带线替代。级间电容、电感元件除了作为匹配电路的一部分,还能帮助调整增益、噪声和回波损耗的形状。

图6 低噪声放大器电路拓扑结构

Fig.6 The LNA circuit schematic

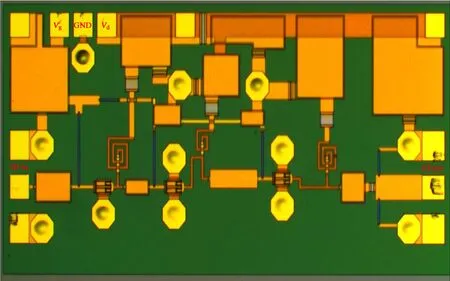

芯片版图的设计要符合半导体公司的设计规则检查(Design Rule Checking, DRC),还要整洁美观紧凑,节省面积,在电路出现问题时方便排查。同时,为了充分利用版图面积并增加电路的稳定性,在直流偏置路径上尽可能并联旁路电容滤除多次谐波。图7为最终流片获得的单片微波集成电路低噪声放大器芯片实物图片,芯片面积为2 mm × 1 mm。

图7 低噪声放大器芯片实物图

Fig.7 Microphotograph of LNA MMIC

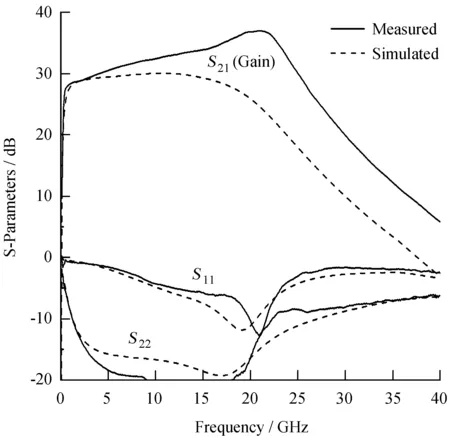

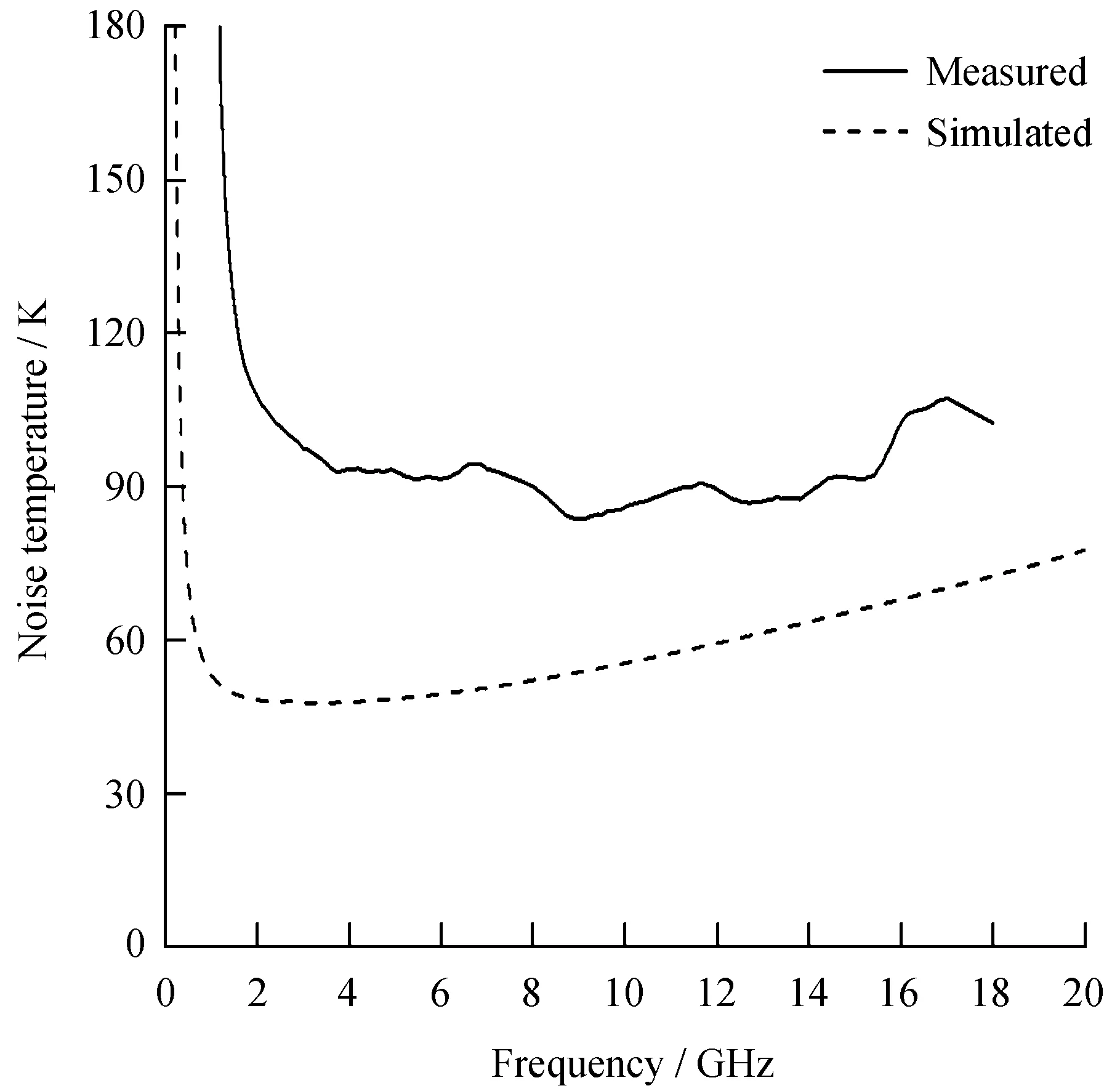

2 常温在片测量结果

常温下,采用微波探针台和矢量网络分析仪等在片测量仪器对低噪声放大器芯片进行测量,在进行多组偏压测量调试后,得到芯片最佳工作状态下的偏压条件为:Vd=2 V,Id=75 mA。此时放大器芯片的增益大于28 dB,输出回波损耗大于13 dB,噪声温度83~108 K。将低噪声放大器芯片S参数和噪声温度的在片测量结果与电磁仿真结果进行对比,图8、图9中虚线为仿真结果,实线为测量结果。从对比图可以看到,该低噪声放大器芯片的反射系数实测和仿真差别不大,而噪声温度在低频处差别较大。造成噪声升高的可能原因有:噪声校准或噪声源本身精确度不够;测量过程使用的探针造成源阻抗匹配效果出现波动;仿真所用噪声模型在低频段不准确等。除了噪声温度差异之外,高频增益也有很明显的抬高现象,不排除元件电磁仿真模型与实际工艺的误差。另外,输入回波损耗与噪声在调节输入匹配时难以同时达到最优,在本次设计中,为了获得低噪声而牺牲了一定的输入回波损耗,故S11在低频段略差。

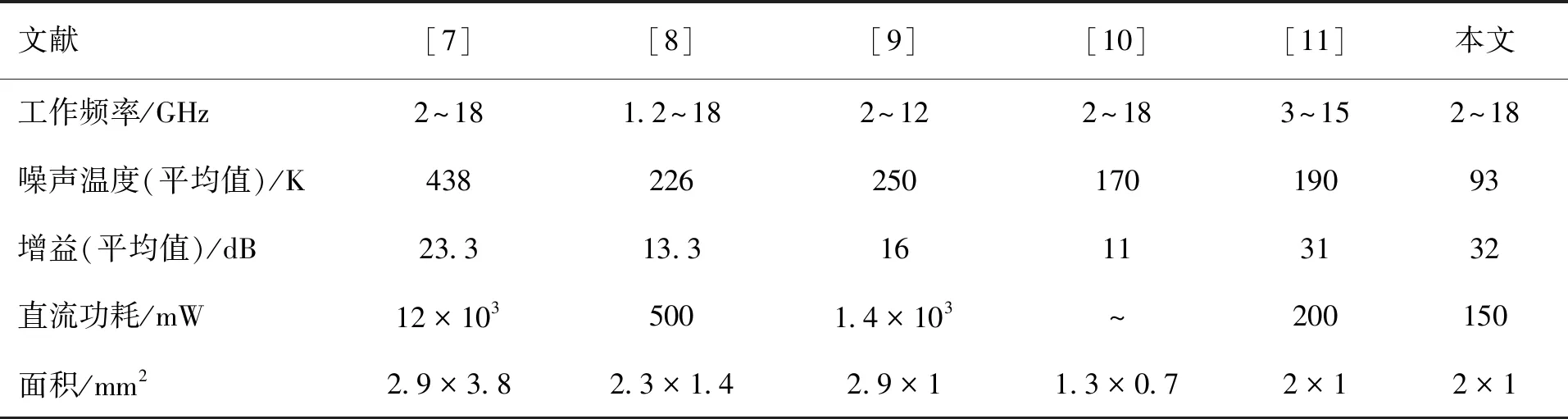

本文与其他文献中相似频段的低噪声放大器芯片的部分参数对比如表1。文[7-9]采用0.25 μm GaN HEMT工艺,文[10-11]采用0.15 μm GaAs pHEMT工艺。由表中数据可以看到,本文设计的低噪声放大器芯片在噪声、增益、直流功耗方面具有一定的优势。

图8 S参数仿真与实测对比图

Fig.8 Comparison between simulated and on-wafer measured S-parameter

图9 噪声温度仿真与实测对比图

Fig.9 Comparison between simulated and on-wafer mesured noise temperature

表1 本文与其他文献中的低噪声放大器芯片主要参数对比Table 1 Main parameters comparison of LNA in this paper and others

3 结 论

本文采用OMMIC公司70 nm GaAs mHEMT工艺设计了一款2~18 GHz超宽带单片微波集成低噪声放大器芯片。该芯片电路采用三级级联放大、单管共源和双电源供电结构,根据最优噪声输入匹配和最大功率输出匹配进行设计,并在输入回波损耗和噪声性能两者中进行了一定的取舍。在Vd=2 V,Id=75 mA的偏压下获得了大于28 dB的增益、小于108 K的噪声温度及良好的输出匹配。本文设计的超宽带低噪声放大器芯片可以用于国际上正在开展的超宽带接收机研究,具有代表性的是国际天文组织IVS(International VLBI Service)正在推动的2~14 GHz下一代全球大地测量观测系统VGOS(VLBI Global Observation System)和欧洲VLBI网正在推动的1.5~15.5 GHz下一代VLBI观测系统。