嵌入式存储器控制器设计中FPGA与VHDL的应用研究

2019-07-09郭慧莹

郭慧莹

摘 要:存储器是保证计算机正常运行的重要组成部分,实现计算机的数据存储工作,传统的存储器控制器存在着运行效率低、不可重复编写的问题,为此,提出一种基于FPGA的嵌入式存储器控制器设计方案,探讨了存储器控制器的构造,设计了四种形态的状态机,可以实现相互之间的自由转换,以VHDL语言作为程序编码的语言,实现对存储器控制器的控制,最后以ISE Simulator Lite软件进行仿真模拟,证实了设计的存储器控制器能够实现数据的读与写操作,同时效率高、可擦写。

关键词:嵌入式存储器;控制器;FPGA;VHDL

信息化时代计算机在各行各业中的地位越来越重要,使得计算机技术得到了快速的发展,与此同时存储器在计算机系统中的作用也逐渐加大。计算机系统中包含了规模庞大的处理器,每一个处理器均要与存储器建立连接实现信息的交互,由此可以看出存储器是计算机的核心部件,影响着计算机的性能发挥。传统的存储器控制方法存在着灵活性差、无法擦写的问题,为此,本文分析了一种基于FPGA的改进存储器控制方法,克服了传统控制方法中的弊端,并引入VHDL语言进行程序的编写,进而实现处理器与存储器信号的有效传递。

一、基于FPGA和VHDL的存储器控制器设计

在进行存储器控制器的设计过程中,第一步需要将相关数据参数传输到控制器部分,其中参数包含了数据的地址、内容以及长度等,控制器将接受到的信号按照先后的顺序进行各个数据的读与写操作。所以,为了满足上述的要求需要设计一个可以对内部程序进行编写的存储器控制器,控制器依据设定的程序代码逐个完成数据的读与写工作。[1]本文设计的存储器硬件设备选用塞林思公司的Spartan-6系列,并使用VHDL进行控制器语言的编写,借助有限状态机FSM完成存储器控制器。另外,还需要在存储器控制器中添加读数装置,从而实现对时序图中所包含的数据进行逐个计数,连接线路用来实现数据地址和内容的运输。如图1为控制器的构造。

配置寄存器是存储器中结构中的一部分,其实现的功能是帮助存储器确定存储形式、字长以及时序参数等方面的内容,通过行业标准查询手册可以看到,配置寄存器的数据读取时间为8ns,假设控制器的工作效率为100MHz,也就是工作周期为10ns,那么配置寄存器数据读取的总时长为1拍的时间。结合时序图以及相关参数可以得到数据读取触发的时间大于8ns,由此可以推理出数据读取觸发的周期必定大于1拍。[2]

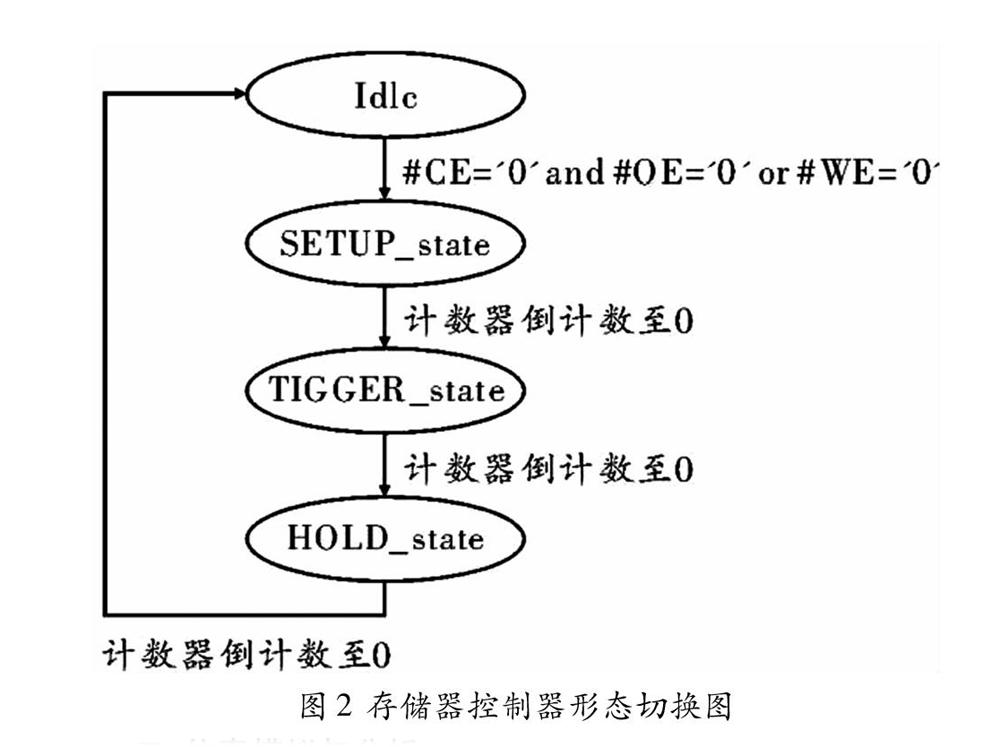

根据上述的理论推理与数据参数,设计了四种形态的状态机,每个状态机的保持与切换均是由计时装置的节拍数进行倒计时来进行控制的,当计数器的数值不为零,那么状态机将保持现状不变,当计数器的数值为零,那么状态机将切换到下一形态。[3]形态切换图见下图2,其中图中所显示的形态文字与第二形态是相同的。

二、仿真模拟与分析

总结上文设计中的理论分析与数据计算,代入到嵌入式存储器控制器中,同时以VHDL语言作为程序编码的语言,实现对存储器控制器的控制,以ISE Design Suite 14.7软件为设计平台,以FPGA为硬件设备,完成程序的下载工作。另外,运用Xilinx软件中包含的ISE Simulator Lite功能进行程序模拟,最终获得的时序图和设计标准手册中的时序图相符合,因此可以得出设计出的存储器控制器能够实现对数据的读与写操作,证明该存储器控制器设计方案是可行的。[4]

三、结语

本文对基于FPGA和VHDL的存储器控制器设计,设定FPGA为嵌入式存储器的控制装置,可以完成对时序控制器中数据的读与写步骤,这种设计思路新颖,不但能够有效降低制作成本,同时还可以保证控制器具有较高的可编辑性,解决了专用控制器中复杂操作的问题,改善了存储器控制软件的运行速度,为今后的存储器控制器设计提供了宝贵的经验。

参考文献:

[1]史展,李占宣.基于FPGA的嵌入式CPU的VHDL设计[J].科技创新与应用,2013(27):43.

[2]李家星.嵌入式系统和FPGA的总线控制器的设计实现[J].微计算机信息,2007(02):242-243+285.

[3]周荣.基于FPGA的嵌入式CPU的VHDL建模和设计[J].浙江工业大学学报,2006(05):550-553+588.

[4]曹志香,桑爱兵,丁黄胜,张萌.基于AMBA总线的嵌入式彩色LCD控制器的设计及FPGA实现[J].电子器件,2004(01):139-142.