带二级密勒补偿的运算放大器研究

2019-07-02魏昱嵩

魏昱嵩

摘 要: 介绍了带二级密勒补偿的运算放大器的电路原理和分析方法,同时设计了一个二级运放并得到了仿真结果,仿真结果表明补偿电路提高了放大器的增益带宽,设计的电路功耗较低,负载较大。

关键词: 二级运算放大器;二级密勒补偿;仿真

中图分类号: TB 文献标识码: A doi:10.19311/j.cnki.1672-3198.2019.13.093

1 引言

模拟电路中的运算放大器被应用在模拟计算机中,在线性、非线性和频率相关的电路中进行典型的数学运算。最早期的有放大功能的电路是由真空管组成的电路结构,真空管的体积比较大,要占用比较大的面积,功耗较大。随着电子技术的发展,出现了由晶体管代替真空管的放大器。集成电路工艺的发展,出现了更小尺寸的芯片来代替较大尺寸芯片实现同样的功能,电路结构的电源电压的不断降低和电路结构对最大承受电流的、低功耗的要求,低压低功耗高增益的二级运算放大器的设计在集成电路领域变得越来越重要。

模拟电路中运算放大器的设计一般分为三个步骤:第一,进行原理图的设计,选择设计所选用的晶体管和各个电路器件,绘制出原理图;第二,参数的估算,根据所要求给定的参数,总体上估算出电路中元器件的参数数值;第三,仿真验证,验证实际数值是否与估算值有相差,如果有相差,我们需要进一步分析导致偏差的原因,通过微调电路结构或者元器件的参数最终得到满足设计功能要求的电路图。

2 二级运算放大器的典型的电路结构

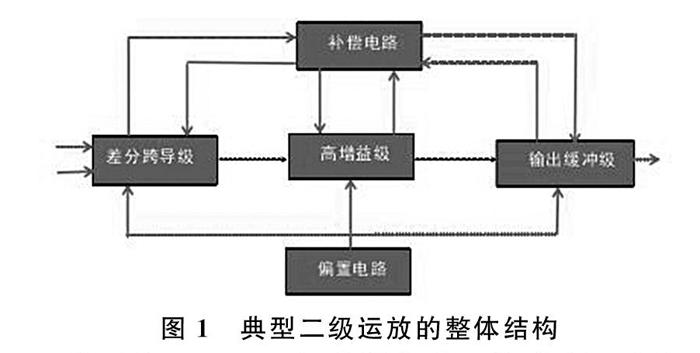

CMOS运放的差分跨导级构成运放的输入级,同时达到了双端差分输入变换到单端输出的效果。通常,整个电路的增益、大部分都是差分级和第二级提供的、可改善噪声性能和降低输入失调。输出缓冲级一般采用反相器,当差分输入级没有完成差分-单端变换时,就由缓冲级的反相器来完成。偏置电路是用来给电路中的各个晶体管建立适当的静态工作点的。另外,通过采用密勒补偿和增加调节零点的电阻来稳定闭环特性。图1给出了典型的二级运放的整体结构。

2.1 典型的CMOS二级密勒补偿运算放大器结构

如图1所示,电路结构主要包括:第一级差分输入级放大电路第二级放大电路、偏置电路和相位补偿电路。M1~M5组成运放输入级,M1和M2组成差分输入对,可以抑制共模信号和噪声的干扰;M3、M4为有源负载;M5为第一级提供恒定偏置电流;输出级放大电路由M6、M7组成,M6为共源放大器,M7为其提供恒定偏置电流,同时作为二级输出负载。相位补偿由M14和Cc实现。M14工作在线性工作区,可以等效为一个电阻,调节零点的位置。

2.2 采用密勒补偿实现电路的稳定性

高直流开环增益和大输出电压摆幅的运算放大器需要频率补偿。采用密勒补偿时,补偿电容在第一增益级的输出和第二增益级输入之间,与第二增益级的输入和输出节点相关的两个极点被分开,电容同时提供了一个前馈信号通路,引入了一个右半平面零点。通过增加与补偿电容串联的电阻可以消除这个右半平面零点。

2.3 静态特性分析

常见的两级运放的典型结构是差分放大器作为运放的输入级,可以达到比较好的抑制噪声的作用并且提供比较大的增益,第二级是共源级放大器,提供比较大的摆幅。偏置电路用于给提供高增益的第一级和补偿电路提供偏置用的电流和电压,补偿电路和调零电阻通过改变零极点的位置,使电路达到较好的稳定性。第一级的运算放大器根据输入结构的不同,也可以是套筒式和折叠式。套筒式共源共栅运算放大器由于输入摆幅小,不利于闭环使用。折叠式共源共栅运算放大器的输入摆幅和输出摆幅都相对高一些,能够闭环使用。因此使用范围更广泛,但这些优点是以损失增益为代价的。暂时不考虑调电阻M14 ,绘出电路的电路模型,如图4所示。

由于第一级差分输入对管M1与M2相同,有

Gm1 = gm1 = gm2

R1表示第一级输出电阻,其值为

R1= r02 ||r04

则第一级的电压增益

A1 = Gm1R1 = gm2(r02||r04)

对第二级有

Gm2 = gm6 =2IDS6/VGST6

R2 = r06||r07

第二级的电压增益

A2 = -Gm2R2 = -gm6(r06||r07)

故总的直流开环电压增益为

A0 =A1A2 =-gm2 gm6 ( r02 || r04 )( r06 || r07)

3 设计的带密勒补偿的二级运放电路

3.1 二级运放电路的设计

Candence软件中搭出下面的原理图后生成symbol,利用symbol搭建仿真平台,用spectre仿真来得到电路的性能参数。

上图设计中M0、M13、M12、R0为偏置电路级,M26是运放的启动电路。M5、M6、M7、M8M9为第一级输入放大电路,M10、M11为第二级输出放大电路,C0是密勒补偿电容,R1是调节零点所在频率位置的电阻。

电路中MOS管的尺寸、电阻、电容的大小见表1。

3.2 电路特性测试

图6~图9中,负载电容为500fF。

3.3 仿真结果

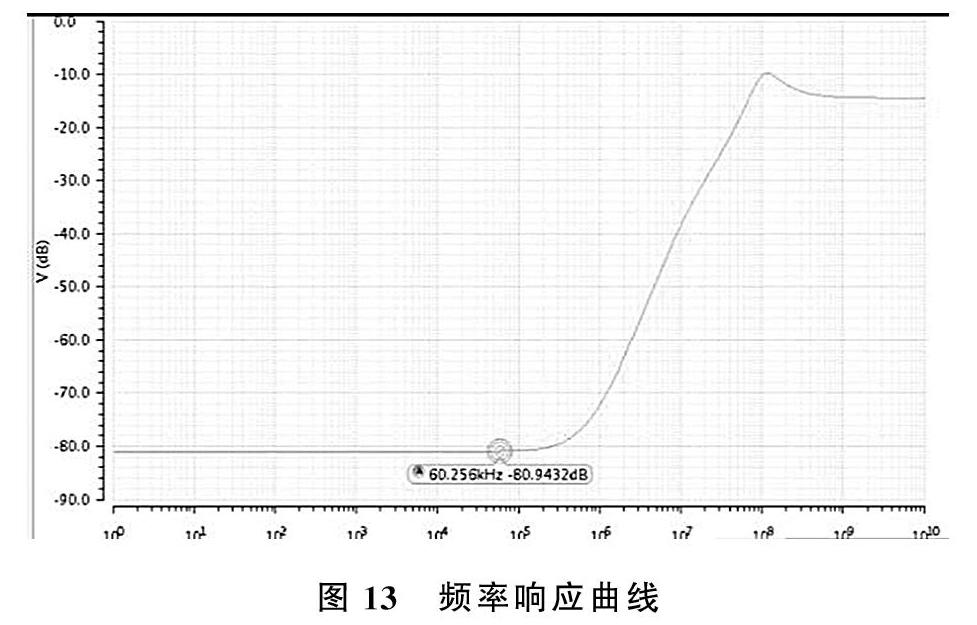

运算放大器在共模输入电压355mv条件下,直流开环增益为75dB,相位裕度达到了89度,低频电源电压抑制比为104.5dB,低频共摸抑制比为80.9dB,运放的单位增益带宽达到了13.195MHZ。

4 结论

本文的运算放大器的共模输入电压是355mv,直流开环增益为75dB,相位裕度达到了89度,运放有很好的稳定性,低频下电源电压抑制比为104.5dB,低频下共摸抑制比为80.9dB,运放的单位增益带宽是13.195MHZ。

参考文献

[1] 栗晶晶,张智容.集成电路的现状及其发展趋势[J].科学论坛,2014.

[2]张汝京等.纳米集成电路制造工艺[M].北京:清华大学出版社,2014.

[3]孙肖子.张健康.专用集成电路设计基础[M].西安:西安电子科技大学出版社,2011.

[4]王阳元.集成电路工艺基础 [M].北京:清华大学出版社,1991.

[5]迪建.中国集成电路产业发展机遇与挑战[J].集成電路应用,2015.

[6]俞建风,陈翔,杨雪瑛.我国集成电路测试技术现状及发展策略[J].中国测试,2009.

[7]王永刚.集成电路的发展趋势和关键技术[J].电子元器件应用,2009.