基于NetFPGA的网络流量分组方法设计与实现*

2019-07-01曾小宝李晓锋肖卓朋

曾小宝,李晓锋,宋 锐,肖卓朋

(张家界航空工业职业技术学院,湖南 张家界 427000)

0 引言

高速网络的出现对传统网络信息处理技术是一个巨大的挑战。现有的网络信息处理技术有软件和硬件两种方式,采用软件实现成本较低,灵活性较高。缺点是软件方式通常会受CPU,操作系统,计算机结构体系,系统资源等的限制,在性能上难以适应现有高速网络的需求。采用硬件实现方式具有速度快,稳定性等优点,从相关文献得知现有采用硬件实现方式是采用专用集成电路(ASIC)来实现,其缺点是专用性较强,灵活性较差,不能得到广泛使用。结合硬件和软件各自的优点,斯坦福大学开发的网络FPGA(NetFPGA)用来处理网络信息是较好的选择[1]。

1 NetFPGA概述

NetFPGA起源于斯坦福大学的Nick McKeown教授领导的研究小组开发设计的一个软硬件皆可编程的开放平台[2]。从2007年开始在国内外掀起了学习和研究热潮,它的出现将硬件的可配置性带入到网络信息处理方面进行硬件加速,研究人员很容易在此平台上搭建高速网络信息处理模型[4]。最新NetFPGA处理速度可达万兆,从而进行网络系统的研究和测试,突破了传统网络信息纯软件处理速度不高的瓶颈[5]。目前,美国多数高校里已经开设了基于NetFPGA平台的路由器设计和高速网络设计实验课程。在国内,NetFPGA才刚刚起步,具有很好的发展前景,现在越来越多的大学和科研院所开始进行研究,台湾中原大学“基于NetFPGA之流量变异侦测系统”,通过速写(Sketch)演算法清晰的构建了时变异常检测系统,达到线速处理网络流量的目标[6]。

2 NetFPGA平台架构

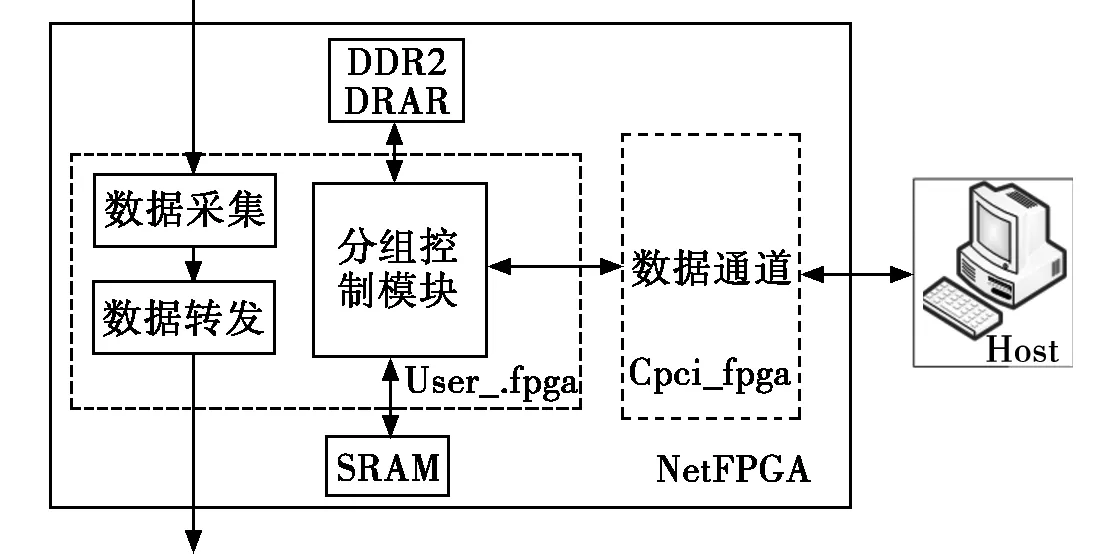

NetFPGA初期硬件原型主要实现网络数据包的解包,负载的扫描分组等功能,并能很好的支持模块化的设计,通过调用各个子模块和用户自己编写模块可以实现较复杂的硬件功能设计。因此,可将此平台应用于网络攻击检测,负载均衡,流量控制等网络硬件加速研究。NetFPGA结构框图如图1所示。

3 基于NetFPGA的网络流量分组方法设计

具体设计如下:从网络上采集数据,数据采集模块采用赛灵思公司开发的IP核TEMAC来实现,采集到的数据访问分组控制模块,得到通过与否信号,决定数据分发到相应的组别,分组控制模块包括特征提取,SRAM的读写,DDR2SDRAM的读写,SRAM用于网络特征的缓存,每隔一定时间以块的形式通过数据通道发送给上位机显示。分组控制模块接收上位主机下载的规则集,按上位主机封装规则进行逆向解析,得到IP地址和相应的分组控制位,并以此IP地址为DDR2存储器的写地址,将分组控制位写入DDR2的位存储空间。直接利用提取到的源IP去访问DDR2,读取相应的分组控制信息,最后分组控制模块输出分组控制信息,决定数据包分到哪一个类组,实现基于IP地址的数据包分组。

图1 NetFPGA结构框图

图2 网络数据包分组方法系统框图

4 基于NetFPGA的网络流量分组方法实现

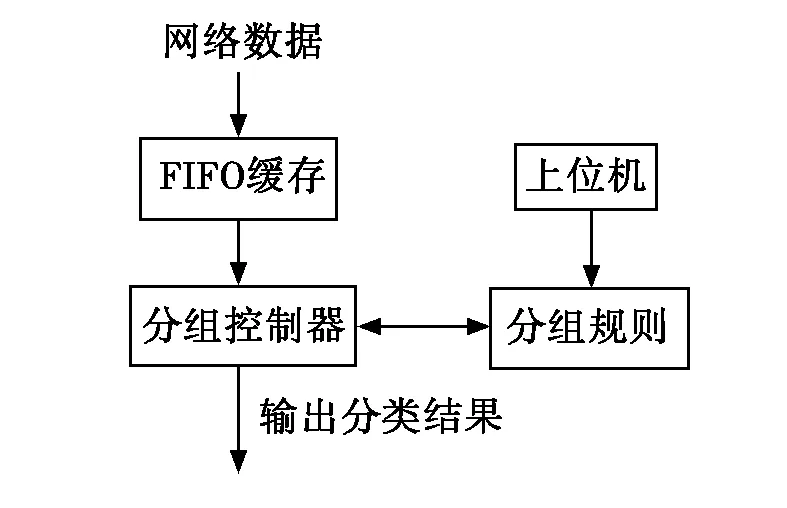

首先从网络上采集到的数据放入FIFO(先进先出队列)进行缓存,其次再将网络数据流送分组控制器,并且依据分组规则进行分类,分组控制器完成分组规则的访问,需要不断的读分组规则,最后输出分类结果,上位机可通过PCI_DMA直接访问的方式将分组规则置入DDR2存储器,也可通过PCI_IO的方式置入。上位机可实时统计显示网络特征,动态配置分组规则集。具体框图如图3所示。

◆FIFO缓存模块:流水线技术是指将一个逻辑功能分割成多个阶段的过程,每个阶段执行一小段逻辑功能。这样处理可提高执行的速度,对整个系统来说,可提高吞吐量,可以允许更高的工作频率,动态的提高了设计性能,但是为了使流水线的性能达到最佳,当采用了多级流水线之后,数据通路变成了多时钟周期通路,必然会带来一定的延时,要进行严格的周期约束,逻辑规模要均衡。在Router HW设计中采用5级流水线模块化设计方法,在数据通路几乎每个模块都设计一个同步FIFO,以实现数据包的缓存。从而不必过多考虑时序约束,专注于模块内部功能的实现,给开发带来极大的便利。

图3 分组方法框图

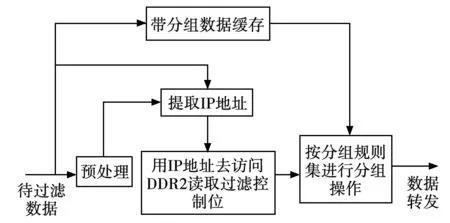

◆分组控制器模块:根据FSMD数据和逻辑控制两部分的思想设计出分组控制方法,设计出分组控制逻辑结构图如图4所示。

图4 分组控制逻辑结构图

待分组数据进入FIFO进行缓存,与此同时进行预处理,预处理的目的是一个状态转移机。根据数据包内容确定在哪个状态下进行IP地址的提取,根据预处理的标记结果启动后面的IP地址提取,数据缓存和提取IP地址是并行执行的,提取到的IP地址再去访问DDR2读取分组控制位,依据读取到的分组控制位如“1”数据包通过,“0”数据包不通过,修改相应数据包信息,以便后续电路对其转发到不同端口。要注意的是:在数据包转发时,对缓存的数据包读取要注意其时序,所用FIFO采用异步的方法控制其读信号。

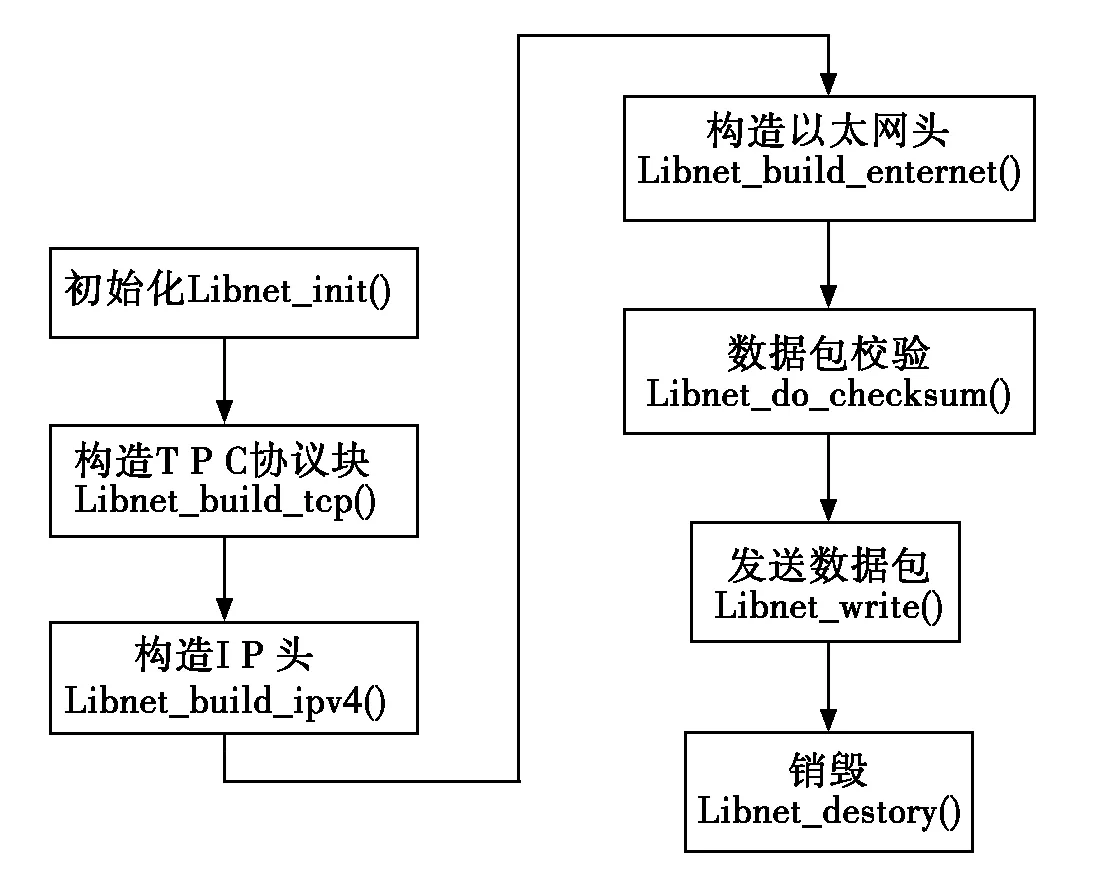

◆上位机下载分组规则:数据包的传输分为帧的发送和接收,对于硬件和驱动来说都是通过PCI接口以DMA的方式进行数据的收发。在应用程序实现上可以有两种方式:一种是利用Linux下网络工具包Linpcap和Libnet分别进行数据包的捕获和发送;另一种是直接对网络接口进行数据包操作。Libpcap是Linux下的网络数据包捕获函数包,可以对网络进行监听,但不能拦截数据包。它是在操作系统内核的数据链路层添加旁路电路实现,并不影响网络协议栈工作,可以用来监听NetFPGA各个网口数据流量等操作。Libnet是Linux下用于数据包构造和发送的函数包软件,只需把NetFPGA作为一块普通的网络接口来操作即可。本文配置分组规则就是采用Libnet软件把大量分组IP和所对应的分组控制位封装成IP数据包的形式,通过PCI_DMA方式下到FPGA中,其封装过程流程图如图5所示。

图5 封装过程流程图

5 结论

为了验证基于FPGA的网络数据包分组系统设计性能,本文的实现是采用斯坦福大学的NetFPGA2.1开发平台来实现其原型系统,通过ISE软件编写Verilog描述语言对各功能模块进行描述,使用ModelSim软件进行仿真,结果表明分组效果较软件方式具有较高的准确率。