基于FPGA的交换结构研究与实现

2019-07-01黄玉萍史陆星

曾 光,黄玉萍,史陆星

(广东交通职业技术学院,广东 广州 510000)

0 引言

交换结构是影响交换效率的关键因素之一,良好的交换结构设计有助于提升系统的交换效率。从其构成而言,可分为单级交换结构和多级交换结构,其中单级交换结构主要包括共享总线结构、共享缓存结构、单级Crossbar结构等,多级交换结构主要包括Banyan网络、Benes网络、Clos网络等[1]。

本文通过对单级交换结构和多级交换结构的比较分析,结合两者优势,改进相关交换结构,使其结构性能与交换系统的适配度最高,并在交换结构设计完毕后,在基于Xilinx公司Virtex-6系列FPGA平台上搭建交换系统,将新设计的交换结构应用其中,进行仿真实现。

1 单级交换结构

单级交换结构,即整个交换系统中只有一个交换单元的结构,主要包括共享总线结构,共享缓存结构,单级Crossbar结构等,综合论文[1-4]的内容,这三种类型的单级交换结构各自的优劣性如表1所示。

2 多级交换结构

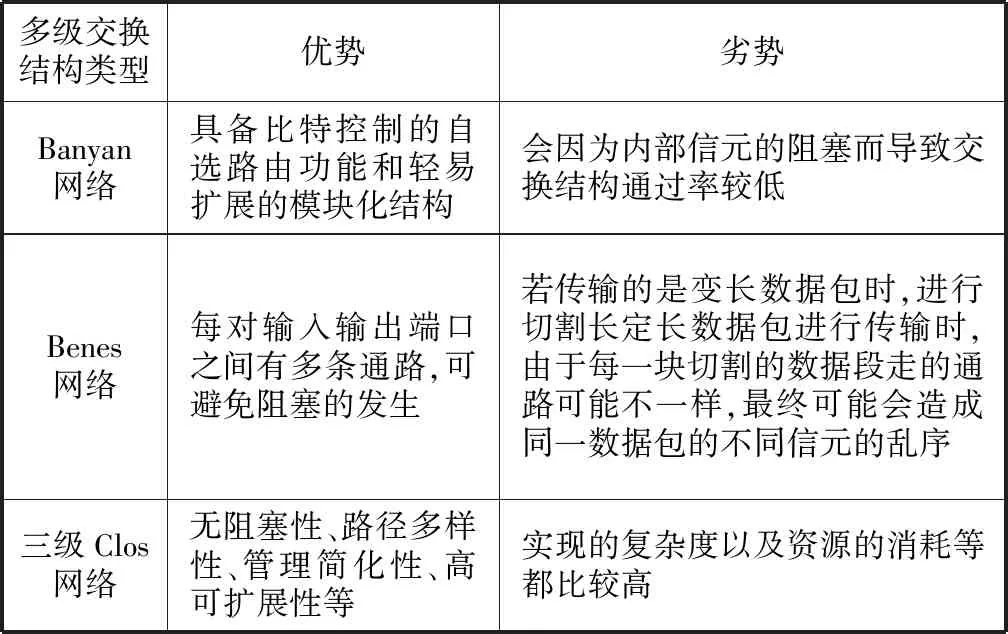

多级交换结构,即由多个单级结构的交换单元联合成的多级交换阵列,从而获得交换机端口和吞吐量成倍增加的效果,常用的多级交换结构主要有Banyan网络、Benes网络、三级Clos网络等,综合论文[1,5]的内容,这三种类型的多级交换结构各自的优劣性如表2所示。

表1 单级交换结构优劣性比较

表2 多级交换结构优劣性比较

3 交换结构的设置

通过上述内容中对各单级、多级交换结构的比较分析,我们可以知道多级交换结构的平均时延较大,而单级交换结构及其配套的调度算法已相对成熟,因此,结合本系统的目标数据包为变长数据包,最终选择的交换结构是改进版的Crossbar交换结构:缓冲交叉式交换结构(Buffered Crossbar)。

Buffered Crossbar交换结构所做的主要改进就是在Crossbar交换结构的每一个交换节点增加了一个缓存,即每一个输入端口传输数据包到对应的所有输出端口都需要经过一个对应的缓存,其结构如图1所示[6]。

图1 6×6的Buffered Crossbar交换结构

数据包通过Buffered Crossbar交换结构实现交换的过程大体可描述为以下三个步骤:

1) 数据包首先进入交换系统的输入端,然后通过输入缓存机制,将数据包分类放置在对应的输入缓存中;

2) 输入仲裁器根据调度算法,将对应输入缓存的数据包存储到Buffered Crossbar交换结构中对应的交叉节点的缓存中;

3) 输出仲裁器根据调度算法,读取对应Buffered Crossbar交换结构中交叉节点缓存的数据包传输至输出端口,实现输入端口与输出端口之间的数据包传输。

正因为Buffered Crossbar交换结构的缓存功能,使其具有类似于提升了对队头阻塞的容忍能力的优良性能,从而被认为此交换结构更适用于变长数据包的交换,并且能够极大的简化调度算法。

4 在Virtex-6平台上仿真实现

以Xilinx公司的Virtex-6为核心的FPGA单板,是交换系统整体实现的物理平台,交换系统的缓存机制、路由查表、系统结构、调度算法等核心模块均在此平台上实现,是决定和体现交换系统整体性能的核心板块。

交换系统相关的缓存机制、路由查表等核心模块的原理与设计等内容,由于篇幅限制,不再展开介绍其中核心的调度算法[7]。在交换结构之前,我们先对数据缓存机制进行选择。

输出缓存机制的局限性就在于对高速数据的限制,在这方面的提升或者改进等都会增加交换结构、调度算法的复杂度,而输入缓存机制适应于高速的交换系统,其队头阻塞的局限性可以通过已有的虚拟输出队列(Virtual Output Queueing,VOQ)缓存策略来得以解决[8],因此,最终本系统所选择的缓存机制为输入缓存机制VOQ。

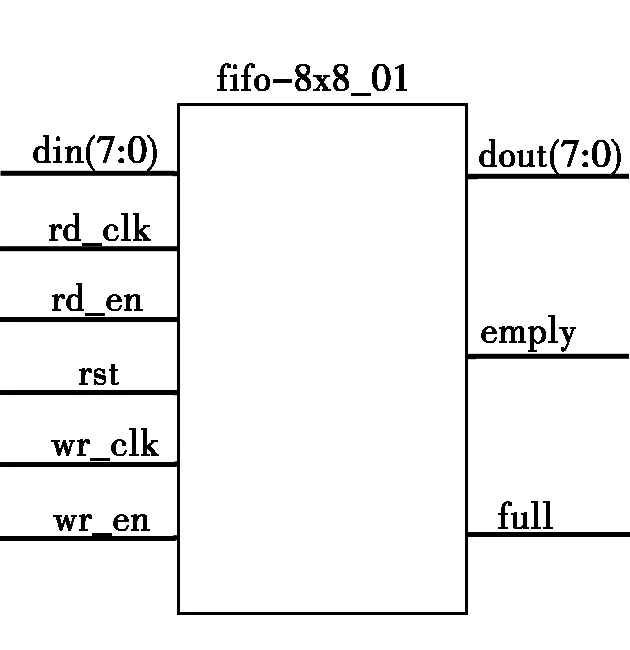

VOQ与Buffered Crossbar结构可以采用的存储单元有随机存储器(RAM)和先进先出存储器(FIFO)两种,其中RAM的地址管理较为复杂,而VOQ与Buffered Crossbar结构中对存储单元的操作主要就是通过控制地址指针来读取对应存储单元的内容,因此,为了降低设计的复杂度与提升交换效率,需要选择地址管理较为简单的存储单元。FIFO是常用的数据缓存单元,按照先进先出的次序对数据进行堆栈操作,地址管理简单,并且集成的FIFO核已经很成熟,对读写控制、空满状态等的实现,已变的很简单,所以,结合Virtex-6本身的优良性能,在本系统的VOQ与Buffered Crossbar结构中,我们采用FIFO作为它们的存储单元。图2所示为FIFO模块。

图2 FIFO模块

图2所示的din[7:0]为8位的数据输入总线,rd_clk为FIFO读取数据的控制时钟输入端,rd_en为FIFO读取数据的使能信号,高电平有效,wr_clk为FIFO读取数据的控制时钟输入端,wr_en为FIFO读取数据的使能信号,高电平有效,empty为FIFO为空的状态指示信号,高电平表示为空,full为FIFO为满的状态指示信号,高电平表示为满,dout[7:0]表示8位的数据输出总线。FIFO各信号之间的控制逻辑如图3所示。

图3 FIFO内部逻辑框图

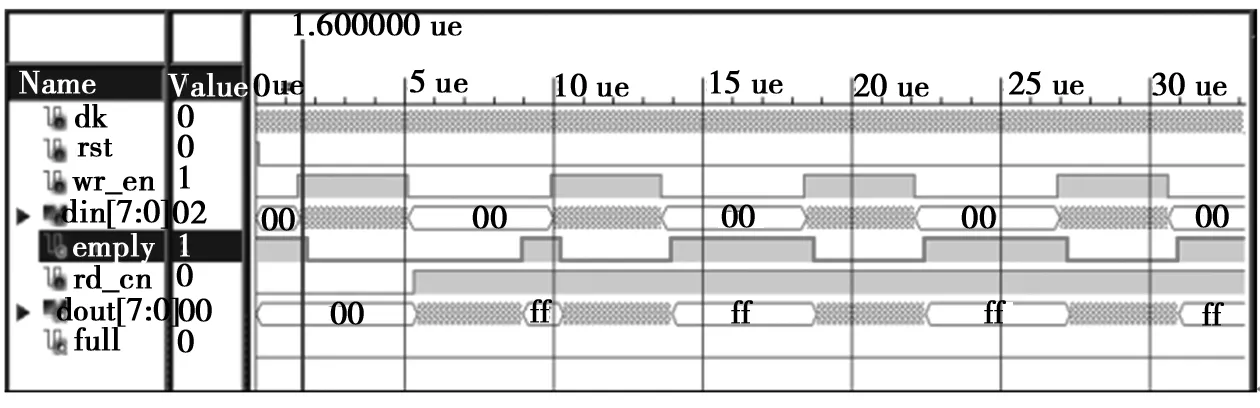

按照上述逻辑对FIFO进行功能仿真,可以得到如图4所示的仿真结果。

图4 FIFO仿真波形

如上图所示:

1) 当wr_en为高电平时,din开始输入数据,并且随着din数据的输入,empty跳转为低电平,即表示此时FIFO为非空;

2) 当rd_en为高电平时,dout开始输出数据,并且当数据输出完毕之后,empty信号跳转为高电平,表明FIFO为空,此时FIFO的输出保持着最后一个输出的状态(16’hff),直至empty再次跳转为低电平时,继续开始输出FIFO中的数据。

3) 因为FIFO一直没有被存储满,所以full状态一直为低电平,即表示还可以继续写入数据。

因此,我们可以根据此仿真结果知道,FIFO的各项功能正常,即VOQ与Buffered Crossbar结构的存储单元模块功能正常。

5 结束语

本文通过对单级交换网络和多级交换网络的比较分析后,采用了改进版的Crossbar交换结构,即缓冲交叉式交换结构(Buffered Crossbar),然后在基于Xilinx公司Virtex-6系列的FPGA平台上,对这个交换结构进行仿真实现,仿真的结果表明此方案在本系统具有确实可行性。但由于交换系统的限制,暂未搭建大量数据交换的实验进行优劣性比较,这将会在后续的实践过程中进行完善。