在FPGA上实现及优化加速卷积神经网络的方法

2019-06-21郑文凯杨济民

郑文凯 杨济民

( 山东师范大学物理与电子科学学院,250014,济南 )

卷积神经网络(Convolutional Neural Network,CNN)是一类人工神经网络,它可以自动从大规模数据中学习特征,并把结果向同类型数据泛化,在语音识别、图像识别、图像分割、自然语言处理等领域广泛应用[1,2].

由于CNN特定的计算模式,现有大部分CNN的设计实现都是基于GPU等硬件的支持,比如INVIDA公司的硬件加速显卡,其就是围绕GPU布局设计的,但是该芯片功耗较大、过大的体积很难适用于移动平台;对于通用处理器CPU而言,其在处理并行数据上效率较低;虽说使用ASIC平台设计具有可定制化的优点,但是成本高昂,产品的可迁移性低[3];而现场可编程门列(FPGA)具有丰富的片上硬件逻辑资源、灵活的线路连接特性以及良好的内存带宽等优点,相比于ASIC而言,更是省去了流片过程,因此在本研究中我们选择使用FPGA来设计该AI芯片.

在一项对于在CPU及GPU上实现CNN的工作中,我们可以清晰的看到在整个CNN网络进行前向传播的过程中,卷积层所耗费时间的比例是很高的[4],所以我们的首要目标就是去优化加速卷积操作. Stylianos等人提出一种以SDF计算模型为基础的框架[5],我们借鉴了该SDF模型以经典的用于识别手写数字集MNIST的CNN网络Lenet-5为例在FPGA开发板上进行了实现,该方法不局限于仅实现固定结构的CNN,我们采用IP核互联以及数据流的方式可以动态调整网络结构以及参数,具有较强的灵活性与通用性.

1 卷积神经网络的基础知识

1.1卷积层卷积层是卷积神经网络的核心,大部分的计算量都在这个层,具体的卷积操作我们可以通过以下两个公式来理解,

(1)

Output=(N-K+2×padding)/stride+1.

(2)

1.2池化层池化层也叫作子采样层,其作用就是减少特征图的空间尺寸、减少参数进一步达到控制过拟合的作用. 池化层并不会对于特征图的深度有影响.还是会保持原来的深度.

1.3全连接层全连接层一般在整个神经网络结构的末层,该层中的每一个神经元节点与上一层的神经元结点是全连接的,目的是将前面层提取到的特征进行综合.

1.4Lenet-5的网络结构LeNet-5[6]共有8层,按次序分别为输入层、C1卷积层、S2池化层、C3卷积层、S4池化层、C5卷积层、F6全连接层、输出层,每层都包含可训练参数.输入图像大小为32×32,而MNIST数据集图像的维度为28×28,因此在训练整个网络之前,需要对28×28的图像进行填充,使其维度变为32×32.

图1 Lenet-5网络结构及参数

2 研究工作

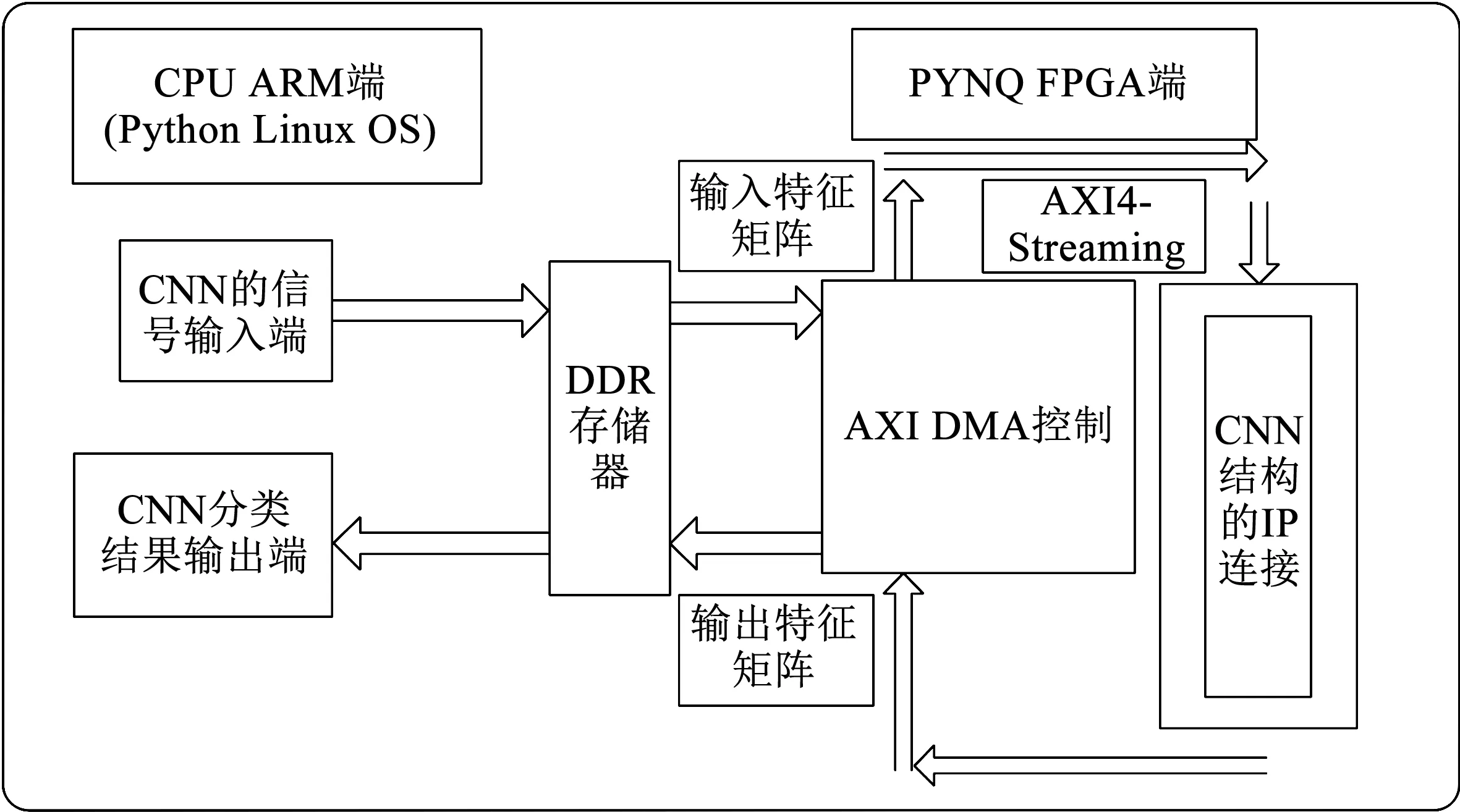

2.1总体框架概览我们采用的设计平台是Xilinx公司研发的PYNQ-Z1开发板,可编程芯片为zynq7020,该芯片上资源较为充足,具有53 200个LUT,4.9MB(280个18kb块)的BRAM和220个DSP(18×25MACC).以及双核ARM Cortex-A9,可实现软硬逻辑协同设计.在该平台上实现的Lenet-5 CNN网络大致可分为两部分:CPU ARM处理器端以及硬件逻辑单元端.具体工作流程大致如下:CPU ARM处理器端的其中一个MCU,被配置为接收输入MNIST数据集的图片张量,并传输至DDR存储器以及输出MNIST数据集的分类结果;DDR存储器,被配置为把输入MNIST数据集的图片张量、输出MNIST数据集的分类结果以及训练好的模型参数存储起来;另一个MCU,被配置为执行DMA驱动程序,控制调度DDR存储器中存储的MNIST数据集图片张量以及将训练好的模型参数传输至FPGA的片上BRAM,并控制输出MNIST数据集的分类结果存储于DDR存储器.在DMA中,通过AXI4-Streaming协议以尽可能大的吞吐量传输数据流,AXI DMA支持每个时钟周期一个数据字的吞吐量.

图2 PYNQ开发板上搭建CNN网络的逻辑框架图

2.2数据量化的必要性以及整体搭建过程一般神经网络的训练是在GPU上进行,使用浮点运算对速度影响不大,但是在FPGA上的离线预测阶段,使用浮点数格式的数据参与运算会严重影响速度.所以要想提高前向传播的运算速度,我们需要对网络模型进行数据量化.进行数据量化的动机主要有两个:1) 减小模型文件的大小,因为模型文件往往占据很大的存储空间;2) 降低预测过程需要的计算资源,从而提高运行速度、减低功耗,这在嵌入式系统设计中具有重要意义.

Plilipp在其研究工作中明确比较了Lenet-5网络在32位浮点数、16位定点数以及8位定点数三种数据格式下的分类精度,在32位浮点数下,Lenet-5对MNIST数据集的分类准确率为99.15%,而在16位定点数的数据格式下准确率几乎没有下降,从32位浮点数到8位定点数在没有进行微调之前相对分类精度损失10.3%,经过微调之后绝对分类精度损失缩小至0.27%,表明Lenet-5在8位定点数的数据表示下运行良好.所以我们最终选择用8位定点数的数据格式来在FPGA上实现Lenet-5.

在软件逻辑端,由于Lenet-5网络对于识别MNIST数据集已经很成熟,所以我们无需重新训练网络,只需要将训练好的网络模型下载好备用.在可编程逻辑端,我们选用了Xilinx公司研发的Vivado HLS2017.4编译器,使用C语言设计算法来编写配置各网络层以备测试,并使用HLS提高抽象级别,这样所有可编程器件都无需手动创建RTL,而且编译器支持ISE和Vivado设计环境,这些特点显著降低了后续设计者的参与门槛[7].

我们将设计好的各层IP核按照网络结构链接在一起即构成了整个Lenet-5网络的IP流图(SDFG),SDF的优点是只要数据流到达节点,节点便会立即开始计算并输出结果,因为SDFG结构中的任意IP核都可独立驱动数据流,这样每层的输出结果会立即流向下一IP核,而不是缓存在片上存储器中,从而节省了整个网络的内存占用.

2.3优化加速措施及细节

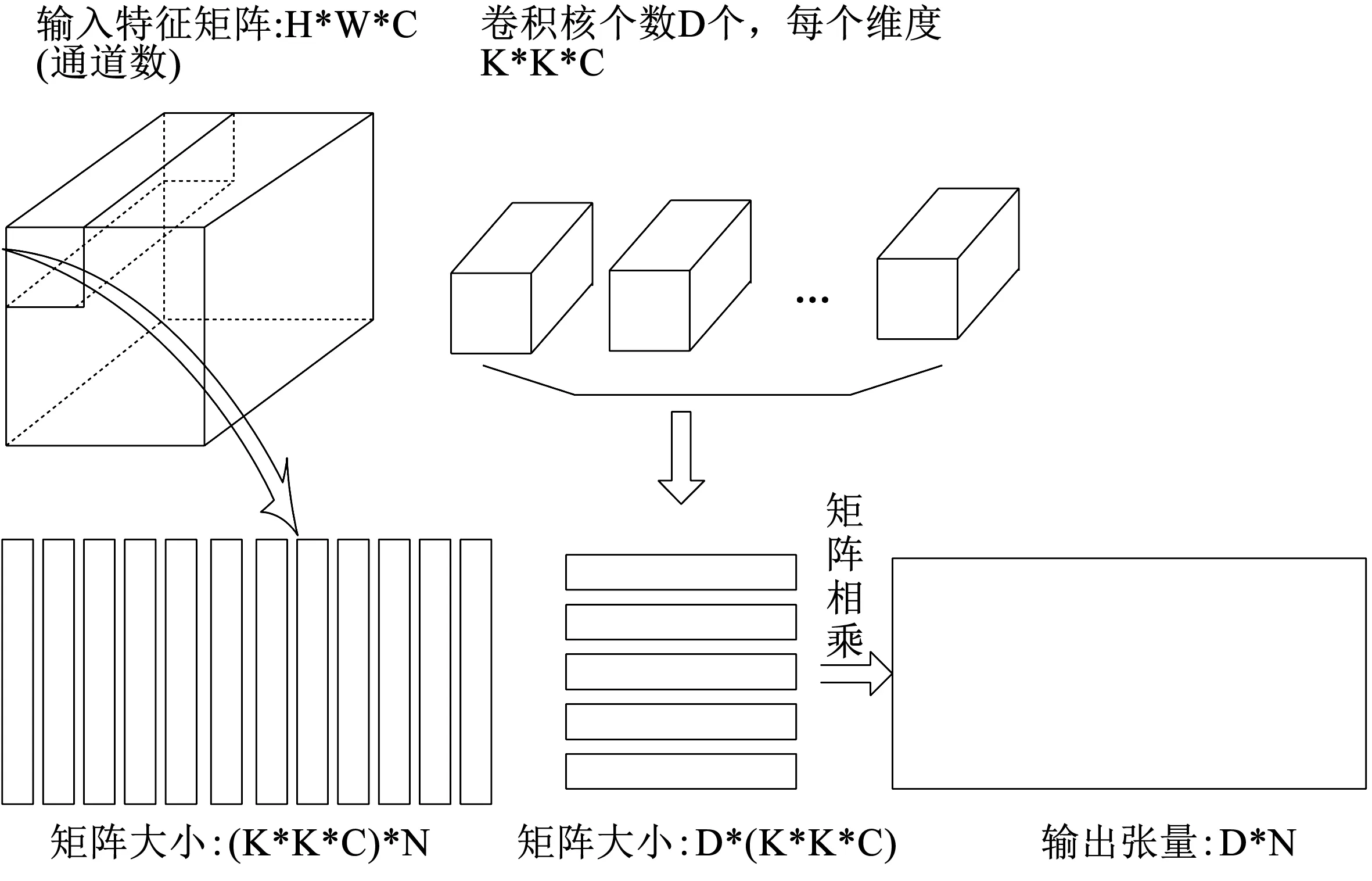

2.3.1 将卷积操作转换为矩阵乘法 首先利用滑动窗口函数根据各层的基础维度、填充维度以及步幅将含有卷积运算该层的输入特征映射扩展为列向量,列向量的顺序与卷积核展开顺序一致;再将扩展的列向量与卷积核进行矩阵乘法完成卷积运算.

图3 卷积过程示意图

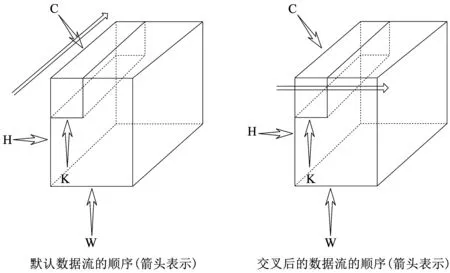

在默认数据流的顺序中,输入特征映射图按照(批量大小,输入通道,高度,宽度)的顺序排列,卷积核按照(输出通道,输入通道,高度,宽度)的顺序排列,在这两种数据流的排列方式中,输入通道都在高度和宽度之前,因此如果我将矩阵拆分为数据流,则在缓冲区缓冲完一个矩阵乘法所有的权重之前,几乎需要缓冲整个特征映射,但是我交叉改变数据流顺序后,让输入通道成为顺序中的最后一个参数,如此所需要的缓冲区数为K*W*C,这大大减少了缓冲区内存的使用,如图4所示.

图4 减小缓冲区内存使用框图

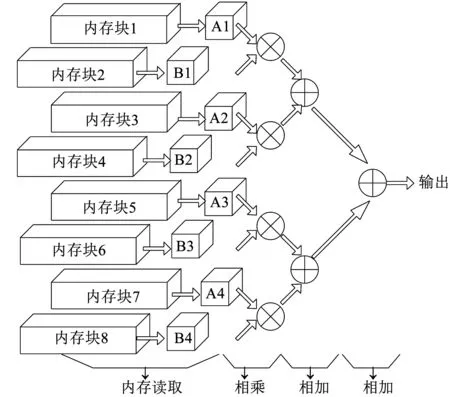

2.3.2 并行计算与流水线技术 要想提高运算的并行性,其中一项有效的技术就是将数据必须存储在多个BRAM中,以便同时获取多个数据;而另一方面并行性的提升带来的是DSP资源的使用量增加,我们通过在程序中设置一个“并行因子”来平衡片上资源和速度,该“并行因子”的具体数值一方面要考虑片上资源的利用率,另一方面要考虑该AI芯片的性能,我们通过不断仿真测试,最终确定了各层“并行因子”的数值.假定矩阵乘法维数为(M*4)*(4*N),在图5中,输入特征图和权重都被分割成很小的存储体以便可以并行获取多个输入数据,我们将输入特征映射存至第1、3、5、7个内存块,将权值存至第2、4、6、8个内存块.在使用乘法器和加法器树进行并行计算阶段,计算过程包含了许多寄存器读取时段,我们设置存储器在接下来的一个时钟周期继续读取数据,而不是等待上一个输出结果,这样就创建了输出流水线,输出数据具有了较高吞吐量,从而整体数据处理速度也得以提高.

图5 FPGA并行计算框图

3 仿真实验结果与分析

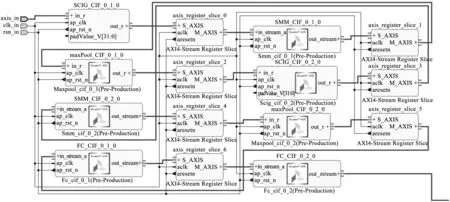

3.1Lenet-5SDFG模型展示图7是Lenet-5网络在Vivado HLS中的仿真模型,对于每个IP层核,在每个时钟周期,IP会接收输入特征映射的新字,并在新输出字准备就绪时候输出.为了消除时间违规,将AXI4-Streaming寄存器片插入到相邻的IP核之间,从而在AXI4-Streaming主机和从机之间创建了定时隔离.

图6 Lenet-5网络SDFG仿真模型图

3.2性能评估与展望在Vivado HLS中,我们首先利用测试平台设计C测试程序来验证Lenet-5网络每一层的输入输出的准确性以及整个Lenet-5网络的输入输出正确性;而在Vivado 中,我们将整个SDFG封装成一个IP核,并进行可行性的验证,通过Vivado 合成比特流并通过Jupyter Notebook下载至PYNQ开发板中,并在Jupyter Notebook部署程序来完成整个项目的测试.在具体程序中,加载预训练好的模型并传递参量,对比了FPGA网络模型在整个运行处理数据过程所用时间与片上ARM CPU网络模型整个运行处理数据过程所用时间,并且将时间损耗与分类准确率可视化出来,便于评估分析.下面我们将从以下几个方面来评估我们的工作以及后续的方向.

3.2.1 片上资源利用率 下表列出了整个网络在FPGA上实现所占用的资源状况.

表1 Lenet-5网络片上资源的占用

从表中我们可以看到,除了片上的寄存器资源与DSP48E外,我们几乎利用了PYNQ上全部的资源,这一方面反映了数据量化的必要性,另一方面反映了如果我们想进一步的获得更好的加速效果,还需要FPGA芯片上更多片上资源的支持.

3.2.2 网络模型的吞吐量 下表展示出了网络模型中的各层参量,其中k代表卷积核的维度,In-channels与Out-channels分别代表输入特征张量通道数与输出特征张量通道数.

表2 FPGA上Lenet-5网络加速优化参数

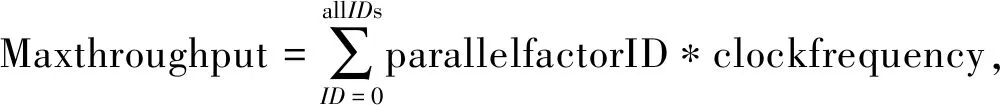

表中列出的并行因子代表每一层最大并行的乘累加操作数(OP/s),因此在理想的情况下(即假设所有层的乘累加操作是同时进行的),我们可以计算得到该CNN模型的理论上的最大吞吐量

(3)

即(25+30+40+20)×100MHz(ZYNQ芯片的时钟频率)=11.5GOP/S.但在前向传播运算中,由于每层的吞吐量都不一样,所以整个网络的实际吞吐量相比于理论吞吐量会有一定的下降.

3.2.3 网络模型的加速比 我们在Jupyter notebook中可视化的时间损耗为整个系统的时间,包括网络部署时间、Python脚本解释器初始化时间、内存传输以及前向传播的时间,在处理批量较小时,前向传播的时间在总体时间中所占百分比不大,其余时间在整个时间中占据主导作用,我们尝试不断增大处理批量,使得前向传播的时间占比增大,在该AI芯片与ARM CPU之间加速比明显的阶段,改变不同的图片处理量,记录执行一次遍历所消耗的时间,结果如下表3所示.

表3 AI芯片与ARM CPU在不同数据处理量下的损耗时间对比

我们可以大致估算一下我们基于FPGA设计的AI芯片的性能,随着batch_size的不断增大,该芯片的加速比会逐渐趋于一个稳定状态,大约在22倍左右.

4 结 语

在本文中,我们结合Vivado以及Vivado HLS等工具在FPGA上实现了一种基于Lenet-5卷积神经网络的AI芯片,具体采用对CNN网络实现8位定点数的数据量来优化片上资源的使用,在分类结果方面相比于32位浮点数数据模型的分类准确率几乎相同,同时相对于ARM CPU有大约22倍的加速.该AI芯片系统携带方便,并且在设计CNN的各层算法时用软件编程替代传统的硬件语言,降低了软件开发人员开发FPGA的门槛,在对网络输入形式为二维图片的分类课题上具有较强的通用性.

但是从长远来看,我们的工作仍然有很大的提升余地,本文所设计的AI芯片系统的性能仍然存在很大的改进空间,芯片上的DSP48E以及Registers的资源利用率不高.在接下来的工作中,我们会优化片上资源的分配来进一步的提高芯片性能,我们会考虑实现结构更加复杂以及针对特定分类主题的CNN网络,而在FPGA开发平台方面,我们将考虑换用更大片上资源的芯片,实现更高的加速.