一种16位200 MS/s的ADC数据采集卡设计

2019-05-27徐智轩葛家瑾

徐智轩,葛家瑾,梁 昊

(1.中国科学技术大学 核探测与核电子学国家重点实验室,安徽 合肥 230026;2.中国科学技术大学 近代物理系,安徽 合肥 230026)

0 引言

随着电子信息技术的高速发展,日趋复杂的信号处理需求对处理平台提出了更高的要求。高速、高精度、高传输速率的数据采集卡广泛成为多场景应用的解决方案[1]。设计提出了一种基于Xilinx公司FPGA的200 Ms/s采样率、16位精度的数据采集系统,采用千兆以太网作为数据传输方案,千兆以太网作为局域网标准的一种重要形式,可提供高速、远距离的数据交互通道,已在局域网实现中得到广泛的应用[2]。通过千兆以太网,设计实现了FPGA与上位机协同完成数据采集与性能测试。

1 数据采集卡设计方案

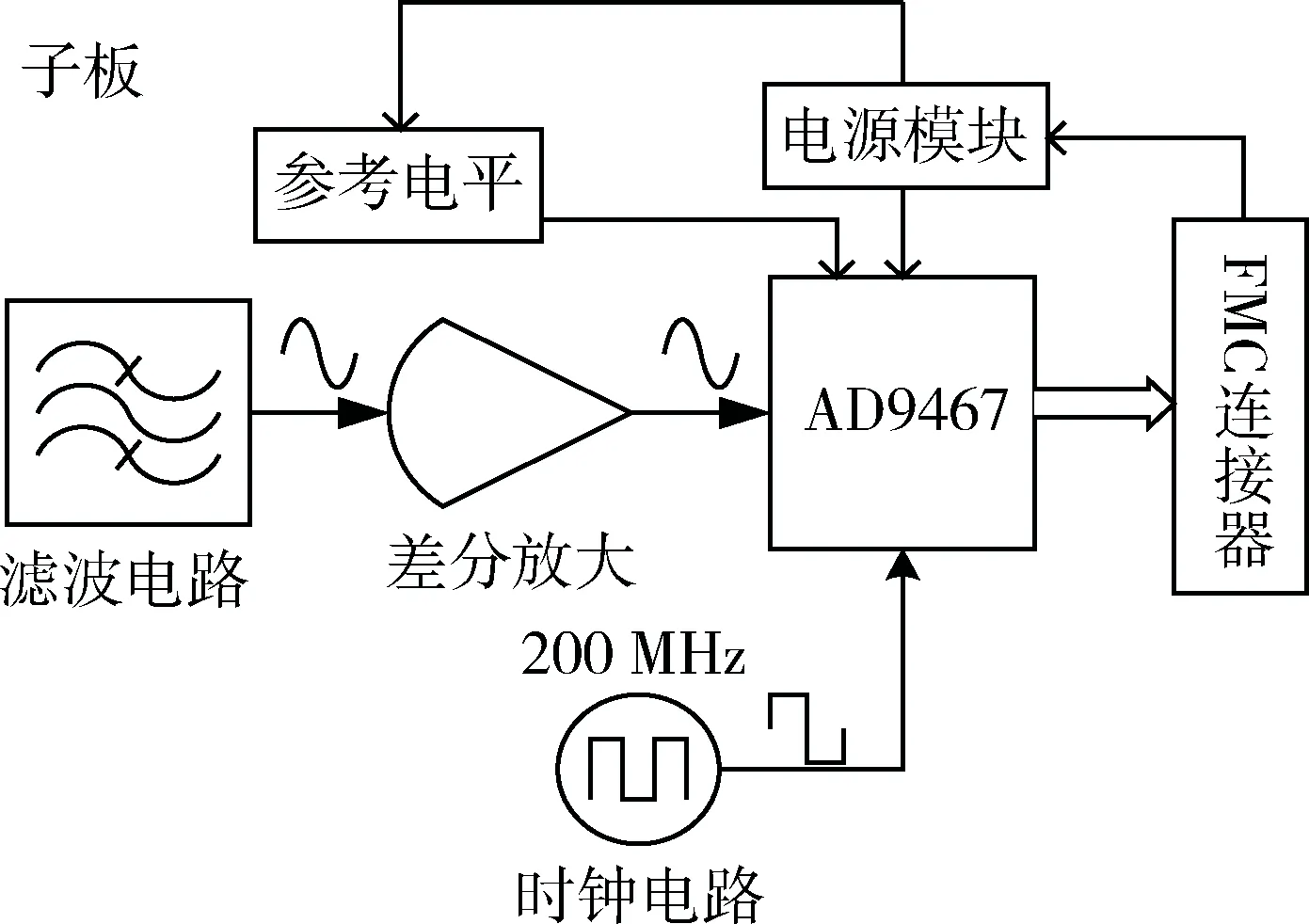

数据采集卡的设计主要包括两部分,作为模拟数据采集的子板部分和作为数据传输和存储的母板部分,两板用FPGA Mezzanine Card(FMC)连接器相连。母板上有一块型号为XILINX Vertex-6的FPGA和一块作为存储器件的DDR3内存条及用于数据传输的千兆以太网接口。模拟输入信号会先通过子板的滤波和放大电路进入ADC,ADC对模拟信号进行模数转换后,产生的数字信号通过FMC进入母板的FPGA。数据会先进入DDR3进行缓存,缓存的数据通过千兆以太网口上传到PC端。数据的收发可通过上位机进行控制。系统的整体结构如图1所示。

图1 系统设计框图

2 子板设计方案

子板是数据采集板进行模拟信号处理的部分,主要包括带通滤波器、差分放大电路、时钟电路、电源电路。子板电路结构如图2所示。子板采用AD9467作为模数转换芯片,AD9467是一块输入缓冲流水线ADC,由四级闪存组成,输入缓冲器提供线性高输入阻抗以减少高频输入信号的反冲,ADC对高线性度、低噪声和低功耗等指标进行了优化,来自每一级闪存的量化输出被组合成16位结果,通过冗余位数字校准闪存错误[3]。

图2 子板电路框图

2.1 模拟信号输入处理

模拟信号输入需通过滤波和放大处理,滤波采

用高Q值的带通滤波器,带通滤波器可实现有效的选频与滤波功能,在目标输入频率范围内改善输入波形的质量。

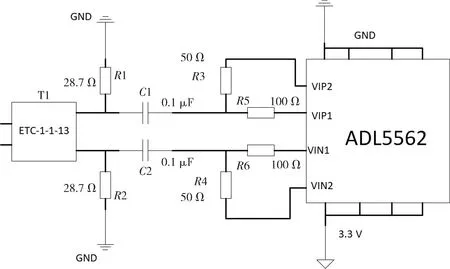

使用ADL5562芯片来差分驱动ADC的输入,驱动芯片的输入阻抗进行了匹配,使得共模噪声得到抑制。在静态工作时,放大器电流的典型值是80 mA,芯片未使能时电流小于3 mA,为信号的输入和输出提供了有效的隔离。差分驱动放大电路如图3所示。

ADL5562是一款高性能全差分放大器,且对射频信号和中频信号处理进行了优化。放大器在宽频域范围内有着低电平噪声和低失真性能,是高速高性能ADC的理想驱动器。差分放大电路的设计提供了三种增益级别:6 dB、12 dB和15.5 dB,可通过调整电路中和引脚相接的电阻的阻值进行配置。

2.2 时钟模块

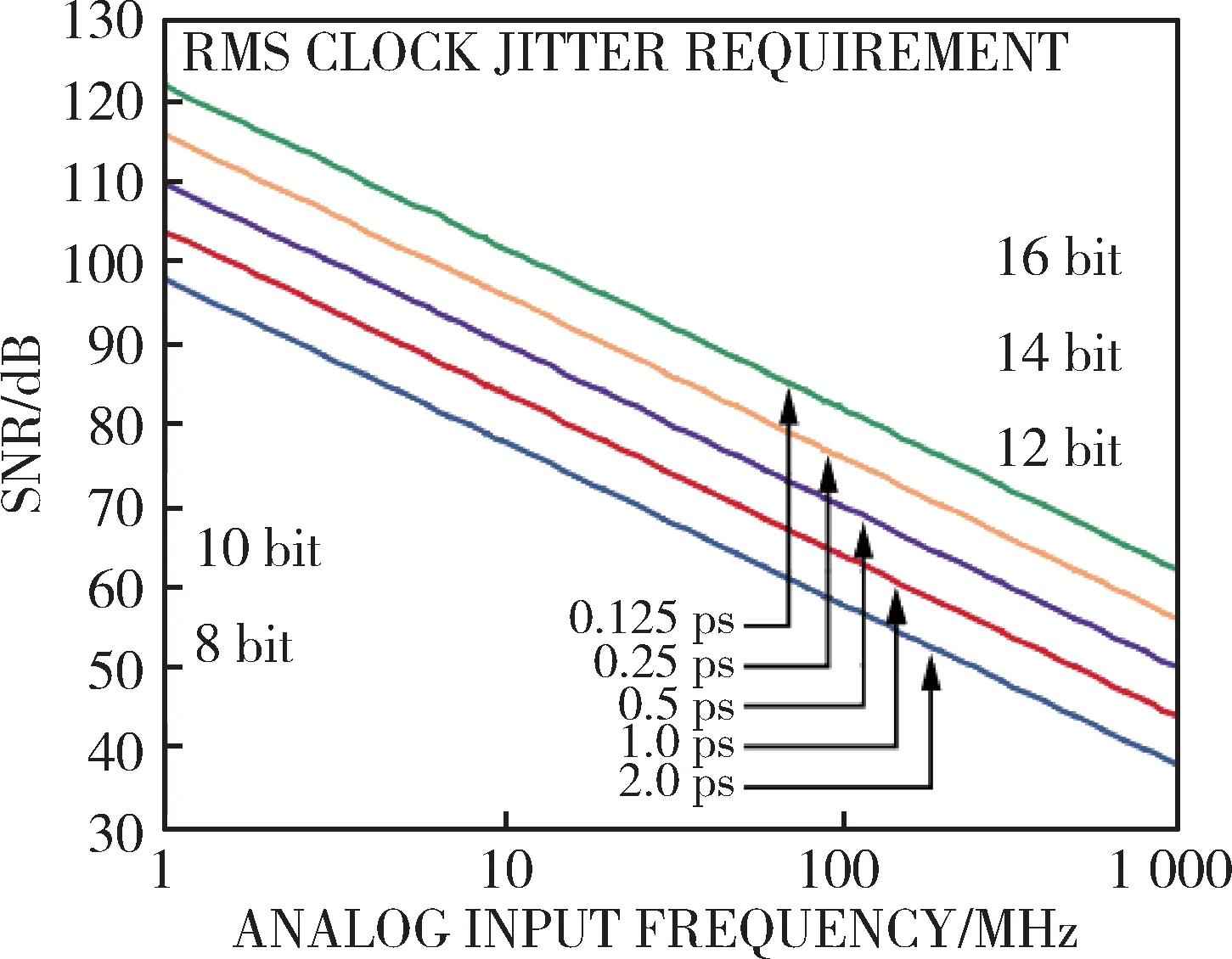

用低相位噪声振荡器来产生ADC的时钟是必要的,因为采样时钟的抖动会调制模拟输入输出信号,降低信噪比,时钟抖动和信噪比的关系如下:

SNR=-20lg (2×π×fa×tj)

(1)

式中,孔径抖动的均方根表示着所有抖动源的代数平方,包括时钟输入、模拟信号的输入和ADC的内部孔径抖动。内部孔径抖动与采样时钟上的抖动相比可以忽略,因为抖动对内部中频欠采样影响较大,当抖动成为影响ADC动态性能的主要因素时,时钟的输入应当被看作是模拟信号的输入[4]。为使ADC能工作在理想状态,设计以低抖动的有源晶振SI545作为时钟源。SI545采用数字phase-locked-loop(PLL)架构,在工作频率下提供了超低的抖动和低相位噪声,其抖动均方根的典型值为80 fs。

图3 差分驱动放大电路

图4表示的是ADC的信噪比和抖动的关系,一般高速ADC会同时使用两个时钟边沿来产生内部的定时信号,因此高速ADC对时钟信号的占空比敏感,占空比容错率需保持在5%以内。AD9467内置一个占空比稳定器来重新排列非采样单元,为内部时钟提供占空比为50%的信号,使得外部输入时钟的占空比失真的容错范围增加,提高了时钟模块的设计稳定性。

图4 时钟抖动与有效位关系

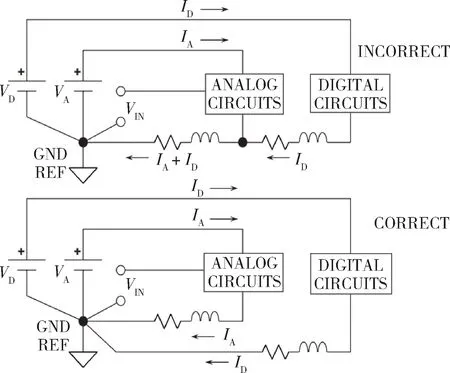

2.3 子板接地处理

子板电路设计属于模数混合电路,恰当的接地设计可以改善采集板的性能。图5为数字返回电流干扰模拟返回电流的典型情况,接地回路电感和电阻由模拟电路和数字电路共享。因为ADC的数字信号输出带有大量的谐波,会干扰到模拟型号的波形,同理模拟输入的高频分量也会干扰到数字信号的输出。这里将子板的模拟地和数字地分开,中间以磁珠相隔。磁珠可用来隔离高频信号,减少数字信号对模拟信号的干扰。

图5 流入模拟返回路径的数字电流产生误差电压[5]

3 母板设计方案

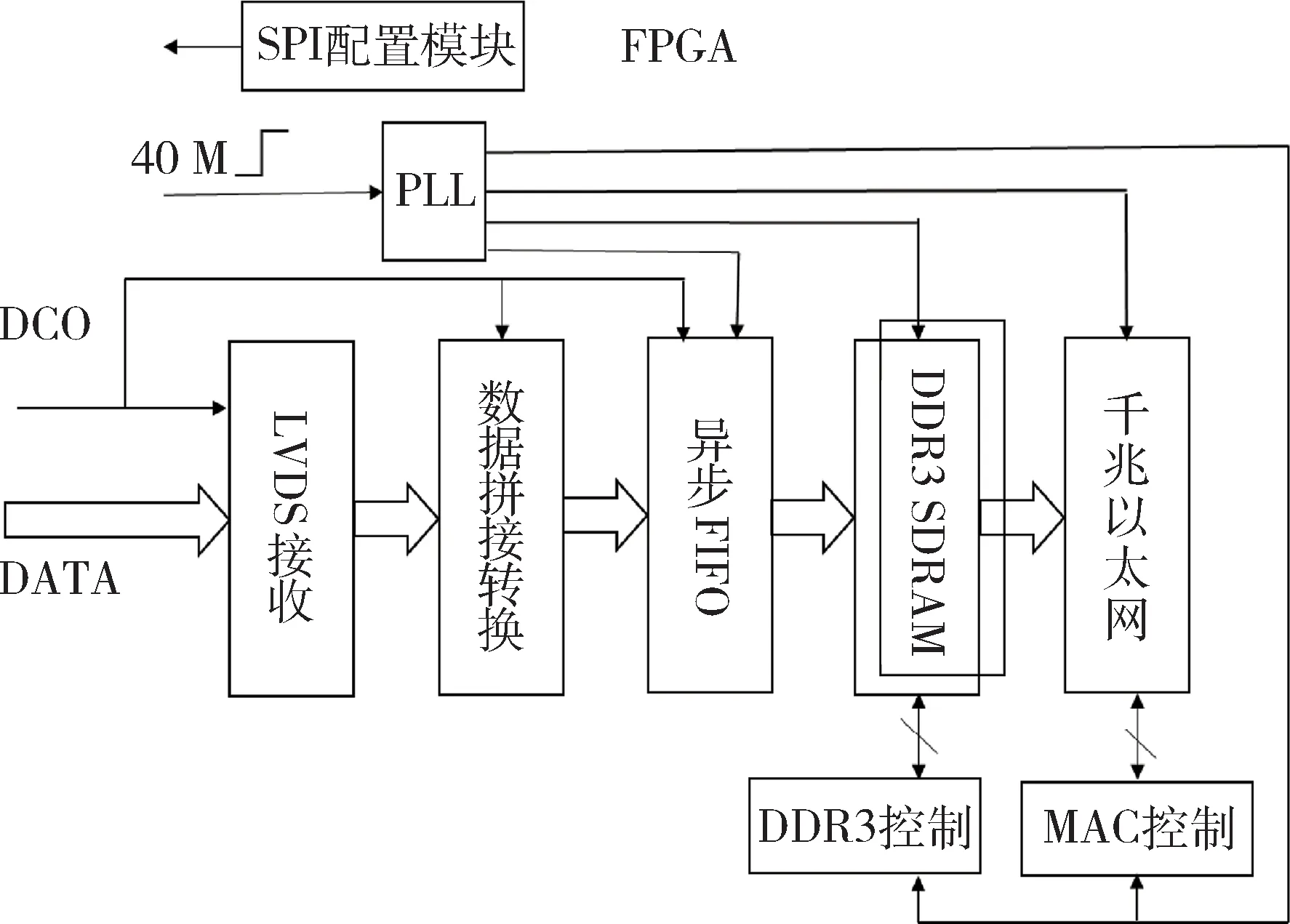

母板是采集卡作为数据传输和存储的部分。FPGA作为母板的控制单元,DDR3用作存储单元,千兆以太网口作为传输接口。FPGA的内部逻辑结构如图6所示,包括Low-Voltage Differential Signaling(LVDS)数据接收模块、数据拼接转换模块、SPI配置模块、DDR3读写控制模块、以太网传输控制模块。

图6 母板逻辑结构框图

DDR3控制逻辑由Xilinx公司提供的IP核和用户接口模块组成,IP核负责与DDR3内存条直接通信,完成DDR3内存条的初始化,对内存条进行刷新和预充电操作,并将DDR3内存条复杂的读写时序翻译为用户可理解的读写时序。用户只需根据IP核提供的状态信号进行读写操作即可。DDR3控制逻辑结构如图7所示,该模块根据上位机的指令,与读写FIFO、DDR3 IP核配合,进行存取操作[6]。在DDR3前一级FIFO中准备一定数量现成的数据,一组数据连续写入IP核,同时对应的相同数量的命令也被连续写入IP核直到DDR3被写满,数据和命令的写入过程相互独立[7]。

图7 DDR3内存条控制逻辑

4 采集板性能测试

采集板的性能测试主要分三部分:DDR3存储性能测试、以太网传输性能的测试和ADC性能测试。

4.1 DDR3性能测试

DDR3性能测试的方法是将准备好的数据存入内存条中,通过以太网接口将数据上传到计算机,数据依据地址被连续地写入内存条中,再从内存条中依次按照地址从内存条中读出[8],通过FPGA中的计数器进行计数。在测试环节中,为了使得内存条达到最大存储速率,应使DDR3在满负荷条件下工作,因为SDRAM在存取过程中会对存储单元进行充电、刷新产生额外的时间。同时需要设置FPGA内部的计时器,以DDR3开始存储的标志位为计时起点,以DDR3存满标志信号作为计时终点,DDR3内存条的容量为2 GB,测试存满内存条所需时间为278 054 μs,由此计算出最大写速率的理论值为68.3 Gb/s。

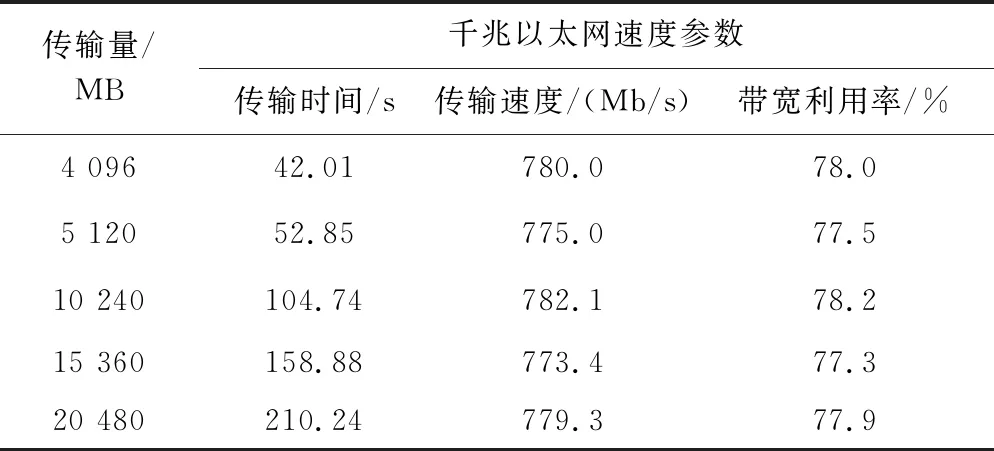

4.2 以太网传输测试

以太网的传输测试主要分为传输稳定性的测试和数据传输速度的测试。以太网的传输测试原理和DDR3测试原理相似,数据源是FPGA内部设置的一个计数器,数据通过以太网传输后进行奇偶校验,再进行连续性检测,若未发现错误,则证明经过以太网传输的数据准确[9]。

以太网速度测试的方法是根据上位机起始上传数据时开始计时,数据传输成功后终止计时。速度测试的硬件环境有型号为Intel core(TM)i5-4590的CPU、Intel 545S 128G SATA3接口的固态硬盘、型号为Intel PWLA8391GT的千兆以太网卡、千兆以太网线。测试了不同传输数据量下千兆以太网的速度,结果如表1所示,以太网最大传输速率达到了782 Mb/s。

表1 千兆以太网速度测试表

4.3 ADC静态性能测试

ADC静态性能测试采用码密度直方图测试[10]。测试依据码密度直方图原理编写MATLAB程序,将数据导入程序得到静态性能测试结果,测试结果如图8和图9所示,测得ADC的DNL(微分非线性)参数为0.51/-0.43 LSB,INL(积分非线性)参数为3.92/-3.56 LSB,对比AD9467的器件手册,在未失码的情况下ADC的INL的范围是±9.5 LSB,测试结果在手册范围内。

图8 采集卡微分非线性

图9 采集卡积分非线性

4.4 ADC动态性能测试

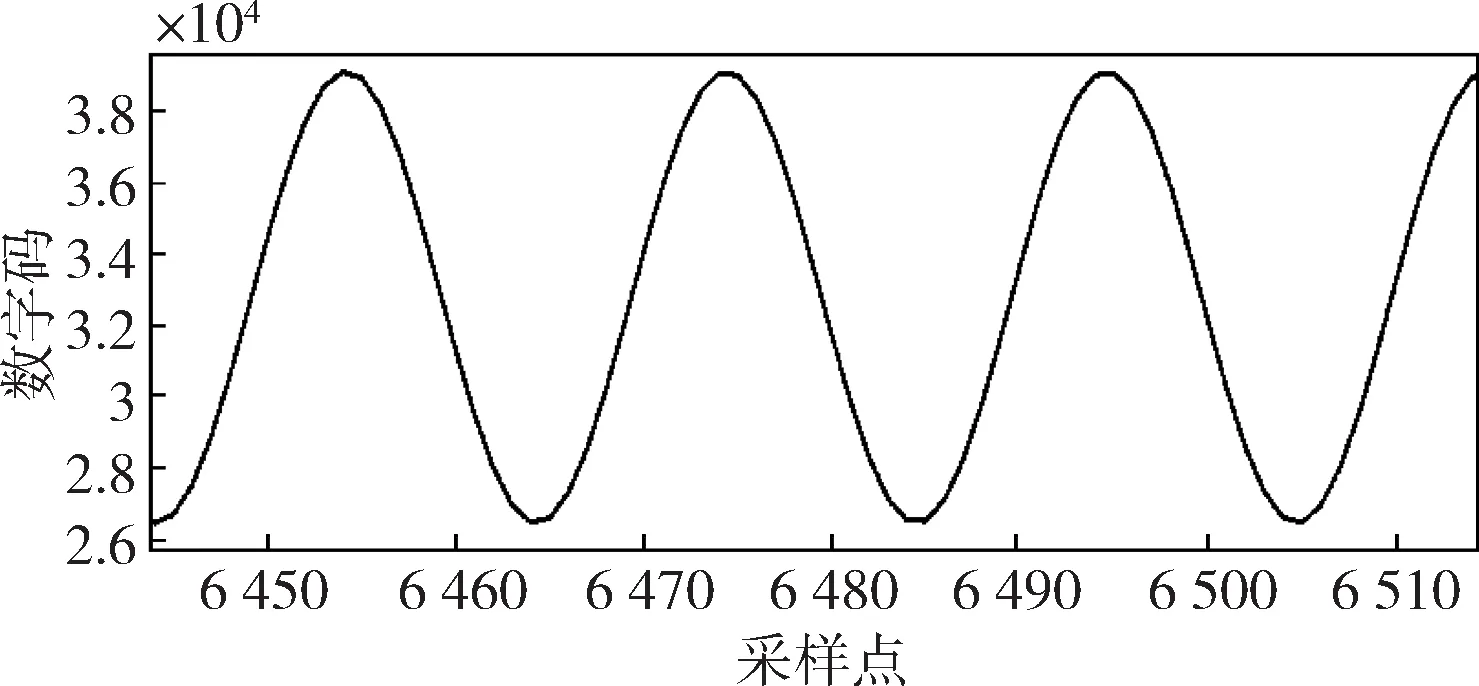

FFT测试方法是目前最常用的ADC动态性能的测试方法,它是从频域的角度去分析信号及噪声背景的频谱参数,以此来计算ADC的各项动态性能指标[11]。一般用于定量表示ADC的动态性能的常用指标有6个,分别是SINAD、ENOB、THD、THD+N、SFDR等,这里选取了其中三个参数进行了测试,输入频率选取从1 MHz~50 MHz范围内的四个值进行采样,测量结果如表2所示。信号恢复波形如图10所示,频谱图如图11所示。

图10 MATLAB恢复数据波形(9.9 MHz)

图11 采集到的9.9 MHz正弦波信号频谱图

频率/MHz主要动态参数参考值SNRSFDRENOBENOB181.6183.4112.4912.49.9102.481.1912.4312.224.8103.3982.5312.5412.449.3101.5784.6512.6512.0

5 结论

设计了一种16位200 Ms/s的ADC数据采集卡。经测试和分析后,ADC数据采集卡的有效位在12.5左右,和器件手册上的典型值相符。采集卡的数据传输性能稳定,可以在上位机的控制下有效地收发数据。DDR3的最大传输速率可达到68.3 Gb/s,千兆以太网传输速率可达到782 Mb/s,数据采集卡的内存有2 GB,所以采集卡的存储深度有1 024M个采样点,可连续采样5 s左右。