晶振电路负载参数匹配与测试

2019-05-10孟永刚陈浩王军

孟永刚,陈浩,王军

(联创汽车电子有限公司,上海 201206)

0 引言

晶体振荡器俗称晶振,是晶振电路的核心元器件。晶振电路用于产生时间频率基准,为微控制器系统(Microcontroller Unit,MCU)提供精准的时基。在实际应用中,如果晶振电路负载参数匹配不当,一方面,可能会造成晶振电路工作频率出现偏差,进而造成计时不准,通信不能同步;另一方面,在睡眠唤醒时,电路扰动较小,可能会导致晶振电路起振困难。无论哪种情况,均会影响微控制器系统的性能甚至造成其无法工作。因此,合理匹配晶振电路负载参数具有十分重要的意义和实际应用价值[1-5]。

1 晶振电路原理

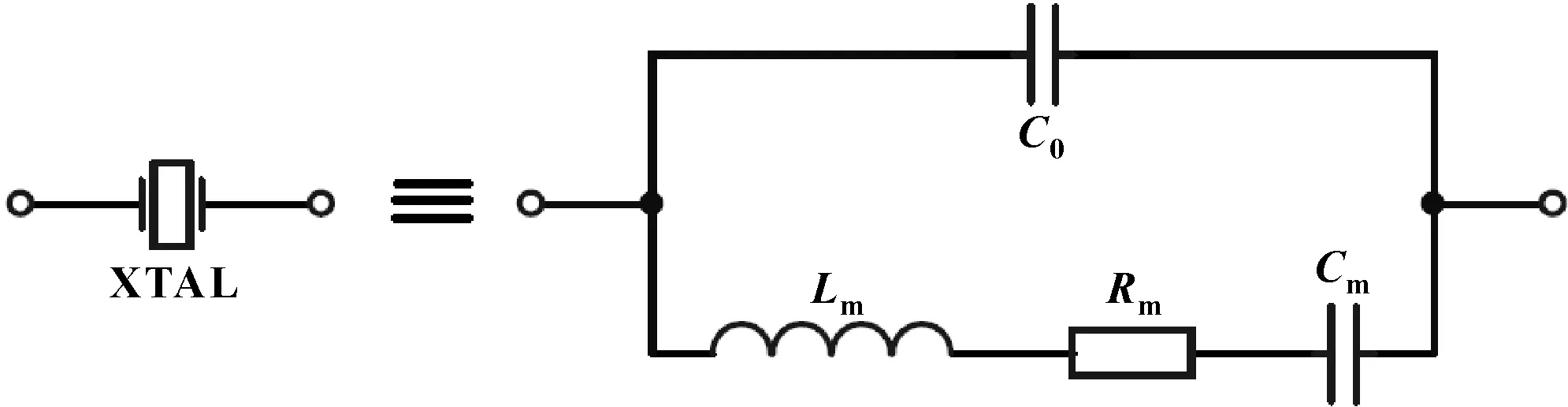

作为晶振电路的核心元器件,晶体振荡器是一种能实现电能和机械能相互转化的压电器件,其等效电路如图1所示,XTAL为晶体振荡器;C0为等效并联电容,其值与晶振的外形、尺寸有关;Lm为动态等效电感,代表晶振振动的惯性;Cm为动态等效电容,代表晶振的弹性;Rm为动态等效电阻,代表对电路的损耗。

图1 晶体振荡器等效电路

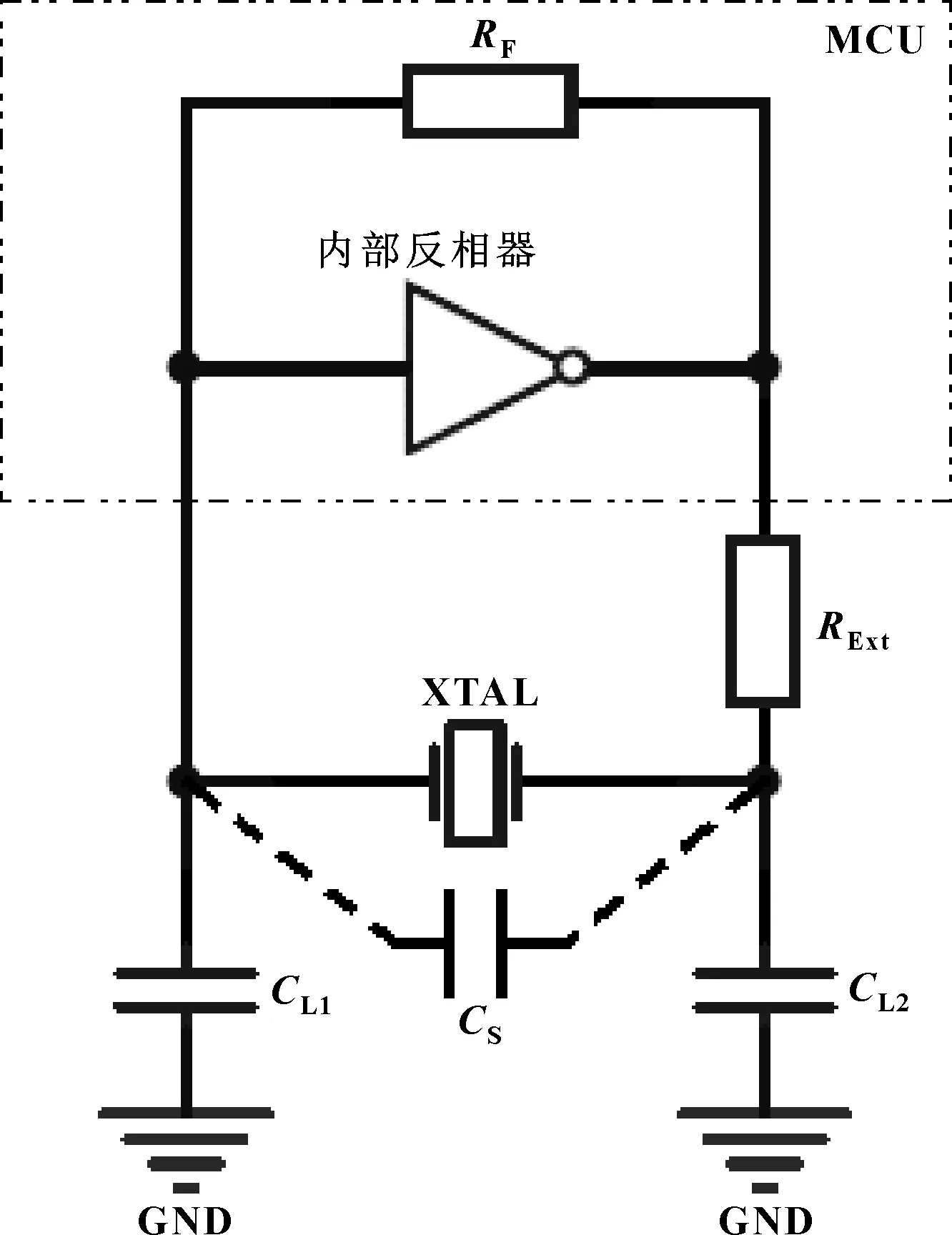

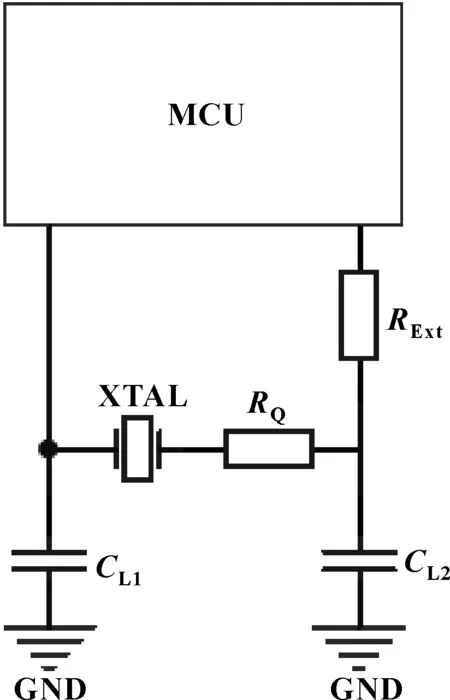

晶振电路主要由一个放大器和选频网络组成,选频网络决定振荡频率。晶振电路在电能的作用下,放大了晶振工作频率范围内的扰动,从而造成起振。由于Pierce振荡电路具有功耗低、成本低和稳定性高等优点,因此目前微控制器系统中使用的晶振电路多为Pierce振荡电路[6]。Pierce振荡电路原理图如图2所示。

图2中,内部反相器的作用等同于放大器;RF为反馈电阻;RExt为限流电阻;CL1和CL2为外接负载电容;CS为等效杂散电容,CS是由芯片引脚、焊盘、封装引脚和印刷电路板走线等引起的寄生电容。

图2 Pierce振荡电路原理图

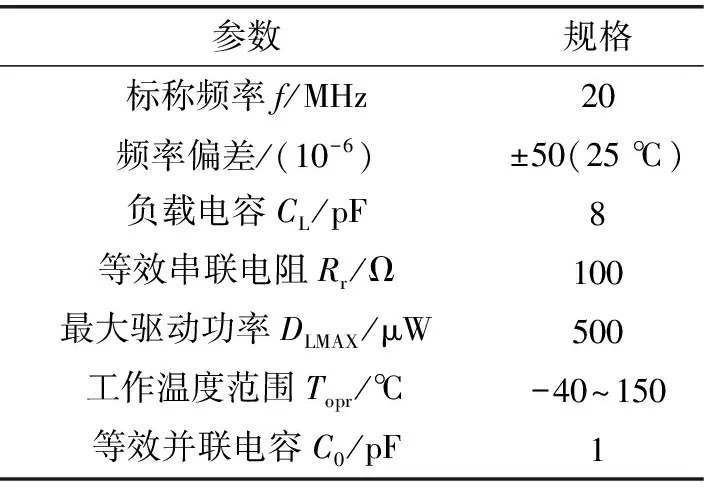

2 晶振电路参数匹配

为了便于分析和说明,本文作者以某公司的一款电动助力转向控制器(Electric Power Steering,EPS)中使用的Infineon SAK-TC264D-40F200W BB型号微控制单元所匹配的晶振电路为例进行晶振电路负载参数匹配介绍。选用的晶振型号为NX5032GA,其基本参数规格如表1所示。

表1 晶振规格参数表

2.1 负载电容的计算与测试匹配

2.1.1 理论计算方法

负载电容CL的大小取决于外部电容CL1、CL2和等效杂散电容CS,计算公式如下:

(1)

晶振厂家在datasheet中通常会给出负载电容CL的标称值。等效杂散电容CS与芯片引脚、焊盘、封装引脚和印刷电路板走线等均有关系,无法得到具体理论数值,按照经验,通常估算为3~5 pF[7]。一般两个外部电容CL1和CL2选定为相同电容值。文中选定的晶振负载电容CL为8 pF,代入公式(1)可计算得到CL1=CL2=6~10 pF。

经过理论计算得到的外部电容CL1和CL2的范围值可以作为后续测试匹配的参考,然后通过实际测试匹配实验确定最优外部电容容值。

2.1.2 测试匹配方法

晶振的具体测试匹配方法是根据理论计算所得电容值范围附近选取典型电容值的电容,然后分别测试并记录不同外部电容值下的振荡频率、振荡频偏等参数,通过对比各参数选取最优外部电容值。

最优外部电容值评价准则:实测振荡频率越接近标称振荡频率,振荡频偏越小,则电容值越优,实际测试匹配过程需要权衡选择电容值。

2.1.3 测试匹配过程

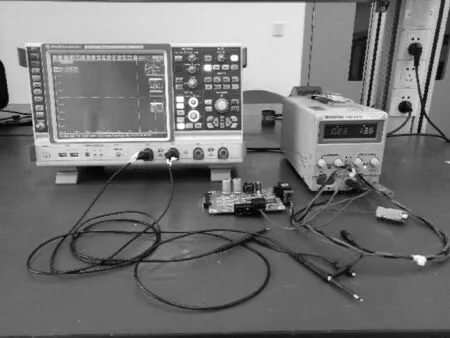

晶振电路测试匹配的环境设置如图3所示。此处测试的目的仅仅是为了进行不同负载参数下晶振特性的比对,验证理论推算的正确性,因此文中选用示波器作为基本测量设备,如果需要获取精度更高的频率数据,需要选用专业的显频仪等设备进行测量。该实验中选取6.8、8、10和100 pF 4种容值电容作为外部CL1和CL2的备选电容,限流电阻固定为1.5 kΩ,选择100 pF电容是为了更明显地验证当外部电容值和理论计算值差别较大时的晶振输出波形的表现状况。通过更换不同容值的外部电容,并利用示波器采集晶振电路输出波形(CL1和CL2需同时更换,保证CL1和CL2的容值始终一致)。对比输出波形的稳定性、频率偏差和幅值大小来判断最佳容值。为了增加数据的可靠性,实验中对每种工况波形随机截取10次,利用10组随机截取的实际波形频率,以方差的方式计算每种工况的平均频偏σ,平均频偏σ定义如下:

(2)

式中:f0为晶振标称工作频率,文中为20 MHz,f1、f2、......、f10为10组随机截取的晶振实际工作频率。

图3 晶振电路测试匹配环境设置

2.1.4 测试结果及分析

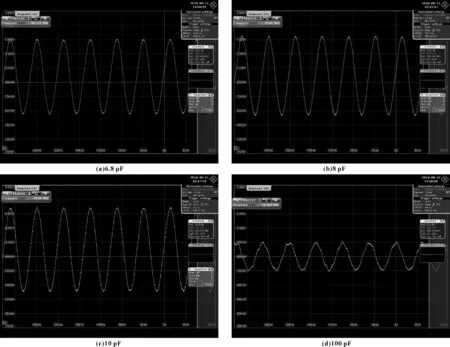

图4给出了当外部电容为6.8、8、10及100 pF时,晶振电路的输出波形。从图中可以看出,在前3种外部电容配置下,晶振电路的输出波形均较为平滑,未出现突变区域,波形重复度较高。当外部电容提升至100 pF时,可以看出,晶振电路输出波形呈现出明显不平滑现象,波形不规律区域较多。

图4 不同外部电容下晶振电路输出波形

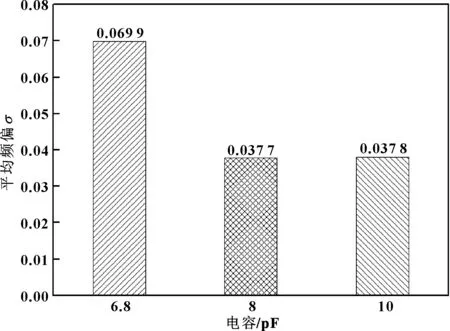

不同外部电容下晶振电路输出波形的平均频偏如图5所示。

图5 不同外部电容下晶振电路输出波形的平均频偏

图5为当外部电容为6.8、8和10 pF时,晶振电路输出波形的平均频偏对比。可以看出,当外部电容为8和10 pF时,平均频偏较低,且二者之间差别不大,当外部电容为6.8 pF时,平均频偏明显升高。说明8和10 pF是较为合适的容值。

2.2 限流电阻的计算与测试匹配

2.2.1 理论计算方法

外部限流电阻RExt的主要作用是限制反相器电流输出的大小,控制晶振驱动功率,防止晶振驱动功率超过最大驱动功率限值而造成过驱动,进而导致晶振因为过度的机械振动而出现电极劣化、频偏、寿命衰减等问题。外部限流电阻RExt的阻值通常是在确定了外部电容CL1、CL2的容值之后确定的。从晶振电路图(图2)中可以看出,限流电阻RExt和外部电容CL2构成分压电路,在估算限流电阻RExt的电阻值时,通常是令RExt的电阻值和CL2的容抗值相等[8],因此,RExt的估算公式如下:

(3)

当振荡器频率f0=20 MHz,CL2=10 pF,计算可得RExt为796 Ω。这个值仅仅是通过理论估算得到的,实际应用中并不一定能直接使用。因为实际应用晶振电路中,RExt需要做调整以调节流经晶振的电流大小,确保实际电路中的晶振驱动功率满足厂家提供的指标要求。同时,RExt值也会影响晶振频率偏差,频率偏差过大也是不允许的。因此,必须通过实测的方法,改变RExt值,对比权衡参数指标的变化,进而确定最佳的限流电阻值。

2.2.2 测试匹配及结果分析

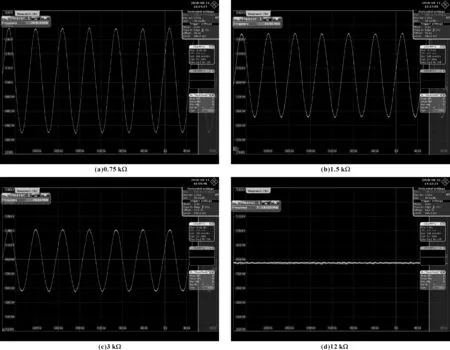

外部限流电阻的测试方法和过程与外部电容的测试基本一致,这里不再赘述。此处,选择0.75、1.5、3和12 kΩ 4种电阻,外部电容固定为10 pF。不同电阻值匹配下的晶振电路输出波形如图6所示,对于前3种限流电阻,晶振电路输出波形整体较为平滑,波形重复度较高,随着阻值增加,波形幅值减小。而当限流电阻增加至12 kΩ时,晶振已无法正常起振。

图6 不同限流电阻下晶振电路输出波形

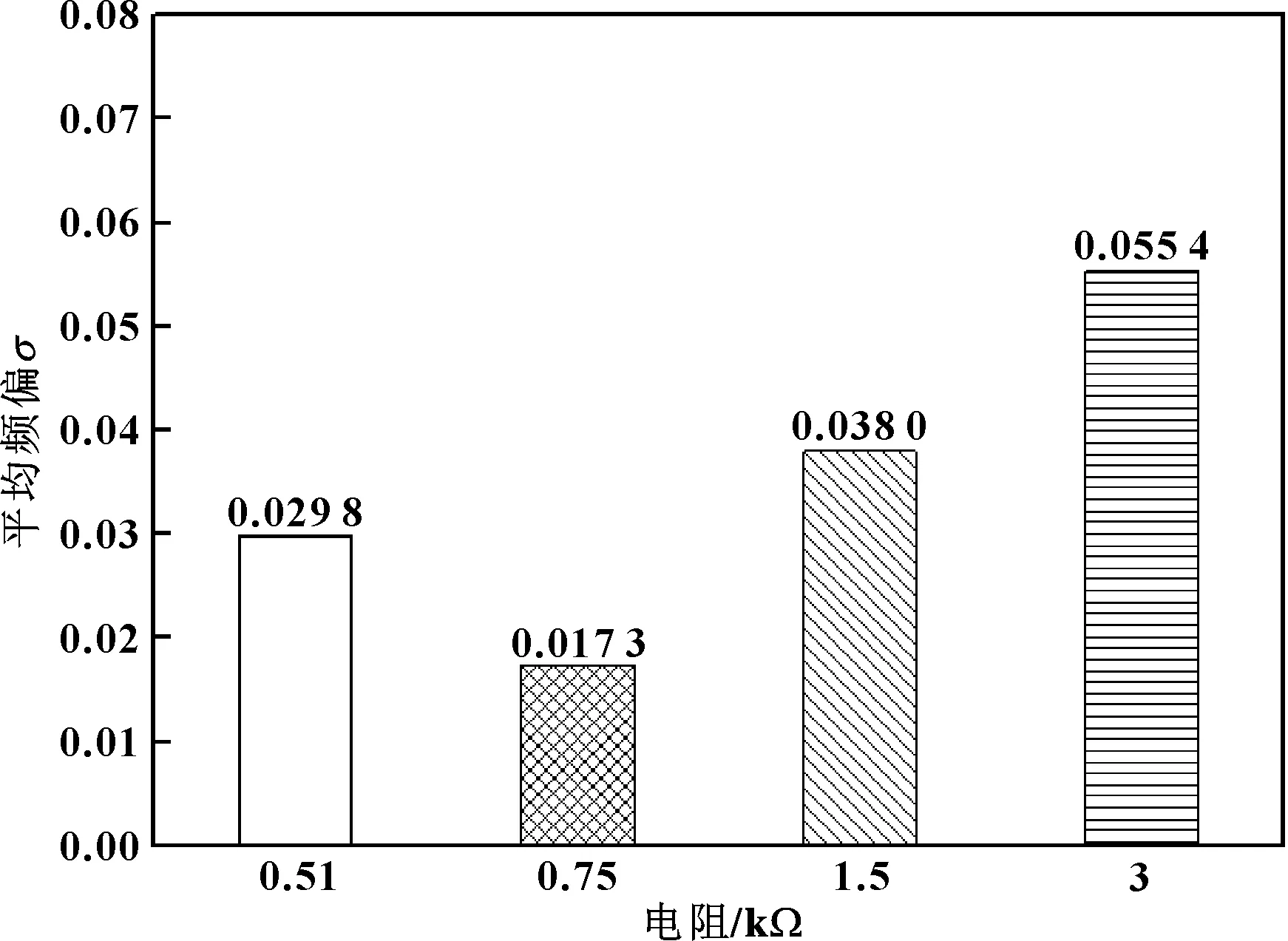

图7给出了当限流电阻为0.51、0.75、1.5和3 kΩ时,晶振电路输出波形的平均频偏对比。通过对比可以看出,当限流电阻为0.75 kΩ,即接近理论计算值0.796 kΩ时,平均频偏最小,随着电阻与理论计算值偏离的增加,平均频偏逐渐增加。通过对比测试结果可以看到,在此实验中所选的几组电阻中,0.75 kΩ在满足晶振驱动功率的前提下是最佳选择。

2.3 负性阻抗的测试和计算

负性阻抗-R也称为发振余裕度,用于评价晶振在发振回路上的发振能力。发振余裕度不足时,会导致振荡电路振荡不稳定甚至启动失效等问题。负性阻抗-R需满足-R>(5~10)Rr[7],晶振电路才能稳定发振。晶振电路负性阻抗-R的测试电路原理图如图8所示。

图7 不同限流电阻下晶振电路输出波形的平均频偏

图8 负性阻抗测试原理图

图8中RQ为可调电阻。具体测试方法:通过不断增大RQ阻值,直到晶振停止振荡,记录此时的RQ阻值,根据测得的RQ值,可按如下公式计算负性阻抗:

-R=RQ+RL

(4)

(5)

式中:RL为加载后的谐振电阻;Rr为等效串联电阻。文中设计的晶振电路经过测量计算得到的负性阻抗-R为1 330 Ω,-R>10Rr=10×100 Ω=1 000 Ω,因此,该晶振电路满足晶振起振和稳定工作条件。

2.4 驱动功率的测试与计算

晶振驱动功率DL不能超过晶振制造商给出的最大驱动功率DLMAX,否则晶振会因为过度地机械振动而出现电极劣化、频偏、寿命衰减等问题。驱动功率DL计算公式如下:

(6)

式中:IQ是流过晶振电流的均方根有效值,电流有效值IQ的计算公式为

(7)

式中:IPP为正弦波电流峰-峰值。综上所述,驱动功率DL的计算公式:

(8)

经过测试计算,文中晶振电路的晶振驱动功率DL为90 μW,而DLMAX为500 μW,DL 结合一款应用于电动助力转向系统中的微控制器单元所匹配的晶振电路,对晶振电路负载参数的理论计算、测试和匹配方法进行了介绍。可以看出,通过测量匹配的负载参数与理论计算匹配得到的晶振电路负载参数基本吻合。在实际应用中,不同的MCU、不同的PCB布线方式、不同的环境条件均会对晶振电路负载参数产生影响。因此,在设计晶振电路和进行晶振电路负载参数匹配时,需以理论计算方法为参考,结合测试手段,权衡匹配出最适合当前控制器电路环境的负载参数,使设计的晶振电路工作在最佳状态。3 结束语