一种零值测试基带信号源设计

2019-05-08

(中国飞行试验研究院,西安 710089)

0 引言

目前全球卫星导航系统正处于快速发展时期[1-4],北斗是我国自主研发并独立运行的全球卫星导航系统,在导航系统设计过程中,基带信号源可在试验条件下对导航系统性能进行有效测试和评估,基带信号处理的调试工作显得尤其重要[5-7]。

国外在导航信号源领域起步较早,形成了技术成熟且应用广泛的信号源。受技术封锁等原因,国内使用的导航信号源多为国外产品,价格昂贵且基带信号模式单一,通用性差[8-11]。国内该领域的研究主要集中在部分高校、科研院所等机构,研究重点是软件信号源及采集回放信号源,相应产品的实时性和灵活性差[12-14]。

本文设计了一种硬件架构零值测试基带信号源,结合上位机软件,信号源可模拟并输出多制式多路调制基带信号,可以完成4通道射频信号的采集,也可以完成4通道直接射频信号的产生,可灵活配置工作参数及设备工作状态的实时监测,便于导航系统的零值自测。该信号源设计依托实际需求,解决了导航系统研制过程中基带信号调试的难题。

1 系统组成及功能概述

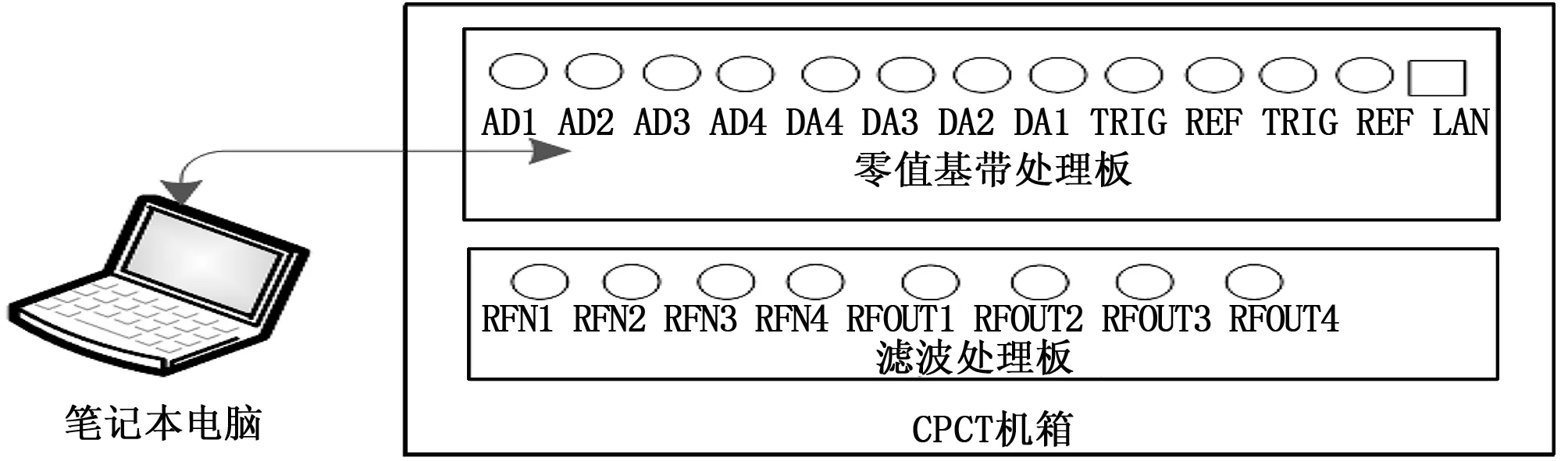

零值测试基带信号源一方面模拟并输出6~10路QPSK、BOC、TMBOC、TDDM-BOC、AltBOC、TD-AltBOC、TD-BPSK(5)调制的基带信号,与频率综合器产生的信号进行混频,模拟下行B1、B2、B3的信号以便系统进行零值自测;另一方面,能够直接生成并输出L波段射频信号,能够对L波段射频信号进行直接采样。信号源可完成发射和接收两个链路功能的处理,零值基带信号处理板采用标准CPCI式板卡设计,可完成4通道射频信号的采集,也可完成4通道直接射频信号的产生,板卡支持内时钟和外时钟两种工作模式。通过网口与上位机进行通信,从而实现上位机对零值基带信号处理板的配置和控制。零值测试基带信号源系统组成原理如图1所示。

图1 信号源系统示意图

在CPCI机箱中还集成一个滤波处理板,板上主要集成了B1/B2/B3频点的无源LC滤波器,用来对零值基带信号处理板输出的4路射频信号进行滤波。通过上位机软件完成设备的工作参数配置、设备状态监测、数据显示记录等处理。

2 系统设计

2.1 零值基带信号处理板设计

零值基带信号处理板的发射链路主要功能是完成B1/B2/B3频点导航信号的基带调制处理,并通过DAC完成直接数字射频信号的产生和输出;接收链路的主要功能是完成B1/B2/B3/BS4个频点导航信号的射频信号采样、捕获、跟踪、解调、测距处理,并最终将不同频点的每个分量的测距结果实时上传上位机软件,完成对发射板产生的导航信号零值标定和评估处理。

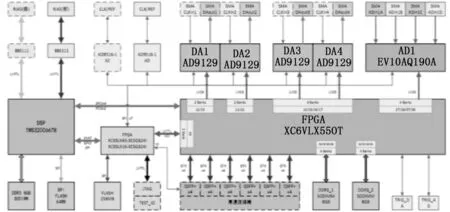

零值板主要由4片DAC、1片ADC、1片FPGA、1片DSP构成,其中DSP的片外集成了8GB-DDR3缓存,FPGA片外集成了16GB-DDR3缓存,以满足大容量高速率数据的处理要求,对外接口包括网口、高速接口,同时预留丰富的自定义接口,方便单板与其它CPCI设备进行互联通信,零值板硬件原理如图2所示。

图2 硬件原理框图

信号源可实现高带宽直接数字射频合成的输出要求,可直接输出1.57 GHz、1.26 GHz、1.19 GHz的射频信号,根据采样定理,DAC的最小重构速率是输出频率的2倍,即最小重构速率为3.14 GHz、2.52 GHz、2.38 GHz,因此要求DAC的重构速率最低为3.14 GHz。DAC模块设计基于ADI公司的AD9129芯片,利用每片AD9129实现一路DA通道,因此采用四片AD9129实现对外输出四路射频信号,该模块最高转换速率设计可达5.7 Gsps,内部同时集成混频器电路,能够完成1.4 GHz~4.2 GHz频段范围内信号的混频输出,模块外部设计滤波器完成镜频和杂散等寄生分量的抑制,DC~1.4 GHz以下频段信号可以直接在基带模式下输出。

ADC模块设计基于EV10AQ190A芯片,可实现最高到S频段射频信号的直接采样处理,这样可兼容现有全部导航频点信号的接收处理,可避免二次增加射频处理环节。ADC模块每个通道独立采集的四通道模式的采样频率最高1.25 GHz,4个通道合并一路完成4相采集的单通道模式的采样频率最高5 GHz,这样使得接收板可以完成高速数据采集,从而完成一定的信号质量分析功能。另外,ADC模块分辨率可达10 bit,可保证采集信号的动态范围和幅度分辨精度。模块内部继承了4个采集通道,这样利用一片ADC就可以完成B1/B2/B3/BS4个频点射频信号的采集处理工作,而不需要额外再考虑ADC器件间的同步等复杂问题,从而保证了零值标定精度。

零值板上的FPGA选用了XILINX公司V6系列的XC6VLX550T,选用V6系列器件基于两点:第一V6系列功耗较低,IO电压均为2.5V,相较于其它系列FPGA(IO电压为3.3 V),整体功耗节省约25%;第二,V6系列FPGA支持的外设接口更为丰富、接口带宽和速率更高,它支持DDR3和PCIE接口,使得它在更适用于高速信号交互应用场合。LX550T,内部逻辑资源高达5500万门,有效IO高达600个,片内集成了864个DSP48E硬核乘法器,完全满足导航信号基带处理的各种需求。此外单板上利用FPGA对外扩展了4组总带宽为20 Gb/s的光纤接口,便于单板与外部进行高速数据的交互需求。

零值板上的DSP则选用了TI公司现阶段推出的最高端处理器TMSC6678。该DSP内部集成了8个独立的CPU核,每个核最高工作时钟频率可达到1.25 GHz。该DSP的强大之处还体现在它对众多高速接口的支持上,包括DDR3、PCIE等众多高速数据总线都集成在内,同时还集成了众多的协处理器以满足图像、语音、超宽带通信等众多领域的使用要求。在我们的单板上,C6678主要用于与上位机之间的网口通信,同时它与FPGA之间互联了EMIF总线和SRIO接口,可以与FPGA配合共同完成高运算量、高吞吐量的算法应用。

2.2 时钟网络设计

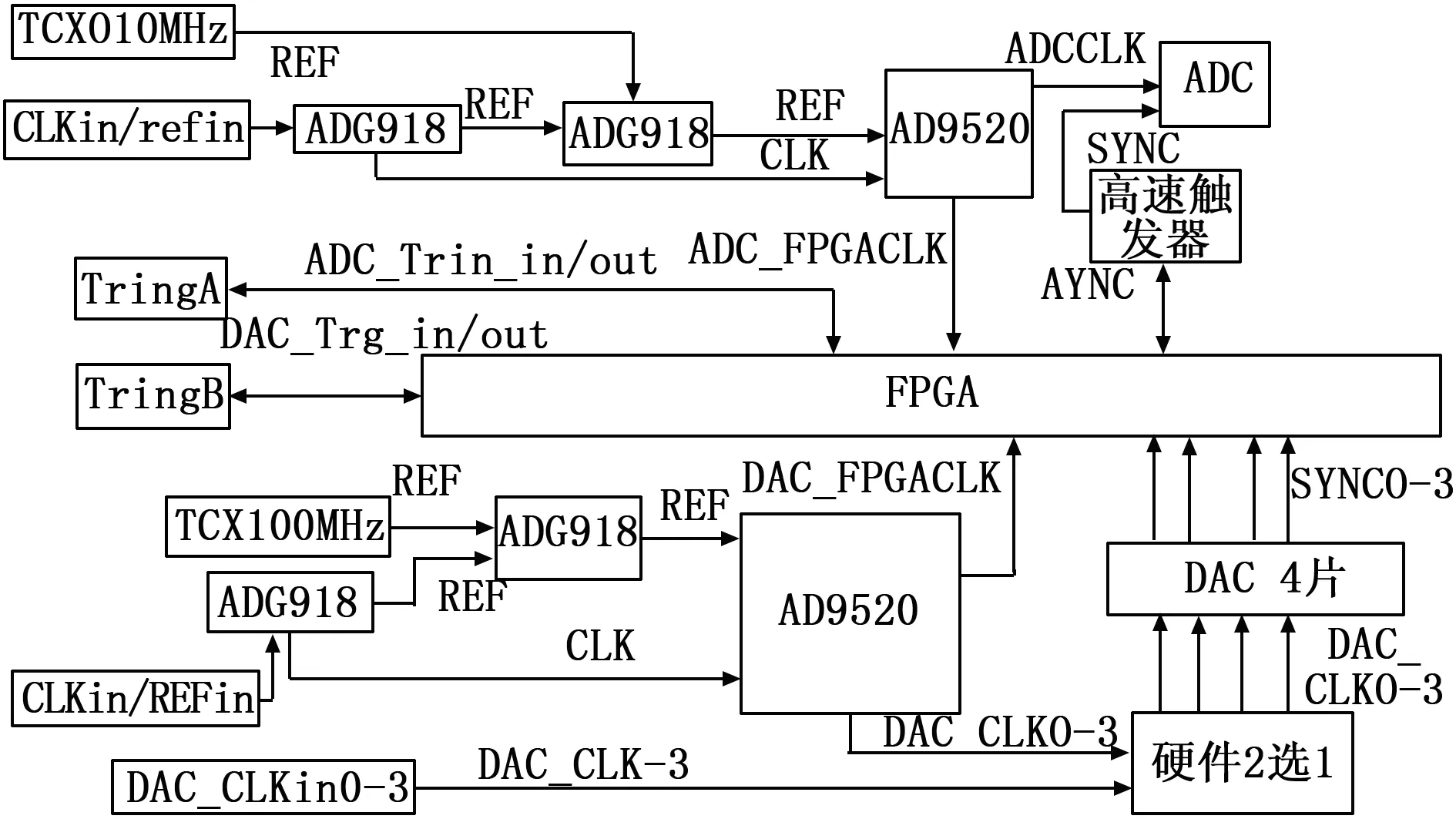

系统时钟设计的原则是兼顾使用方便、能够灵活改变单板工作时钟频率,且同时能够支持外源参考工作模式,从而满足同源工作的要求,单板时钟处理方案如图3所示。

图3 时钟产生及分配原理框图

由于AD9129的时钟最大为2.85 GHz,且零值板上有4片AD9129,这就要求时钟芯片最大输出时钟大于或等于2.85 GHz且具有输出路数大于4路的多路输出功能。因此,时钟模块设计基于ADI的AD9520时钟芯片,AD9520内部集成了PLL+VCO,VCO的工作频段为2.53 GHz~2.95 GHz,满足最高工作时钟的要求,模块可满足高速信号处理场合对时钟性能要求。

时钟模块支持内外时钟两种模式,在内时钟模式下,只需提供一个参考时钟,然后板上的AD9520则可以完成对参考时钟的锁相倍频,然后综合产生各种板上同步器件所需的工作时钟。在外时钟模式下,可以直接向单板提供所需的外部工作时钟,此时时钟模块就不能再启用内部的PLL和VCO,只能对外部输入的时钟进行分频和多路分配处理。对于发射链路时钟设计时还预留一种供钟模式,可以直接向单板中的DAC提供所需的外部工作时钟。在同步触发设计环节,充分考虑板内不同同步器件间、板间等各种涉及同步处理的地方,同时满足主动同步和被动同步两种方式。

AD9520包含了PLL电路并集成了一个2.53 GHz~2.95 GHz的片上VCO、1个参考时钟倍频器、1个参考时钟R分频器、1个整数N分频器、可调延迟线和均分为4组的12个LVPECL输出,这些配置是通过加载已预设值的寄存器来实现控制的。AD9520可选择内部VCO或者CLK作为要分配的时钟信号源进入信道分配器,所允许的进入信道分配的最大频率是1600MHz,所以较大频率的信号在进入信道分配之前必须设置信道分频器进行分频。参考时钟输入通过一个VCO分频器连接至时钟分配模块,VCO的分频值可设为2到6之间的任意整数;AD9520也可选择内部VCO或者CLK直接输出。

2.3 多片DAC模块同步设计

因为DAC模块会给系统带来流水线延迟差异,进而导致不同DAC的输出不对齐,并且每次上电的偏斜不一致,多片DAC同步是指多个DAC具有相同的时延,因此利用固定延迟可以实现多个DAC的同步。

首先,通过零值板上的时钟拓扑设计以保证4片AD9129在具有相同的时钟条件,零值板DAC的时钟拓扑结构如图4所示。在外时钟模式下,由外部提供一个1.4 G-2.5 G时钟接到AD9520的CLK输入端口上,通过AD9520扇出4路一样时钟分别供给4片AD9129作为工作时钟;再由AD9520输出一路时钟作为FPGA输入时钟,该时钟为AD9129工作时钟4分频;4片AD9129的随路时钟(DCI)及FRAME是由FPGA产生的。

图4 DAC的时钟拓扑结构

其次,消除由DAC芯片所带来延迟差异。引起延迟差异的原因有两方面:FIFO与内部时钟初始化相位不固定;首先,由DAC时钟衍生(分频)的内部时钟,这些时钟每次上电的偏斜不一致,即这些时钟的相位关系不固定,导致DAC每次上电后从FIFO输出到模拟输出的时间延迟不是固定的。其次,AD9129中的FIFO是一个多数据槽缓冲器,有助于将DCI时钟域的数据转交到DAC时钟域,FIFO写指针由DCI时钟衍生的内部时钟控制,FIFO读指针由DAC时钟衍生(分频)的内部时钟控制,FIFO复位操作将这两个指针分开,二者之间的偏移由FIFO相位偏移决定,FIFO相位偏移不固定,导致数字路径延时不一样。

模块同步设计中,利用各DAC的SYNC输出(通过设置寄存器0x1A的位4=1使能),通过调整内部延迟(每次写入寄存器0x1A的位7或位6,便递增或递减一个DACCLK周期),使SYNC信号相互对齐,可以将多个DAC内的DACCLK对齐到±1DACCLK周期范围内;然后复位各DAC的FIFO,确保实现正确同步。

2.4 直接数字射频信号发射设计

FPGA与DAC的高速并行数据交互是发射链路的重点,因为在并行I/O总线中,接口的数据对齐问题影响着与外部设备的有效通信,在数据速率超过1 Gb/s而且不再能够为保持信号同步提供可靠方法时,并行I/O电路达到了其物理极限。

采用基于AD9129的RF数模转换器模块设计来解决FPGA与DAC并行数据交互问题,AD9129的数据接口采用一个源同步、双通道数据接口,因此总线接口速度降至数据速率的1/2,DCI时钟工作速率为DCK时钟的1/4,这样每个通道数据的采样时钟频率可以降为DAC芯片时钟的1/4;其次,是FPGA内部逻辑无法正确工作在这么高的时钟下,但是它的接口交互速率完全可以达到高速交互的要求,而且它与DAC之间的接口都是LVDS电气特性,因此可以直接相连,在FPGA内部采用多通道合成的并串转换技术来解决。FPGA与DAC并行数据交互具体实现方式如图5所示。

图5 FPGA与DAC接口交互图

由于DAC需要输出1.57 GHz、1.26 GHz、1.19 GHz,2.492 GHz的射频信号,同时还需满足多路基带伪码相位相对一致性。这就需要选择一个统一的时钟作为4片DAC的工作时钟,同时DAC工作模式只能选择混频模式。

时钟频率的选择受限于DAC与时钟芯片的工作时钟范围:AD9129 DACCLK_x时钟输入范围:1.42 G~2.85 G;AD9520-0片内VCO的频率范围为:2.53 G~2.95 G,CLK输入范围为:0~2.4G,LVPECL时钟输出最大频率为2.4 G。为了保证时钟的性能,综合时钟芯片的时钟工作范围与DAC时钟工作范围,时钟频率范围设定为1.4 G-2.4 G。在混频模式下,产生各数据样本的互补样本并插入其后,使得它也能以相似方式更新DAC。使用混频模式时,器件以DAC采样速率对输出进行有效削波,其作用是降低基频信号的功率,同时提高以DAC采样速率为中心的镜像的功率,从而提高这些镜像的动态范围。

3 实验结果及分析

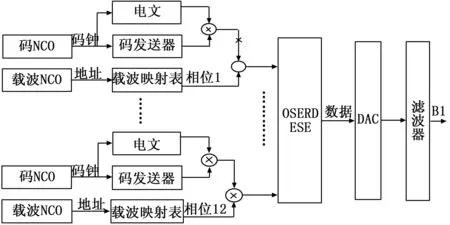

信号源主要功能是通过直接数字射频信号发射技术来产生下行B1、B2、B3的信号,以下行B1信号生成方式为例,其它频点信号类似,首先,配置合适的工作时钟,由AD9520分别给AD9129提供1718.64 MHz的工作时钟,给FPGA提供143.22 MHz的工作时钟;其次,使用多相技术在FPGA里产生中心频率为143.22 MHz的调制信号,输出给AD9129;最后,使用AD9129的混频模式,对143.22 MHz的调制信号与AD9129工作时钟进行混频,对AD9129输出信号进行滤波,只留下中心频率为1575.42 MHz的调制信号,信号生成如图6所示。

图6 B1信号生成框图

下行B2信号生成方式如下:首先,配置合适的工作时钟,由AD9520分别给AD9129提供1718.64 MHz的工作时钟,给FPGA提供143.22 MHz的工作时钟;其次,使用多相技术在FPGA里产生中心频率为526.845 MHz的调制信号,输出给AD9129;最后,使用AD9129的混频模式,对526.845 MHz的调制信号与AD9129工作时钟进行混频,对AD9129输出信号进行滤波,只留下中心频率为1191.795 MHz的调制信号。下行B3信号生成方式与B2基本相同,只是FPGA里产生中心频率不同,为450.12 MHz的调制信号,滤波器的频点不同。

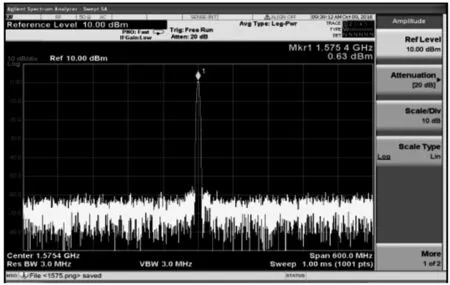

以DAC输出1.57 GHz为例,时钟为2265.48 M,DAC工作模式设置为混频模式,输出1575.42 M单载波,频谱如图7所示。

图7 1575.42 M单载波频谱

高性能的RF数模转换器与多相技术相结合,设置合理的时钟频率及RF数模转换器工作模式,可完成直接数字射频信号发射技术,输出所需频率。在混频模式下输出频率在Fs*0.75时幅频特性最佳,在混频模式下输出频率在Fs*0.45至Fs*1.1时,相对于满量程幅度有5db的衰减,满足信号的功率要求。通过上述对采样时钟的计算,满足DAC输出1.57 GHz、1.26 GHz、1.19 GHz,2.492 GHz射频信号的统一时钟范围为2265.48~2383.59 M。因此,信号源高性能的RF数模转换器与多相技术相结合,通过设置合理的时钟频率及RF数模转换器工作模式,可以完成直接数字射频信号发射技术,最终实现所需频率的信号输出。

4 结束语

本文基于FPGA和DSP处理器架构,设计了一种零值测试基带信号源。系统各模块充分考虑高速数据处理能力及宽温范围内的工作时延稳定性和一致性,系统可模拟并输出多路多制式的基带信号,兼备收发信号处理能力,可模拟下行B1、B2、B3信号以便系统进行零值自测,能够直接生成并输出L波段射频信号。该信号源已成功应用于北斗导航系统的研发过程中,系统的模块化设计及配置灵活等通用化设计,对导航领域信号源设计具有一定的借鉴意义。