宽带信号接收机中数字下变频的设计与FPGA实现∗

2019-05-07覃荣捷陆大海

覃荣捷 袁 晓 辛 超 陆大海

(1.四川大学电子信息学院 成都 610064)(2.西南电子电信研究所 上海 200434)

1 引言

随着通信技术的发展,软件无线电技术在军事和民用上都具有重要作用[1,9]。而宽带信号接收机就是针对宽带信号进行信号采集、处理与传输的一种基于软件无线电技术的设备。但是随着集成芯片的不断发展,ADC的采样速率越来越高,这对后续的数据处理、传输以及存储带来很大的压力,具有向下变频、滤波和降低采样速率等优点的数字下变频就显示了其重要作用,同时,它也是软件无线电技术中的关键技术之一。现有的数字下变频实现方法有通用DDC芯片、专用ASIC和FPGA等。而以FPGA实现的数字下变频是通过硬件描述来实现,具有灵活可配置、并行处理等特点,常常被作为首选实现方案[2]。本文根据宽带接收机的功能需求,设计一个针对数字中频的可灵活配置的DDC方案。

2 DDC的原理及其设计方案

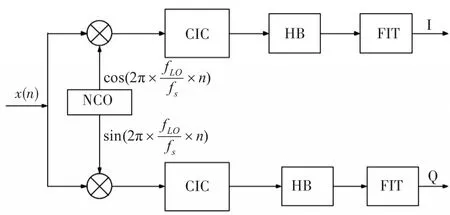

数字下变频主要包括数控振荡器NCO、混频器和滤波三个部分,其原理框图[3]如图1所示。DDC的工作原理过程为经过A/D转换后的数字高频信号x(n)进入DDC后,先与数控振荡器(NCO)产生的正交本振信号相乘,将数字高频信号下变频至特定频率。此时,混频得到的数据速率仍然和A/D采集的速率一致,都相对较高,对后级的数据传输和处理造成很大压力。因此,混频后的信号经过积分梳状(CIC)滤波器和半带(HB)滤波器进行抽取滤波,将数据速率快速下降。最后通过FIR滤波器进行整形滤波,输出I/Q两路基带信号。

图1 数字下变频的原理框图

根据某宽带接收机的功能需求,设计一个模拟中频输入为70MHz,采样频率为93.33MHz,数字中频带宽最大为20MHz的可配置的数字下变频器。在充分考虑DDC时效性和开发周期的基础上,数字下变频器中的大部分模块先通过Matlab进行仿真,并从Matlab中获取相应的参数,再利用这些参数进行IP核的配置,最后利用Verilog完成DDC的实现。

3 DDC的详细设计及其仿真

3.1 混频模块的设计

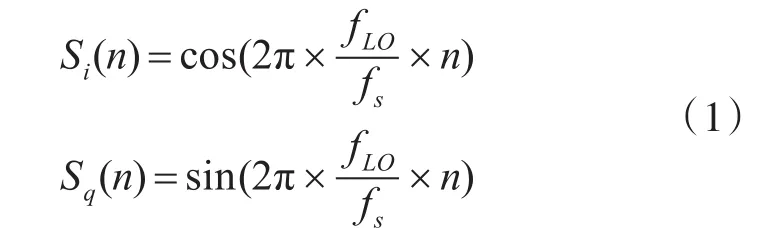

混频模块主要包括数控振荡器NCO和乘法器。其中,数控振荡器,作为DDC的核心部分,主要用来产生稳定的、正交的、频率可控的正弦和余弦信号,如式(1)所示。

式(1)中,fLO是数控振荡器的本地振荡频率,fs是ADC的采样频率。在FPGA中常用的数控振荡器可以采用查表法、DDS和CORDIC等方法。但无论采用哪种方法,都在一定程度上占用了FPGA的ROM资源或者DSP资源,而且提高调试的复杂度。因此,在本文中,提出了一种免混频方法,其原理是:在满足采样定理的前提下,本设计中采样频率为93.33MHz,中频频率为70MHz。ADC采样时钟会将70MHz的中频信号左右搬移93.33MHz的整数倍,即产生频率为(70±93.33N)的镜像,此时可选择其中任意一个镜像信号来完成解调。文中选择23.33MHz的镜像信号,即数控振荡器NCO产生的23.33MHz的正余弦信号与之相乘。由此可知,以式(1)中的为例,可写成:

从式(1)、式(2)可以看出,NCO的I路输出就分别为cos(O)、cos(π/2)、cos(π)、cos(3π/2),即1,0,-1,0四个特殊值,Q路输出为sin(0)、sin(π/2)、sin(π)、sin(3π/2),即0,1,0,-1四个值。这样混频器就可以避免复杂的振荡器和乘法器,而用简单的组合逻辑和取反电路即可实现,从而极大简化了硬件电路的实现。实现方法为:先将输人数据流每隔2个求其负数,即取2的补码,形成一个新的数据流,再将新数据流每隔一个置0,所得的输出数据流就是下变频后的基带I/Q数据。FPGA中观测混频之后的结果如图2所示。

3.2 CIC滤波器设计与Matlab仿真

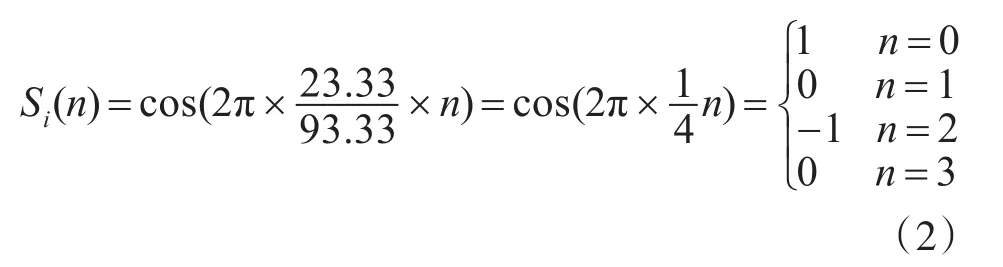

级联积分梳状滤波器(Cascade Integrator Comb,CIC),顾名思义是讲积分器和梳状滤波器级联而成,其原理结构框图如图3所示。从框图中可以看出,CIC滤波器前半部分是一个积分器,所做加法运算是在x(n)与反馈回路乘1之间。而后半部分是r阶的梳状滤波,所做加法运算是在x(dn)与其前馈回路乘-1所得之间。由于其系数均为1,运算只需要加法器而无须乘法器,在实际设计时无须对系数进行存储,从而在FPGA中实现时节省了存储空间和DSP资源。

图3 CIC滤波器原理结构框图

CIC滤波器的传递函数[4]为

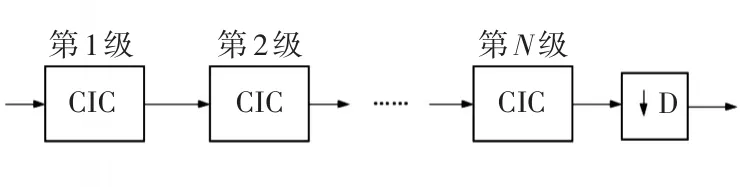

在抽取系统中,常以N级CIC级联使用,其结构如图4所示。

图N级级联结构图

N级CIC级联后的性能主要由旁瓣抑制AN、阻带衰减αN、带内幅值容差δN和带宽比例因子b等参数指标决定,它们与级数N,抽取因子r之间的关系如下:

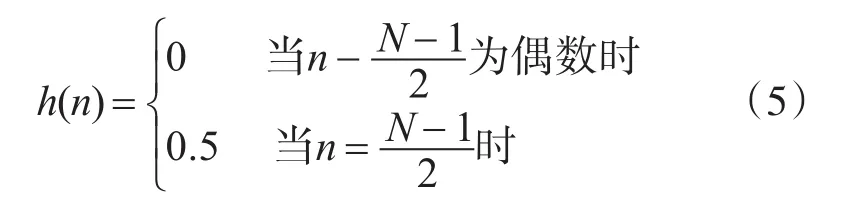

由上述公式可知,随着级数N的增大,滤波器的旁瓣抑制A和阻带衰减α都增大,同时带内幅值容差也增大,考虑到通带性能,通常选取N≤5[5]。在N不变的情况下,带宽比例因子b越小,CIC滤波器的通带和阻带特性也就越好。根据设计要求,CIC的级数为3,抽取因子为4~1024可变。在Matlab和FPGA中可得到其幅频响应如图5所示。

图滤波器的幅频响应

3.3 半带滤波器设计

半带滤波器是一种特殊的FIR滤波器,它的具体两个显著的特性。

1)其通带宽度与阻带宽度相同,并且它的通带容限与阻带容限也相同,也就是说,通带与阻带是关于π/4对称的,这也是半带滤波器这个名字的由来。

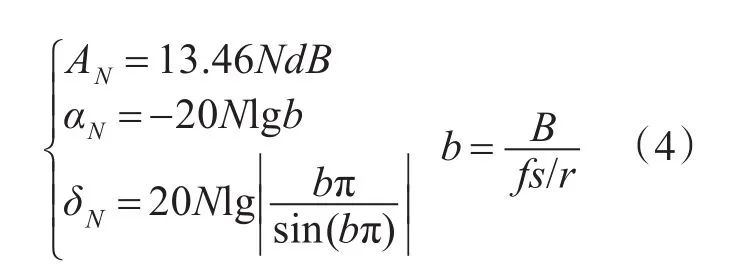

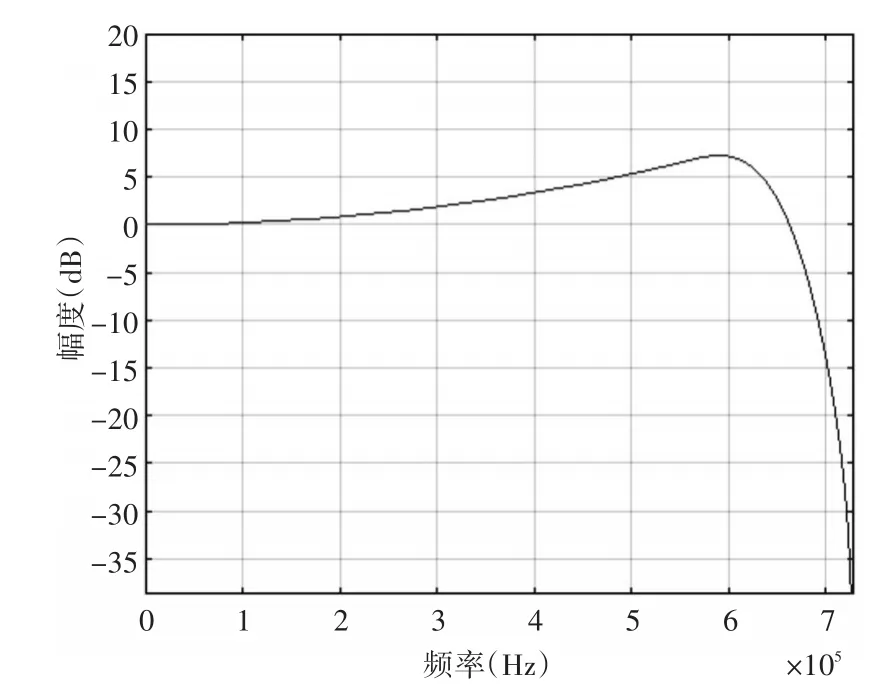

2)半带滤波器的单位冲击响应为

式(5)中,N为滤波器的长度,且必须为奇数。从式(5)中可以看出:除零点外,其他偶数序号的单位脉冲响应为0,所以半带滤波器的系数有一部分是0。因此,在进行卷积运算的时候也就省去了部分乘法运算和加法运算,这就使得半带滤波器的运行速度大幅度提升,占用的硬件资源大幅度减小。所设计的半带滤波器的幅频响应如图6所示。

图6 半带滤波器的幅频响应

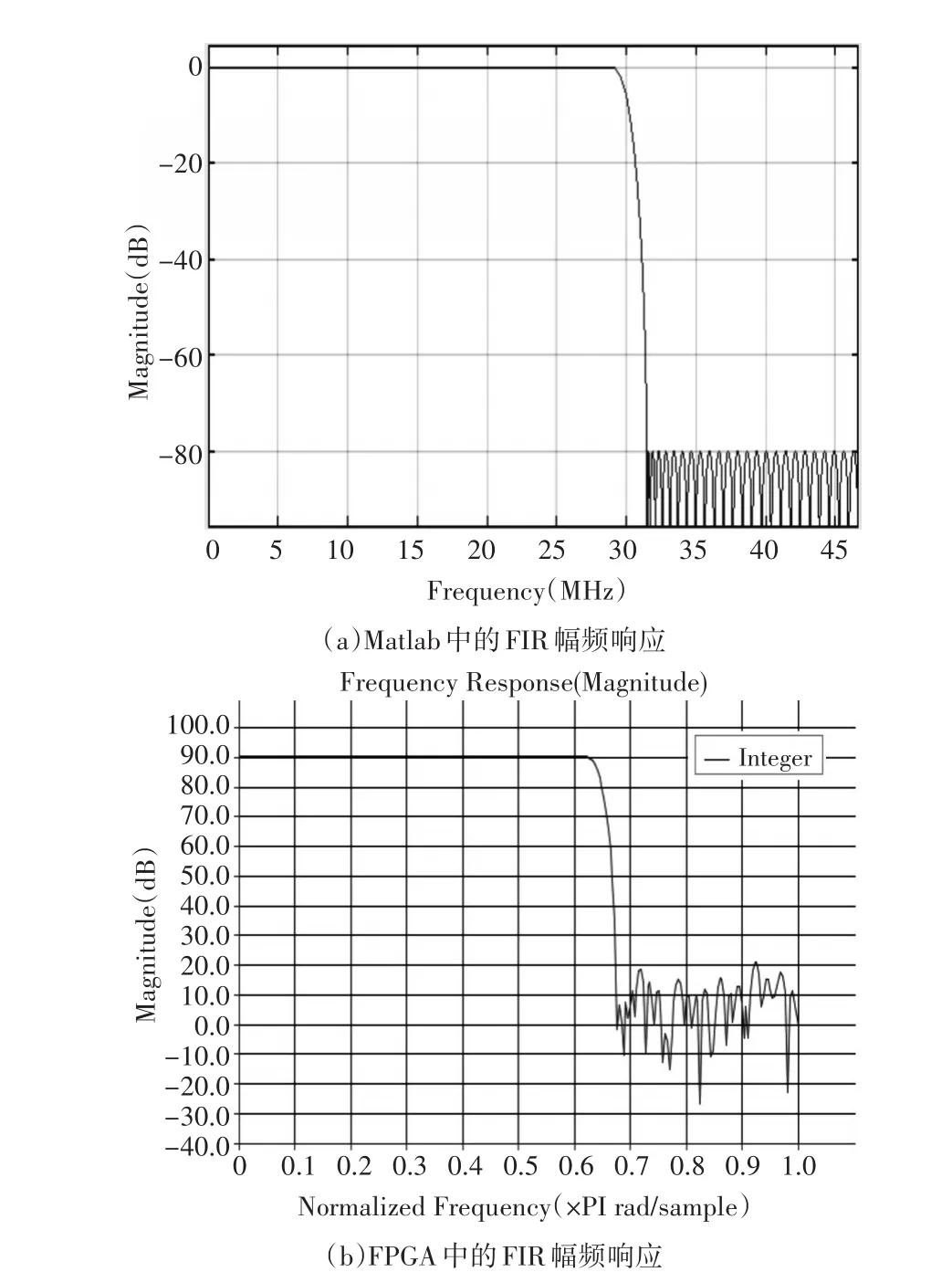

3.4 FIR滤波器设计

FIR滤波器,顾名思义,其冲击响应由有限个采样值构成[12]。在DDC中,HB滤波器后面需要增加一个FIR低通滤波器对数据进行整形滤波。由于信号经过CIC抽取之后速率变低,为了减少过渡带宽,提高滤波器性能,通常通过提高FIR的阶数来实现,即增大N。本文是通过Matlab FDATool设计FIR滤波器,并将设计好的FIR系数量化成定点后导出至FPGA中,可以看出在两个环境下的幅频响应如图7所示。该滤波器阶数为128,阻带衰减为80dB,通带宽度为30MHz。

4 DDC的FPGA实现

选用Xilinx公司的7系列XZ7Z100ffg-2作为目标器件,利用Verilog语言,在vivado软件平台下进行DDC的实现,RTL框图如图8所示。

图7 FIR滤波器的幅频响应

图8 DDC的RTL原理图

系统验证对频率为1MHz信号的数字下变频,本文设计采用的系统时钟为93.33MHz,中频频率为70MHz,用系统时钟对中频信号进行采样,由带通采样定理可知,在23.33MHz处会出现基带信号的镜像信号。系统输入97MHz正弦信号,经过采样后镜像信号出现在24.33MHz处,通过混频和抽取滤波后应该在1MHz的信号不被滤掉。具体做法是利用ILA进行数据监测,同时保存所监测的数据,最后对所保存的数据进行Matlab分析验证。图9和图10分别以数据和波形的方式呈现DDC以4倍抽取输入信号的结果。图11则以ILA中的有效数据进行时域图和频谱图结果。结合图9、图10、图11可以看出,DDC最后输出的波形就是1MHz正弦信号,与理论分析相吻合。

图9 DDC调试结果的数据显示

图10 DDC调试结果的波形显示

图11 DDC的数据在Matlab中时域图和频谱图

5 结语

综上所述,本文设计的DDC对输入的中频信号,很好地完成了抽取降速、整形输出的过程,为后续的数据处理提供可靠的数据源。同时DDC的抽取因子是可以灵活配置的,可根据系统要求进行改变。该设计大部分模块的实现采用了Xilinx IP核,简化了设计流程和缩短开发时间,从最后的结果可以看出本设计是正确可行的,而且已被成功地运用到某便携式宽带接受机设备中,对无线电监测等设备的研制具有一定的参考意义。